Enhanced Versatile Analog-to-Digital Converter (EVADC)

The EVADC provides a series of analog input channels connected to several clusters of analog/digital converters using the successive approximation register (SAR) principle to convert analog input values (voltages) to discrete digital values.

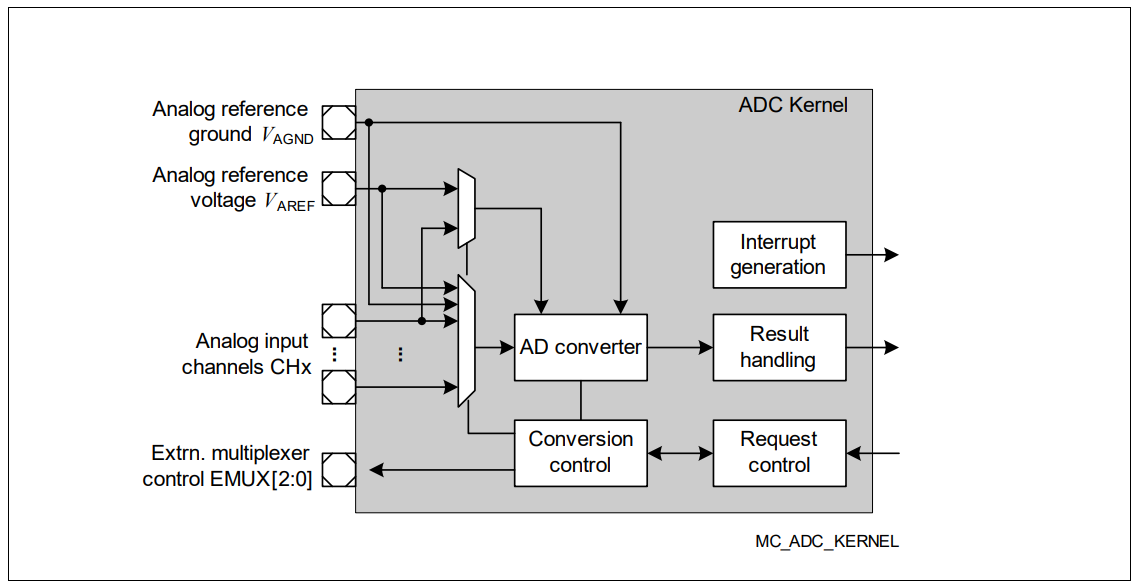

The EVADC is based on SAR converters, each comprising a sample&hold unit and a converter block. An analog multiplexer selects one of several input channels and a dedicated control logic with several request sources defines the sequence of consecutive conversions. This altogether builds a conversion group. The number of analog input channels and conversion groups depends on the chosen product type.

Each converter of the ADC clusters can operate independently of the others. The results of each channel can be stored in dedicated channel-specific result registers or in a group-specific result register.

Three clusters with different functionality are available:

- Primary converter cluster: Equipped with 8:1 multiplexers and 8-stage queues, conversion time down to below 0.5 µs

- Secondary converter cluster: Equipped with 16:1 multiplexers and 16-stage queues, conversion time down to below 1 µs

- Fast compare cluster: Single channels, update rate down to below 0.2 µs

In addition to the EVADC also the EDSADC (Enhanced Delta-Sigma Analog to Digital Converter) performs analog-digital conversions.

Feature list

The following features describe the functionality of the ADC clusters:

- Nominal analog supply voltage 5.0 V or 3.3 V

- Input voltage range from 0 V up to analog supply voltage

- Standard (VAREF) and alternate (CH0) reference voltage source selectable for each channel to support ratiometric measurements and different signal scales

- Several independent converters with up to 8/16 analog input channels each

- External analog multiplexer control, including adjusted sample time and scan support

- Conversion speed and sample time adjustable to adapt to sensors and reference

- Conversion time below 0.5 µs for primary channels (depending on sample time)

Flexible source selection and arbitration

- Programmable arbitrary conversion sequence (single or repeated)

- Request source chaining to generate extended conversion sequences

- Conversions triggered by software, timer events, or external events

- Cancel-inject-restart mode for reduced conversion delay on priority channels

Powerful result handling

- Independent result registers

- Configurable limit checking against programmable border values

- Storage of maximum/minimum value

- Data rate reduction through adding a selectable number of conversion results

- FIR/IIR filter with selectable coefficients

Fast Compare Channels with above 5 M samples

- Automatic handling of flags and output signals

- Compare value adjustable via software, via conversion channel or via ramp

- Flexible service request generation based on selectable events

Built-in safety features

- Configurable register access protection supports safety applications

- Broken wire detection

- Multiplexer test mode to verify signal path integrity

- Automatic execution of test sequences

- Support of suspend and power saving modes

Functional description

The Enhanced Versatile Analog to digital converter module (EVADC) comprises a set of converter blocks that can be operated either independently from each other, sequentially chained for longer conversion sequences, or synchronized for parallel conversion of up to 4 channels. Each converter block is equipped with a dedicated input multiplexer and dedicated request sources (except for fast compare channels), which together build separate groups, each assigned to a kernel.

Primary groups provide 8:1 input multiplexers and deliver the minimum conversion time of approx. 0.5 µs. Secondary groups provide 16:1 input multiplexers and require a higher sample time leading to an increased conversion time. Fast compare channels provide one dedicated input channel each and deliver a compare time of approx. 200 ns.

This basic structure supports application-oriented programming and operating while still providing general access to all resources. The almost identical converter groups allow a flexible assignment of functions to channels. A set of functional units can be configured according to the requirements of a given application. These units build a path from the input signals to the digital results. Each kernel provides a dedicated Sample&Hold unit connected to the input multiplexer and to the converter itself.

Configuration of general functions

Several parameters can be configured individually for each channel, source, or group, or are valid for all ADC clusters. These parameters adapt the functionality of the EVADC to the requirements of the actual application.