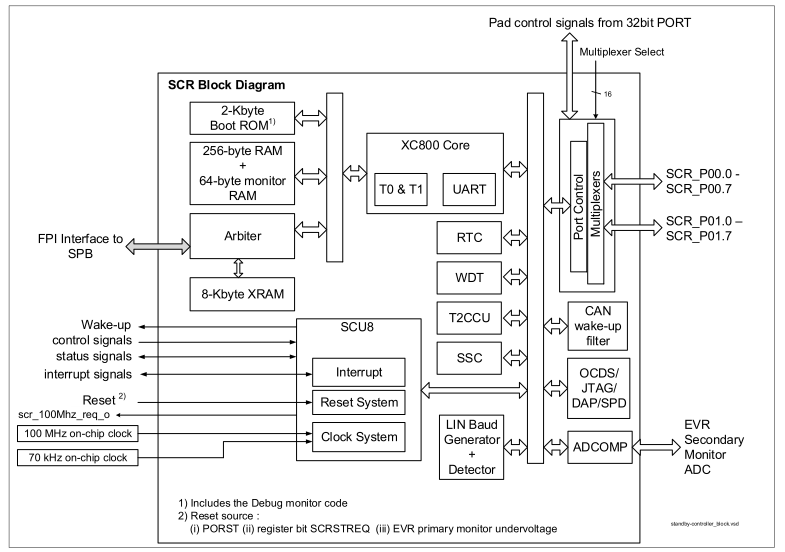

Standby Controller (SCR)

The SCR is an 8-bit microcontroller that continues to run while the main SoC is in the STANDBY state. It is based on the XC800 core that is compatible with the industry standard 8051 processor. There is an embedded 32 kB XRAM for program code and data.

Feature list

The following list summarizes the main features of the SCR:

High performance XC800 core

- Compatible to standard 8051 core

- Two clocks per CPU cycle architecture (for memory access without wait state)

- Two data pointers

- Maximum 20 MHz of core frequency

On-chip memory

- 2-Kbyte Boot ROM for startup firmware

- 256-byte RAM; plus 64-byte Monitor RAM

- 8-Kbyte XRAM for program code and data; accessible by CPUx via the main SPB bus

Power saving modes

- Idle mode

- Clock gating control to each peripheral

Watchdog Timer (WDT) with programmable window feature for refresh operation and warning prior to overflow

Two general purpose I/O ports able to control the shared pins in SCR Ports P00 and P01 (P33 and P34 of TriCore™)

Three 16-bit timers - Timer 0, Timer 1, Timer 2 of T2CCU

Capture/compare unit of T2CCU for digital signal generation

Real-time clock with on-chip oscillator to support periodic wake-up in standby mode

Full duplex serial interface (UART)

Synchronous serial channel (SSC)

ADCOMP unit which provides ADC compare functionality

- Interrupt supported from SCR to TriCore™ and vice versa

- XRAM Programmable via the System Peripheral Bus

On-chip Debug Support via single pin DAP interface (SPD)

- 1.5-Kbyte monitor ROM (part of the Boot ROM)

- 64-byte monitor RAM

Functional description

Key features include two instances of a 16-bit general purpose timer with a capture/compare unit (T2CCU) for digital signal generation such as pulse generation, pulse width modulation, and pulse width measuring. A Real Time Clock (RTC) supports periodic wake-up in standby mode. The On-Chip Debug Support (OCDS) unit supports software development and debugging of XC800-based systems. Local Interconnect Network (LIN) applications are supported through extended UART features and the provision of LIN low level drivers for the AURIX™ TC3xx Platform. For low power applications, various power saving techniques are available for selection by the user. Control of the numerous on-chip peripheral functionalities is achieved by extending the Special Function Register (SFR) address range with an intelligent paging mechanism optimized for interrupt handling.