AURIX™ TC3xx tools and software

The following section describes the functionality of the AURIX™ TC3xx platform firmware:

Startup Software (SSW) including support for:

Software modules implementing additional functions:

Startup Software

The Startup Software is the first software executed after a chip reset.

Software over the Air (SOTA)

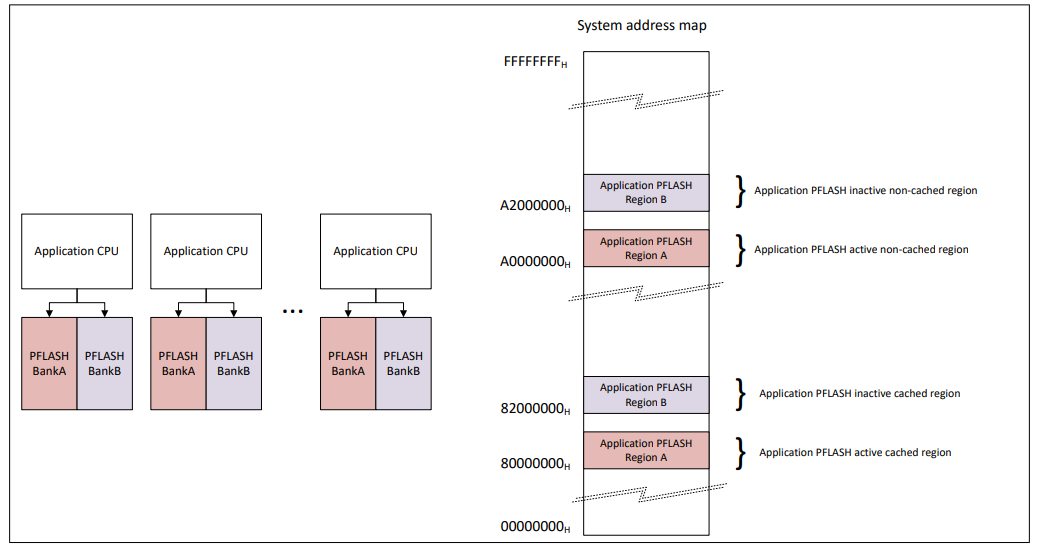

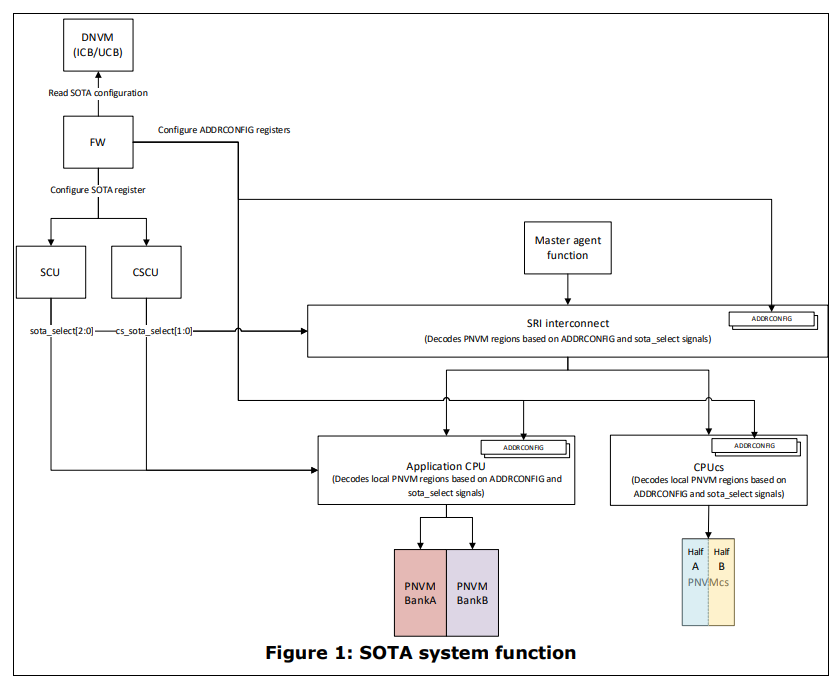

TC375 device has the ability to receive Software updates Over the Air (SOTA) by a function to split the PFLASH into two groups of banks, A and B. When SOTA is enabled, one of these groups of banks can be read and executed from, while the other group can have new code written to it. Thus, though simultaneous read-while-write (RWW) capability is not supported within a single physical PFLASH bank, SOTA is supported by a function to safely and securely perform write and erase operations to the unused group of banks.

Functional description

When SOTA is enabled, a group of PFLASH banks will be mapped to CPU executable address space (defined as ‘active’ banks) and the other group will be mapped to a set of addresses that allows them to be read and written to (defined as ‘inactive’ banks). When a SOTA update is completed, and the banks are swapped around, only the address mapping will change. This means that no data needs to be copied and the address ranges being executed from are always the same. When a SOTA address map switch from standard address map is performed, the mapping of the PFLASH banks for read/code execution has to be considered. All NVM operations are performed via the DMU function using the physical system address of the PFLASH, i.e., an NVM operation always uses the standard address map regardless of swap settings. ‘NVM operation’ is a term used for any command sequence such as a program, erase etc. targeting a FLASH and does not include reads.

The parameters that control SOTA address map switching and related functions are pre-configured in a user configuration block (UCB) and the hardware configuration is only updated by on-chip system firmware during the subsequent System Reset. This prevents unintentional changes during application execution. On some product variants, a 1MB block will be swapped with a 3MB block. Because the code image must be able to fit in either group A or B, the upper 2MB of the 3MB block cannot be used for program code.

Performance considerations

The CPU access to its local Program Flash bank is optimized for maximum performance. This can thus cause a performance variation when executing from different physical PFLASH banks. In order mitigate this, when SOTA is enabled, CPU fast path to local PFlash must be disabled. This will cause some drop-in performance but will ensure identical system performance when executing from either group of banks. If exact performance parity between each group is required, prefetch access should be disabled completely. If, however, only approximate parity is required, one of the four user-assignable prefetch buffers should be assigned to each non-local CPU. The first prefetch buffer is permanently assigned to the local CPU.

Checker Software

The Checker Software (CHSW) is intended to evaluate whether the device configuration and preparation for user code execution. In particular, the aspects considered as safety relevant are correct after completion of the Start-up Software.

Bootstrap Loaders

Bootstrap Loader routines provide mechanisms to load a user program via the selected interface by moving code into the Program Scratchpad RAM of CPU0 (CPU0_PSPR). The loaded code is started after exiting the BootROM.

Shutdown request handler

All active CPUs in AURIX™ TC3xx Platform jump unconditionally to the entry point of this handler upon any warm reset request.

Power supply friendly debug monitor

The AURIX™ TC3xx Platform BootROM contains a routine called Power Supply Friendly Debug Monitor (PSFDM). The purpose of this routine is to minimize the risk of getting EVR voltage over-/undershoot due to a sudden current drop when more than one CPU is halted by On-Chip Debug Support (OCDS), and to avoid a current peak when the CPUs are released from halt.

Registers

AURIX™ TC3xx Platform contains several registers exclusively dedicated to usage by Firmware. These registers provide users with information about the results from start-up mode evaluation done by SSW.