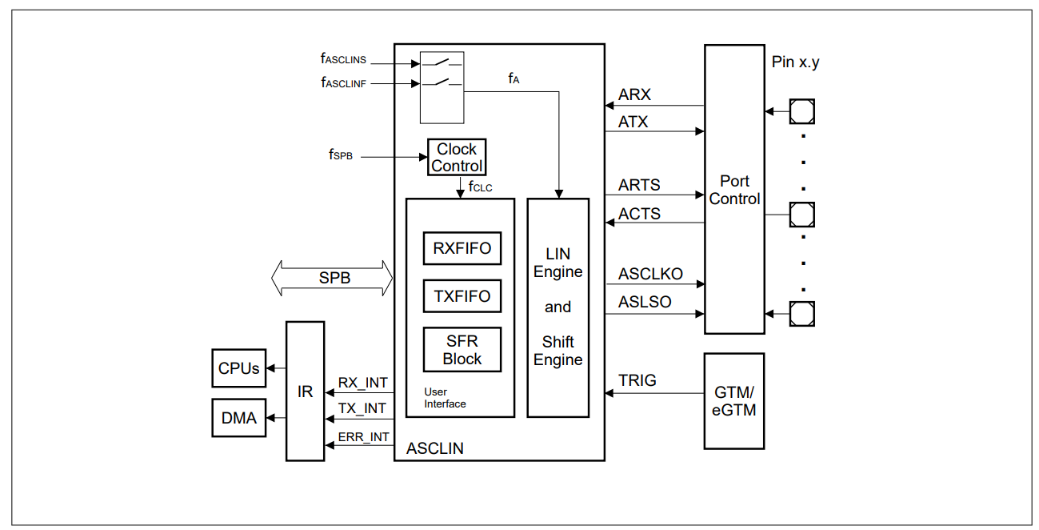

Asynchronous/Synchronous Interface (ASCLIN)

Feature list

General features

Transmit ASC, LIN, and SPI frames to external devices and handle all protocol relevant topics

- Receive ASC, LIN, and SPI frames from external devices and handle all protocol relevant topics

Data storage of 16-bytes TxFIFO (Transmit first in first out) and 16-bytes RxFIFO (Receive first in first out)

- Pack and unpack capabilities of the TxFIFO and RxFIFO

Interrupt generation:

- On a configurable TxFIFO level

- On a configurable RxFIFO level

- On an error condition (frame, parity, overrun error)

- On various internal events (end of ASC or SPI frame, or LIN events)

- Interrupt signals capable of triggering either a CPU or a DMA

Flexible functional configuration for software:

- Programmable oversampling of 4 to 16 times per bit

- Programmable sampling point position

- Programmable digital glitch filter and median filter for incoming bit stream

Shift direction LSB first for LIN mode and programmable LSB or MSB first for SPI and ASC mode

- Internal loop-back mode

Standard ASC features

Full-duplex asynchronous operating mode:

- 7-bit, 8-bit, or 9-bit (or up to 16-bit) data frames, LSB first

- Parity-bit generation and checking

- One or two stop bits

- Maximum baud rate fA/16 (6.25 MBaud at 100 MHz fA module clock)

- Minimum baud rate fA/268 435 456 (0.37 Baud at 100 MHz fA module clock)

- Frame transmit on hardware or software trigger

- Circular buffer

Extended ASC features

- Programmable oversampling of 4 to 16 times per bit:

- Optional RTS/CTS handshaking

LIN features

Support of:

- LIN version 1.3, 2.0, 2.1, and 2.2

- J2602

- Break detection

- Break injection

- Sync field generation

- Auto baud detection based on Sync Field measurement

- Collision detection optionally (LIN2.1 mandatory)

LIN Watchdogs:

- Header time-out

- Frame or Response time-out

- Stuck at zero or one monitoring

- Bus idle time monitoring

- Energy saving features (Wake-Up, Sleep)

Minimum CPU load in master mode:

- Single interrupt indicating the end of the frame

Minimum CPU load in slave mode:

- Single interrupt at the end of the header reception

- Single interrupt at the end of the response or end of frame

- Standard operation with one interrupt per transmitted or received byte supported

SPI features

SPI master modes (slave mode not supported):

- Four-wire or three-wire (with or without slave select output signal)

- Up to 32-bit data width

Full-duplex and half-duplex:

- Maximum baud rate fA/4 (= 25 MBaud at 100 MHz fA module clock)

- Minimum baud rate fA/268 435 456 (= 0.37 Baud at 100 MHz fA module clock)

- Programmable leading and trailing delays

Functional description

The main purpose of the ASCLIN module is to provide asynchronous serial communication with external devices using only data-in, data-out signals. The focus of the module is set to fast and flexible communication: either fast point-to-point or master-to-many slaves communication using the LIN protocol. Additionally, the module supports the synchronous SPI communication.

The Shift Engine is responsible for frame transmission and reception, depending on the configured settings. For LIN communication the LIN Engine controls frame transmission and reception according to the protocol specification. This block runs on asynchronous clock. The User Interface block is for configuration of protocol settings as well as the RxFIFO and TxFIFO and their management. The user can access the FIFOs using the registers. This block runs on synchronous clock.