Camera and ADC Interface (CIF)

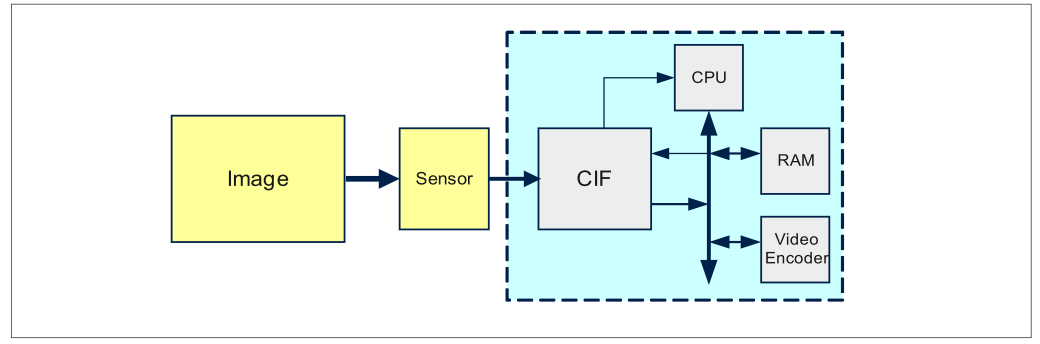

The camera and ADC interface module (CIF) provides a 16-bit wide parallel read interface that can be used to connect camera sensors and external analog to digital converters (ADCs). The following section provides an overview of the architecture of the CIF module and its applications. The camera and ADC interface (CIF) is a complete video and still image input interface that transfers data from an image sensor into EMEM. In addition, there are several hardware blocks that perform image-processing operations on the incoming data.

Feature list

The following list summarizes the CIF features:

Throughput up to 96 MPixel/s

32-bit BBB slave programming interface

BBB master interface

ITU-R BT 601 compliant video interface supporting YCbCr and RAW data transfer

ITU-R BT 656 compliant video interface supporting YCbCr and RAW data transfer

Non-line/frame aligned data transfer (data mode)

16-bit parallel camera and ADC interface

YCbCr 4:2:2 processing

The hardware JPEG encoder supports images with a horizontal resolution of up to 1280 pixels. It includes a JFIF 1.02 stream generator, as well as programmable quantization and Huffman tables

Windowing and frame synchronization

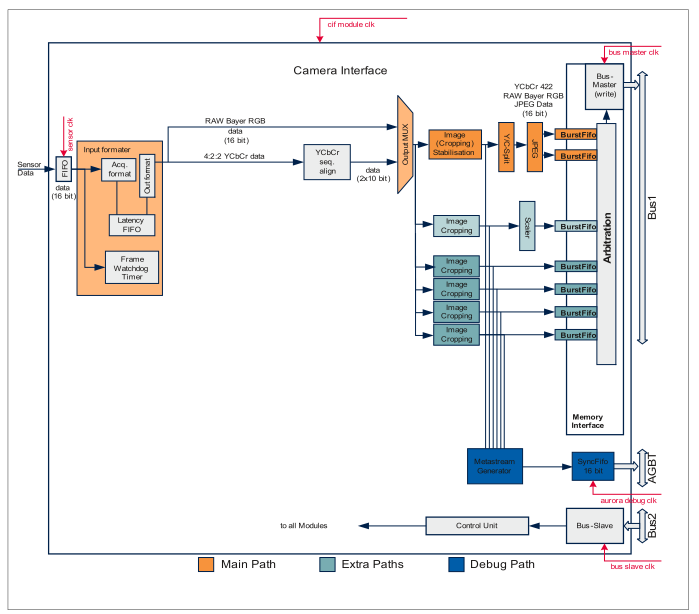

One main and five extra image cropping units allowing parallel transfer and position adjustment of up to six subregions

The path from the main image stabilization or from one extra image cropping unit to the AGBT debug interface is established. This path includes a meta-symbol generation unit, which inserts frame start and timing information into the stream, ensuring accurate data handling and processing

Programmable watchdog timer to detect abortion/breaks in frame transmission

Linear downscaling for the first extra path, supporting a mode for RGB Bayer pattern

Frame skip support for video (for example, MPEG-4) encoding

Macro block line, frame end, capture error, data loss interrupts, and synchronization interrupts

Programmable polarity for synchronization signals

Luminance/chrominance and chrominance blue/red swapping for YCbCr input signals

Maximum input resolution of 4095x4095 pixels

Buffer in EMEM organized as a ring-buffer, supporting up to 2x8 beat bursts (2x32 bytes)

Buffer overflow protection for RAW data transfer and JPEG files

Asynchronous reset input, software reset for the entire IP

Support of planar, semi-planar, and interleaved storage format (main path)

Power management by software-controlled clock disabling of currently not needed submodules

Functional description

Apart from providing the physical interfacing to various types of camera sensor modules, the CIF block implements image processing and encoding functionality. The integrated image-processing unit supports image sensors with integrated YCbCr processing. The CIF also supports the transfer of RAW (for example, Bayer pattern) images and non-frame synchronized data packets. The CIF block features a 16-bit parallel interface. All output data is transmitted via the memory interface to a BBB system using the master interface. Programming of the CIF is done by registering read/write transactions using a BBB slave interface.

Figure 1. Camera and ADC interface (CIF) block diagram

The BBB interface is divided into a master and a slave interface with their own clock domains. These clock domains may be asynchronous to the CIF module clock. To avoid data loss the frequency of the BBB clocks needs to fulfill the following requirements:

BBB interface master clock (DMA) >= CIF module clock

BBB interface master clock (DMA) <= 2 * CIF module clock

CIF module clock >= Pixel clock (PCLK)

The CIF is targeted on various applications requiring a mega pixel still image and/or video input (for example: mobile devices, automotive or industrial vision, …).

Figure 2. Target application example

The CIF provides a sensor/camera interface for a wide variety of video applications and is optimized for high-speed data transmission under terms of low power consumption.

The module is designed for the following use cases:

Video capturing/encoding

Still image capturing in YCbCr with on-the-fly JPEG encoding

RAW frame data capturing

Simple non-line/frame aligned data reception (data mode) used, for example, for connecting to external ADCs

The CIF requires fast system memory for image storage in either planar/semi-planar/interleaved YCbCr or RAW planar format or as JPEG compressed data. The integrated JPEG encoding engine is able to generate a full JFIF 1.02 compliant JPEG file that can be displayed directly by any image viewer. YCbCr formats - which are used for video compression (for example, MPEG4) for instance - are supported. For on-the-fly encoding, macro block line interrupts are generated to trigger video encoding.

The CIF provides a parallel interface that can be used to connect external ADC converters. To connect to one or more external ADCs, the CIF module requires a timer module capable of generating the appropriate clock and select signals, like the generic timer module (GTM). Connecting multiple ADCs to the CIF module may require an external multiplexer, and additional control signals to control it. Using twin or quad ADCs avoids the need for an external multiplexer.

The CIF forms a complete video and still picture input interface solution for SoCs for various applications. It is widely programmable and therefore very flexible to use. It supports input frame resolutions up to 4095x4095 pixels. It comprises a video image signal processing unit (ISP), security watchdog unit, Y/C splitter, downscaling unit, cropping units, debug path, JPEG encoder, output unit, Ctrl unit, and BBB slave interface for programming. All data transfer between EMEM and CIF is handled via the memory interface block.