PSOC™ Control C3 - PSC3P5xD, PSC3M5xD

Arm®

Cortex®-M33 32-bit MCU+FPU+DSP, 180 MHz,

up to 256 KB Flash/64 KB SRAM, Real-time Control

PSOC™ Control package image

Features

High-performance, low-power 32-bit single-core Arm® Cortex® M33-based microcontroller with digital signal processor (DSP), floating-point unit (FPU), and state-of-the-art security features

High-performance, programmable analog subsystem (HPPASS):

12-bit,12-MspsSAR ADC with parallel idle sampling of up to 16 analog channels

Five comparators with <10 ns built-in 10-bit DAC and slope generator

Real-time control peripherals:

Coordinate rotation digital computer (CORDIC)

16 x 16-bit and 4 x 32 bit timer/counter pulse-width modulator (TCPWM) supporting <80 ps high-resolution pulse-width modulator (HRPWM)

Enhanced routing flexibility with a combinatorial trigger multiplexing unit

Communication interfaces: Up to six SCB and two CAN FD (one supporting 8 Mbps)

256 KB read-while-write flash with ECC support

Low-power operation modes down to 300 nA: Sleep, Deep Sleep (three modes) and Hibernate

Up to 50 GPIOs with programmable drive modes, strengths, and slew rates; up to 28 pins support Smart I/O programmable logic and up to 16 dedicated analog pins

Security: PSA L2 certified; configurable flash partitioning and protection

Safety: Class B and SIL 2 compliant safety test libraries are available

Power supply range: 1.71 V to 3.6 V

Ambient temperature range: -40°C to 105°C Ta

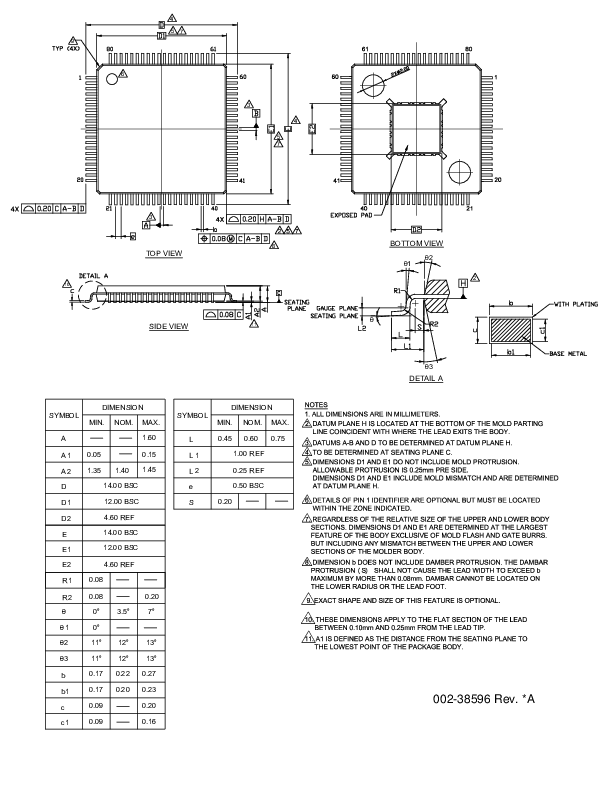

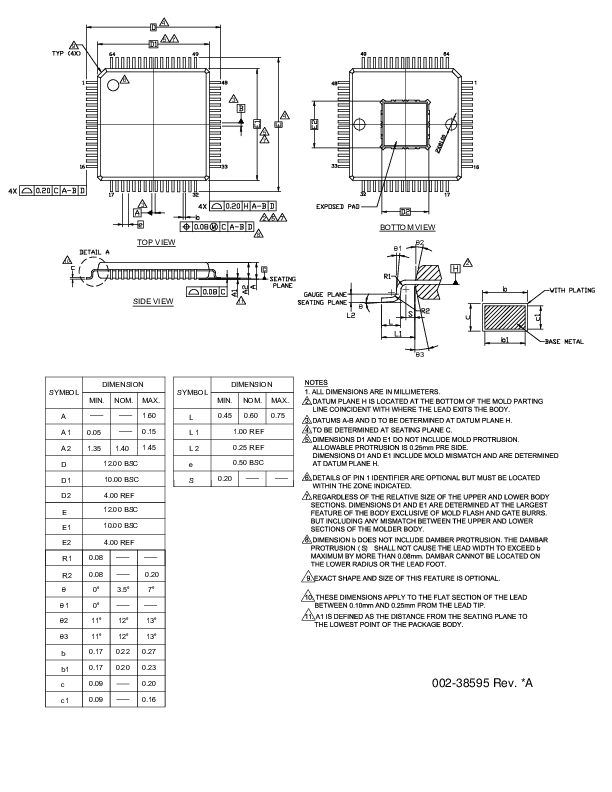

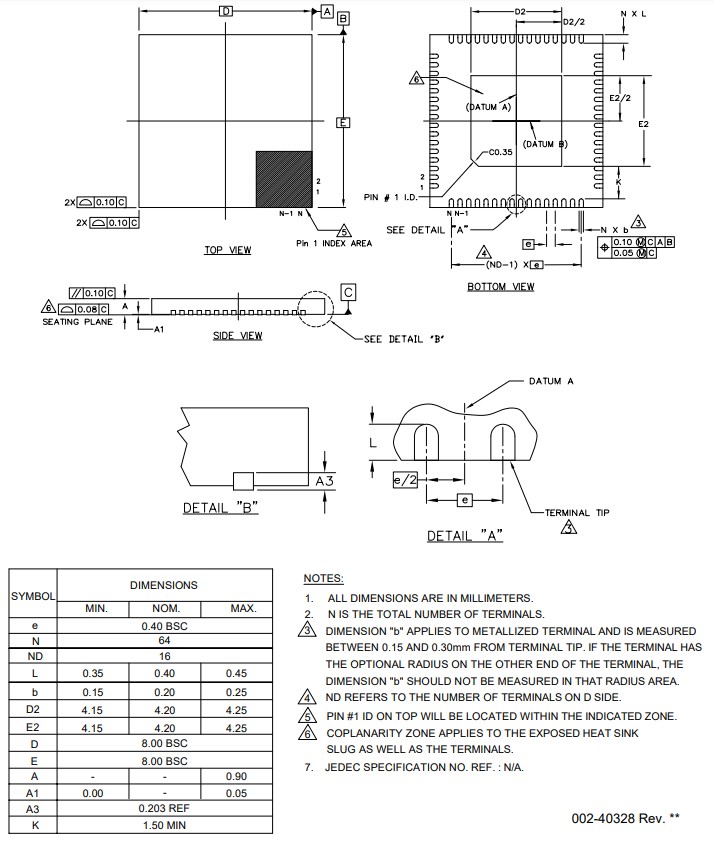

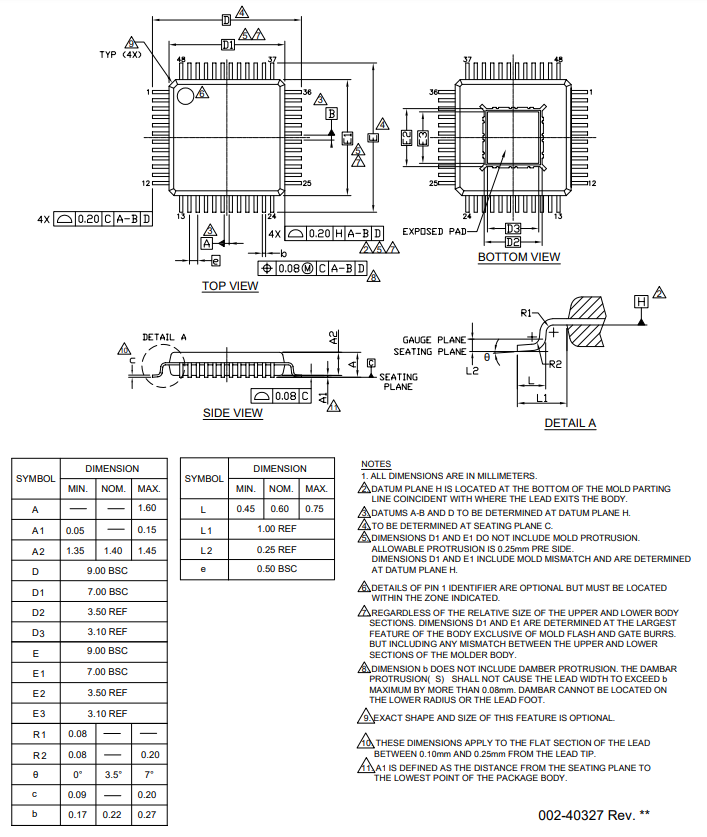

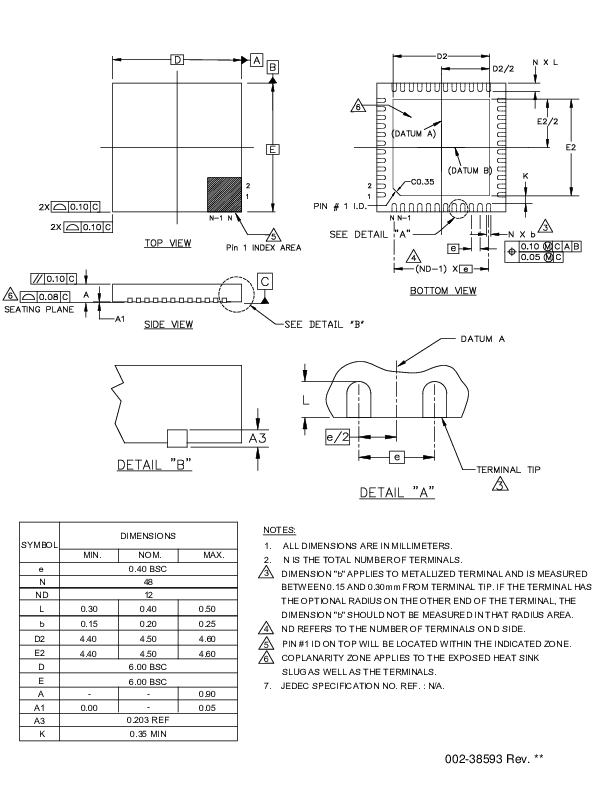

Packages: VQFN-48, E-LQFP-48, VQFN-64, E-LQFP-64 , E-LQFP-80

Potential applications

Motor control in power tools, home appliances, industrial drives, light electric vehicles, robotics, and drones

Digital power control in switched mode power supply (SMPS) and PFC applications for LED lighting, EV chargers, solar inverters, servers, and PC power supplies

Wide bandgap technologies (e.g., SiC and GaN) based motor control and power conversion applications

Description

The

PSC3P5xD

and

PSC3M5xD

devices are based on the Arm® Cortex®-M33 running up to

180 MHz

with DSP and FPU capability. In addition to the CPU subsystem, the devices contain advanced real-time control peripherals, such as high-performance programmable analog subsystem, comparators, advanced timers with high-resolution capability, up to six SCBs and two CAN FDs for communication. The devices support one Active and five low-power modes for managing and reducing the power consumption depending on application requirements.

Introduction

The

PSC3P5xD

and

PSC3M5xD

devices are part of the

PSOC™ Control C3

MCU family designed for real-time control, enhanced sensing, secure, and low-power operations. Some target applications for these microcontrollers are:

Industrial motor-controllers

Power-stage converters

Home appliances

Automation devices

Low-power sensors

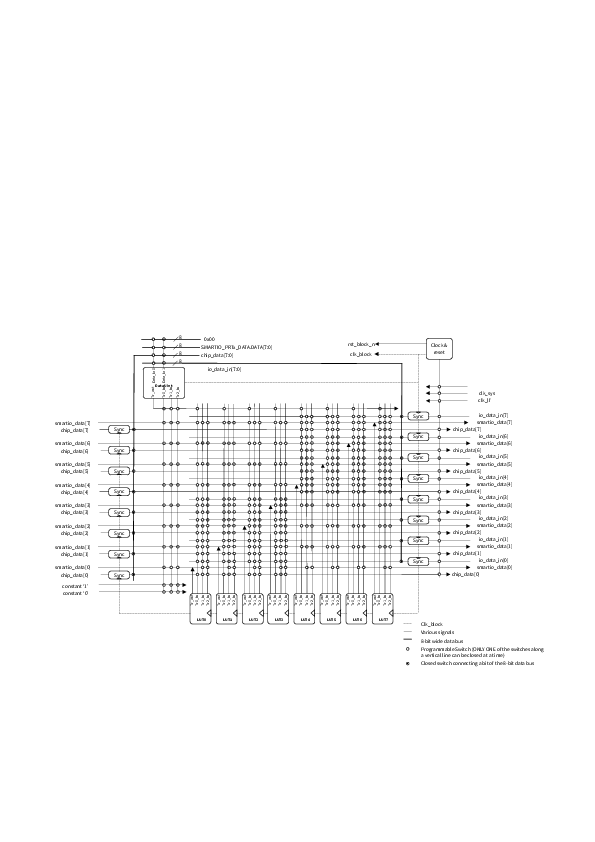

A detailed block diagram of the MCU is shown in

Figure 1

.

Figure 1.

Functional block diagram

Device identification and revisions

Family ID = 0x118(12‑bit); Si ID range = EE40- EE7F; Major‑minor rev ID = 0x1, 0x1

Detailed features

This device has the following features:

CPU subsystem

Arm® Cortex®-M33 running up to 180 MHz

Digital signal processor (DSP), floating-point unit (FPU), memory protection unit (MPU), 16 KB I-cache

Two direct memory access (DMA) controllers with 16 channels each

Security

Platform security architecture level 2 (PSA L2) certified

Step-wise authentication of execution images until the control is handed over to the user code

Secure execution of code in the execute-only mode for protected routines

Image authentication and integrity check

TrustZone framework that establishes an isolated device root of trust (RoT) for trust attestation and software management

Memory

On-chip flash with ECC support

Up to 256-KB flash with read while write (RWW) capability, 64 KB ROM for boot code, and bootloader functions

Built-in device firmware upgrade (DFU) support in boot ROM via serial interface (UART/I2C/SPI)

SRAM with ECC support

64 KB full SRAM available in Deep Sleep

SRAM data path is protected with a hardware mechanism (ECC) for soft error detection and correction

Clocking subsystem

8 MHz IMO with Deep Sleep operation offering ±2% accuracy

48 MHz internal high-frequency oscillator (IHO) offering ±1% accuracy

32 kHz internal low frequency oscillator (ILO) offering ±10% accuracy

4 to 35 MHz external crystal oscillator (ECO) support

32.768 kHz external watch crystal oscillator (WCO) usable for real-time clock (RTC)

External clock (EXTCLK): Maximum frequency 80 MHz

One frequency lock loop (FLL) with 24-100 MHz output range

Two digital phase-locked loops, DPLL#0 and DPLL#1, with 25-250 MHz output range

Low power (1.71 V to 3.6 V) operation

Six power modes (Active, Sleep, Deep Sleep, Deep Sleep-RAM, Deep Sleep-OFF, and Hibernate) for fine-grained power management

Deep Sleep mode current of 11 µA at 3.3-V external supply using an internal voltage regulator with 64-KB SRAM retention, LPComp, and Deep Sleep SCB

Hibernate mode current with RTC and LPComp of up to 1000 nA

Communication peripherals

Serial communication blocks (SCBs)

Up to six independent run-time-reconfigurable SCBs; each is software-configurable as I2C, SPI, or UART in master or slave mode

One SCB also supports Deep Sleep operation and wake-up from Deep Sleep in I2C slave and SPI slave modes

One SCB has fast SPI support of up to 50 MHz

SCB supports single-wire half-duplex mode for UART

CAN FD

Up to two CAN FD channels with a single instance with operation of up to 8 Mbps

High-performance, programmable analog subsystem (HPPASS)

Analog-to-digital converter (ADC)

One 12-bit, 12-Msps SAR ADC

Up to 16 dedicated analog pads, connected to up to 16 parallel sample stages

Two additional GPIOs can be used as analog inputs

Up to 16 sample/hold (S/H) circuits in SAR ADC connected to pins directly or through AMUX

One S/H circuit in SAR ADC is internally connected to analog references and a temperature sensor

Configurable input gain of 1, 3, 6, and 12 on all 16 S/H circuits

Digital comparator at the output to compare the ADC result against programmed boundary values

Digital comparator outputs can be connected to timer/counter pulse-width modulator (TCPWM) (low latency between the modules)

Analog comparators

Five Active comparators without Deep Sleep functionality, each with a 10-bit DAC to generate the comparator reference

Each comparator supports an external reference/threshold through pins

Active comparator can be used with the built-in DAC in Hysteresis mode

Two additional comparators in LPComp are available in Active/Deep Sleep/Hibernate modes

Comparator outputs can be brought to pins for control loop applications

Comparator outputs can be connected to TCPWM (low latency between the modules)

Logical OR of multiple comparator trigger outputs connected as an input trigger to TCPWM via trigger MUX

Real-time control peripherals

Coordinate rotation digital computer (CORDIC)

Supports all CORDIC operating modes for solving circular (trigonometric), hyperbolic functions, and integrated independent lookup tables to accelerate calculation

Timer/counter pulse-width modulator (TCPWM)

Sixteen 16-bit TCPWM channels

Four 32-bit TCPWM channels supporting high-resolution PWM generation (HRPWM) for PWM outputs

Center-aligned, edge, and pseudorandom modes

Comparator-based triggering of kill signals

Shadow update of duty, period, dead-time, output signal polarity, and dithering (pseudorandom mode)

Multichannel control: In a group of eight TCPWM channels, one channel within a group can trigger another channel

Ability to logically combine the outputs of multiple channels through Smart I/O

Dedicated output triggers mux in a group to allow flexibility to the PWM channel as a trigger and/or gate signals to the HPPASS

Hall sensor interface with autonomous BLDC block commutation support

Quadrature encoder interface to decode motor speed and rotor position

HRPWM feature for period, duty, and dead-time insertion with a typical resolution of less than 80 ps

I/O subsystem

Programmable GPIO pins

Up to 66 functional pins (50 digital GPIOs; 2 out of 50 GPIOs can be used for analog inputs + 16 dedicated analog-only inputs)

Programmable drive modes, strengths, and slew rates

Programmable digital

Up to seven Smart I/O capable ports (28 I/Os, 56 LUTs) enable Boolean operations on I/O signals

Cryptography

Cryptography accelerator

Hardware acceleration for symmetric (AES-128) and asymmetric cryptographic algorithms (RSA and elliptic curve cryptography (ECC)) supported by vector unit (VU) and hash functions (SHA-256)

True random number generator (TRNG) function

Chip-level functional description

Power

The device offers multiple features for managing and reducing power draw. Multiple power modes include Active, Sleep, Deep Sleep, and Hibernate. Deep Sleep has three variations based on retention of SRAM.

The power control block provides assurance that voltage levels meet the requirements of the respective modes. It can:

Delay mode entry (for example, at power-on reset (POR)) until voltage levels are as required for proper functioning

Detect operation below safe power supply levels:

Generates interrupts for low-voltage detection (LVD)

Generates reset for brownout detection (BOD)

The device operates using a single regulated VDDD supply within the range of 1.71 V to 3.6 V. In addition, there is an optional VBACKUP supply that can be used, which has a range of 1.4 V to 3.6 V. A linear regulator powers the core logic at four voltage levels:

0.9 V, 1.0 V, 1.1 V, and 1.2 V

. Voltage level switching is implemented by writing to the power control registers. The voltage for the core logic can be set based on the application's performance and power requirements; (see

Power modes

). With clock gating at peripheral and bus levels, this permits fine-grained optimization of energy usage.

Typically, the backup domain requires an input voltage of 1.4 V to 3.6 V, which can be provided by connecting a backup battery or a super capacitor to the VBACKUP pin. The internal backup switch automatically selects between VDDD and VBACKUP (when VDDD is no longer available) for powering the backup domain peripherals like RTC, WCO, ILO, and Backup registers. Some I/O cells are powered from the VBACKUP supply before the internal backup switch. If the application does not require a dedicated backup source, VBACKUP can be connected to VDDD externally to ensure that the I/O cells powered by VBACKUP are functional.

The device has multiple VDDIO pins that are used to power the I/O cells except the backup domain I/O cells. VDDIO can either be connected to the same supply as VDDD or an independent supply voltage within the valid operating range. This provides more flexibility in terms of choosing the logic level for the port pins powered using different VDDIO supplies. The VDDIO supply can be switched off if the port I/Os are not used. Switching off the VDDIO supply is only allowed in Active or Deep Sleep mode. VDDIO should not be switched off when the device is in Hibernate mode. Refer to the

gxg1730181873132.html#mfy1698739677971

section for information about the VBACKUP or VDDIO supply used for powering the port I/O cells.

Power connections

The following power system diagrams show typical connections for the power pins for all the supported packages. In these diagrams, the package pin is shown with the pin name, for example, "VDD;

9

".

There is no dependency on power supply sequencing.

Figure 2.

LQFP-80 package power connections

Figure 3.

LQFP-64/QFN-64 package power connection

Figure 4.

LQFP-48/QFN-48 package power connections

Power domains

The device has independent power domains, allowing the domain power to be enabled/disabled depending on the power mode.

A diagram of the power connections and routing is shown in

Figure 4

:

Figure 5.

Power distribution and domains

Power modes

The device can operate in five power modes. These power modes are intended to minimize the average power consumption in an application.

Power modes supported are:

Active/Sleep:

All peripherals are powered. The CPU is either active and executing the code or can be put in sleep (clock gated). Any interrupt can wake up the CPU within one CPU clock cycle to resume operation. In Active/Sleep mode, the core voltage can be set to any of the four values. This impacts both power consumption and maximum clock frequency for CPU and peripherals. The following power profiles are supported in Active/Sleep mode:

ULP (Ultra Low Power): 0.9 V core voltage with 50 MHz CPU frequency

MF (Medium Frequency): 1.0 V core voltage with 70 MHz CPU frequency

LP (Low Power): 1.1 V core voltage with

150 MHz

CPU frequency

OD (Overdrive): 1.2 V core voltage with 180 MHz CPU frequency

Deep Sleep:

The CPU is in retention mode. RAM content is also retained. Only Deep Sleep capable peripherals can wake up the system. Once awake, the operation resumes

Deep Sleep-RAM:

The CPU is turned off. 64 KB of SRAM is retained for a warm boot after wake-up. Only Deep Sleep-capable peripherals are operational if enabled and are capable of waking up the system

Deep Sleep-OFF

Same as Deep Sleep RAM except RAM is also turned off. The wake-up action is reset or cold boot

Hibernate:

All peripherals except LPComp and backup domain peripherals such as RTC is turned off. All clocks except the backup domain clock and all internal regulators are turned off. This results in asynchronous operation of the LPComp. The system is reset when it exits the Hibernate mode

Power mode transitions

The device supports Arm® standard power modes; see the

Power modes

section for details.

Table 1

lists the parameters for supported power modes:

Active/Sleep | Deep Sleep | Deep Sleep-RAM | Deep Sleep-OFF | Hibernate | Off | |

|---|---|---|---|---|---|---|

Parameters | ||||||

Wake source 1 | Any interrupt | DS peripherals | DS peripherals | DS peripherals | RTC/HIB peripherals | Power on |

Wake action | Resume | Resume | Warm boot | Reset/cold boot | Reset | Reset |

Wake time | One CPU cycle | <20 µs | Deep Sleep + warm boot | Deep Sleep + cold boot | POR + cold boot < 1 ms | |

Resources | ||||||

ECO | On/Off | Off | Off | Off | Off | Off |

IHO | On | Off | Off | Off | Off | Off |

IMO | On | On/Off | Off | Off | Off | Off |

ILO | On/Off | On/Off | On/Off | On/Off | On/Off | Off |

WCO | On/Off | On/Off | On/Off | On/Off | On/Off | Off |

CPU | On/Sleep | Retention | Off | Off | Off | Off |

SRAM | On | On | On/Off | Off | Off | Off |

Power block support

shows the available operational states for the major blocks in this device. Note that the operational states possible in low-power modes are generally limited in functionality and parametric performance as compared to their capabilities in the Active power mode. Additionally, blocks that do not support low-power modes such as Deep Sleep and Hibernate cannot wake up the CPU from these power modes. See

Power modes

for details.

Block | Power mode | ||||

|---|---|---|---|---|---|

Active | Sleep | Deep Sleep | Hibernate | Backup | |

CPUSS | |||||

CPU | Y | N | N | N | N |

NVIC | Y | Y | N | N | N |

WIC | Y | Y | Y | Y | N |

FLASH | Y | Y | N | N | N |

SRAM | Y | Y | Y | N | N |

DMA | Y | Y | N | N | N |

Programmable digital | |||||

SMART I/O | Y | Y | Y | N | N |

Fixed function digital | |||||

TCPWM | Y | Y | N | N | N |

SCB | Y | Y | Y 2 | N | N |

CAN FD | Y | Y | N | N | N |

Special function | |||||

CORDIC | Y | N | N | N | N |

Analog | |||||

HPPASS (SAR, CSG) | Y | Y | N | N | N |

LPComp | Y | Y | Y 3 | Y | N |

I/O | |||||

GPIO | Y | Y | Y | Y 4 | N |

Backup | |||||

RTC | Y | Y | Y | Y | Y |

Registers | Y | Y | Y | Y | Y |

Security

Both secure and nonsecure debug accesses are supported. In nonsecure access, the debugger cannot access the areas marked as “secure”. In the secure case, the device can be “locked” such that it may not be acquired for test or debug.

Certificate management assures that appropriate accesses are provided for secure debug and RMA transition.

This device is fully compliant with Arm® TrustZone at hardware and software levels. An extra layer of security is implemented with the help of Infineon-proprietary protection units.

PSA L2-certified parts support PSA-compliant cryptographic services, key management, and secure storage services (For PSA L2 parts, see

gxg1730181873132.html#lqc1681475602142

).

Security features

Arm® platform security architecture compliant with PSA level 2 precertification, depending on part number (see

gxg1730181873132.html#lqc1681475602142

)

Protected firmware feature support depending on part number (see

gxg1730181873132.html#lqc1681475602142

)

Hardware crypto accelerator with comprehensive support of cryptographic algorithms

Secure isolation of processing environments via Arm® TrustZone

Infineon proprietary MPU, MPC, and PPCs for memory and peripheral access control

Off-the-shelf secure isolation using Trusted Firmware‑M (TF‑M) and mbedTLS crypto acceleration package

Security architecture overview

Cortex® ‑M33:

Arm® TrustZone enabled core with two processing environments: secure (SPE) and nonsecure (NSPE)

Infineon proprietary protection units for memory and peripheral protection

Integrated mbedTLS crypto acceleration package that supports software and hardware cryptography services

Infineon-provided Trusted firmware‑M (TF‑M) implemented in SPE — its services are leveraged by Cortex® ‑M33 NSPE and SPE

Figure 6.

Security architecture diagram

Block functional description

CPU

Arm® Cortex®-M33 with digital signal processor (DSP)

Floating-point unit (FPU)

The TrustZone framework establishes an isolated device root of trust for trusted attestation and software management

Memory protection unit (MPU): Supports eight regions each for secure and nonsecure MPUs

Secure attribution unit (SAU): It defines the security status of up to eight memory regions

Debug facilities including trace (embedded trace macrocell (ETM), no embedded trace buffer (ETB))

16 KB I-cache for flash and ROM access

A separate 4-channel interprocessor communication (IPC) module (two IRQs) offers seamless support for semaphores and mailbox structures within secure and nonsecure execution.

The subsystems include an interrupt controller such as a nested vectored interrupt controller (NVIC). It also consists of a wake-up interrupt controller (WIC), which can wake the processor up from system Deep Sleep mode, allowing the main processor power and clocks to be turned-off when the chip is in system Deep Sleep mode.

The CPU subsystem also includes debug interfaces and supports both SWD and JTAG. The chip also supports boundary scan, which is required for testing on a PCB, and a separate test access port (TAP) controller is provided for controlling boundary scan functions.

DMA

The Cortex®-M33 CPU includes two DMA controllers that can be used to transfer data to and from memory, and peripheral registers. This allows for autonomous transfer of data from peripherals such as ADC to memory, or allows deterministic control of peripherals such as the PWM.

The DMA controllers are bus masters in their respective domains. Each DMA has 16 channels. It has a single transfer engine for all channels that arbitrates for bus master access. The DMA uses the 32‑bit AHB bus that shares the same clock as the CPU.

Cryptography support (CryptoLite)

One instance of the cryptographic acceleration block that implements hardware support for true random number generator (TRNG), SHA-256, AES-128, and vector unit (VU), is provided.

Memory

The device features multiple nonvolatile and volatile memory types. The CPU and other bus masters can access any memory block. The number of wait states depends on the access path.

Flash

The device offer up to 256 KB of user-programmable flash. The flash supports single and dual bank modes. Dual bank mode supports the RWW feature, which allows reading from one sector while programming the other. In addition, the flash module has ECC support.

SFlash

The device has 32-KB supervisory flash (SFlash) memory. SFlash stores the device trim settings, secure key hashes, and FLASH_BOOT firmware. Device trim settings are used to initialize hardware resources for proper operation. Secure key hashes are used to authenticate Infineon and OEM assets and images. SFlash cannot be used to store user data.

ROM

All

PSOC™ Control C3

devices offer 64 KB of ROM. The ROM contains boot and configuration routines and authentication checks. After a reset event, the boot code in the supervisory ROM (SROM) checks the Reset Cause register to determine whether a Hibernate event was the cause of the reset to provide the fastest possible transition to execute the user code. This minimizes the wake-up time from Hibernate mode as opposed to a power on reset (POR) or an external reset (XRES) event.

RAM

The device has

64 KB

SRAM memory, with provision of retaining memory during Deep Sleep power mode. SRAM has ECC support for soft error detection and correction.

eFuse

The device contains 1024 one-time programmable (OTP) eFuse bits. These are reserved for system use such as device life-cycle management, trim, and hash values. eFuse bits cannot be directly programmed by the user.

Each fuse is individually programmed; once programmed (or “blown”), its state cannot be changed. Blowing a fuse transitions it from the default state of ‘0’ to ‘1’. To program an eFuse, VDDIO0 must be at 2.5 V ±10%.

Because blowing an eFuse is an irreversible process, any process requiring eFuse programming is recommended only in mass production under controlled factory conditions by Infineon provided provisioning tools.

Clock system

The

PSOC™ Control C3

clock system is responsible for providing clocks to all subsystems requiring clocks and switching between different clock sources without glitching. In addition, the clock system ensures that no metastable conditions occur.

Furthermore, a clock supervision (CSV) circuit is implemented for each clk_hf domain. The CSV circuit detects a stopped clock or an abnormal frequency of the monitored clock. There are clock counters for both the monitored clock and the reference clock. Parameters for each counter define the frequency of the reference clock and the upper and lower limit for the frequency of the monitored clock.

If the dedicated frequency range comparator detects a stopped clock or a clock outside the specified frequency range, an abnormal state is signaled. Depending on the register settings and how the monitored clock is used on the device, either a reset or an interrupt is generated.

The following clock sources are provided:

Internal main oscillator (IMO): 8 MHz ±2%, fast wake-up, low jitter

Internal high-speed oscillator (IHO): 48 MHz ±1%

Internal low-speed oscillator (ILO): 32 kHz ±10%, also as a wake-up source for the RTC

External crystal oscillators (ECO and WCO)

External crystal oscillator (ECO): 4 MHz - 36 MHz

External watch crystal oscillator (WCO): 32.768 kHz

External clock (EXTCLK): Maximum frequency 80 MHz

One frequency lock loop (FLL) with 24 -100 MHz output range

Two digital phase-locked loops, DPLL#0 and DPLL#1, with 25 - 250 MHz output range

Note:

FLL input clock should to be at least 2.5 times less than the FLL current controlled oscillator frequency. Therefore, with FLL output divider enabled, IHO can be used as FLL input clock source only when FLL output frequency is ≥ 60 MHz.

Internal main oscillator (IMO)

Internal main oscillator (IMO) operates at a fixed 8 MHz frequency. Its tolerance is ±2%. A high-speed clock can be derived using the IMO plus a DPLL. It has fast wake-up and low jitter.

Internal high-frequency oscillator (IHO)

Internal high-frequency oscillator (IHO) operates at a fixed 48 MHz frequency. Its tolerance is ±1%. A high speed-clock can be derived using the IHO plus DPLL.

Internal low-frequency oscillator (ILO)

The ILO is a low-power oscillator with a typical current of 0.3 µA and frequency of 32 kHz with ±10% accuracy. The ILO can be used as wake-up source for real-time clock (RTC)

External crystal oscillator (ECO)

External crystal oscillator (ECO) can use a crystal with frequency ranging from 4 MHz to 36 MHz for generating a high-precision clock. This option can be used when the precision offered by internal oscillators is not sufficient.

Watch crystal oscillator (WCO)

WCO uses an external 32.768 kHz crystal for applications requiring higher-precision real-time clock (RTC) functionality. WCO clock can be routed directly to the RTC for higher precision and to avoid any glitches due to internal switching of clock sources.

Watchdog timer (WDT)

One watchdog timer (WDT) and one multi-counter watchdog timer (MCWDT) are provided. The WDT is implemented in the clock block running from the ILO or the WCO. This allows the watchdog operation during Deep Sleep and can generate a watchdog reset if not serviced before the timeout. The watchdog reset is recorded in the Reset Cause register.

Real-time clock (RTC)

The device includes a real-time clock (RTC). The RTC has the following features:

Can operate in both 12-hour format with AM/PM flag and 24-hour format

Automatic leap year correction

The alarm feature allows the RTC to generate an interrupt, which may be used to wake up the system from Sleep, Deep Sleep, and Hibernate power modes

Reset

The device can be reset from various sources, including a software reset. Reset events are asynchronous and ensure reversion to a known state. The reset cause (WDT, MCWDT, Faults, Debug, Software, and Clock Supervision) is recorded in a register, which is sticky through reset, and allows the software to determine the cause of the reset. An XRES pin is available for external reset.

High-performance programmable analog subsystem (HPPASS)

12-bit SAR analog-to-digital converter (ADC)

The device has one 12-bit SAR ADC with up to 16 parallel sampling channels. The ADC supports multiple S/H, which enables synchronous sampling on several channels.

All analog channels support individually selectable input gains of 1, 3, 6, and 12. In addition, all channels can be oversampled and averaged in hardware. The SAR ADC supports up to

12-Msps

rate for a repeated conversion of the same channel. The ADC can operate with a voltage range between 1.71 V to 3.6 V (VDDA).

VDDA needs to be between 2.7 V to 3.6 V for running the HPPASS at 240 MHz.

The AREF_EXT pin is used to provide the ADC reference voltage. It can be connected to a precision reference voltage generator (1.71 V to VDDA) or connected externally to the AVCC pin.

The idle sampling feature allows ADC triggers to start directly from hold operation. All 16 samplers can be triggered simultaneously for simultaneous idle sampling (same hold instance) and sequential conversion (useful for multimotor, multiphase motor control and digital power applications). ADC has a sequencer with eight groups that can be programmed according to the user application. Each group defines a set of inputs that will be simultaneously sampled when that group is triggered by hardware or firmware. Each group supports the control and conversion of up to 16 samplers, and the sample time can be configured for each group. It supports two-level priority conversion. Each group can be configured to high or low-priority conversion.

The ADC has a set of built-in post processing features for the converted digital data such as averaging (result accumulation), pseudo differential mode, 2x FIR with 16 taps, 8x limit detect, 8x channel gain and offset correction coefficients with support for signed or unsigned result format. These features help in reducing CPU utilization for analog data acquisition and post processing.

The ADC can be connected to an internal temperature sensor, the value of which can be read and digitized. This is useful for calibration and other temperature-dependent functions. For more information, see

Temperature sensor

. The ADC is not available in the Deep Sleep and Hibernate power modes.

Comparator and slope generator (CSG)

The device has five analog comparators that operate in Active mode. The comparator output is synchronized to avoid metastability. The comparator output can be routed to a GPIO or TCPWM (through TriggerMux), for example, as an input to kill the PWM signal if an overvoltage or over current condition is detected.

The five Active mode comparators can use the built-in 10-bit DACs or another analog input to define the programmable threshold for the comparator. The output of the DAC serves as a reference for the comparator. The DAC output is connected to the internal S/H circuit of the ADC through AMUX with other inputs. The ADC can measure the output of the comparator.

The comparator DAC values can be updated by either direct or buffered writes. This can be used for slope generation or LUT waveform generation.

The comparators can also be used in Hysteresis mode. Hysteresis voltage is configurable by the user and the comparator provides a run-time configuration for it.

Temperature sensor

The

PSOC™ Control C3

devices contain a diode-based temperature sensor. It can be disabled to save power. The temperature sensor is connected to the SAR ADC through AMUX as one of the measurement channels. The precision of the temperature sensor output is ±5°C over the full operating temperature range.

Low-power comparator (LPComp)

The device provides two low-power comparators that can operate in all power modes. This allows other analog system resources to be disabled while retaining the ability to monitor external voltage levels during Deep Sleep and Hibernate modes. The comparator outputs are normally synchronized to avoid metastability unless operating in an asynchronous power mode (Hibernate) where the wake-up circuit is activated by a comparator-switch event.

Fixed function digital

Timer/counter pulse-width modulator (TCPWM)

The TCPWM consists of the following:

A counter with user-programmable period/duty length PWM outputs

A capture register to record the count value at the time of an event (which may be an I/O event)

A period register to either stop or auto reload the counter when its count is equal to the period registers

Compare registers to generate compare value signals that are used as PWM duty cycle outputs

The block provides accurate and complementary outputs with a programmable offset between them to allow its use as dead-band programmable complementary PWM outputs. It also has a kill input to force the outputs to a predetermined state; this can be used in motor drive and power conversion systems, for example, when an overcurrent state is indicated and the PWMs driving the FETs must be shut off immediately with no time for software intervention.

TCPWM has a Motion Interface (MOTIF) block that can be used in Hall sensor, Quadrature encoder or standalone Multichannel mode.

TCPWM also supports a high-resolution PWM (HRPWM) feature. The 32-bit four-channel TCPWM counters are enhanced with the following functionalities:

It can program and control the PWM output signals with a typical resolution of less than 100 ps

It can control the period, duty cycle, and dead-time with the high-resolution function

Serial communication block (SCB)

The

PSOC™ Control C3

has up to six SCB modules, which can be software-configured for I2C, UART, or SPI interface as master or slave when in Active mode. One of the SCB modules can operate in Deep Sleep mode with an external clock with the functionality limited to I2C slave or SPI slave. Every protocol can use a 256-byte-deep FIFO per SCB module. All SCB blocks support DMA transfers.

Note:

SCB4 and SCB5 not available in 48-pin devices.

Inter-integrated circuit (I2C)

The hardware I2C block implements a full multi-master and multi-slave interface and is capable of multi-master arbitration. This block can operate at speeds of up to 1 Mbps (Fast Mode Plus) and has flexible buffering options to reduce the interrupt overhead and latency for the CPU. It also supports EZI2C, which creates a mailbox address range in the memory of the

PSOC™ Control C3

. This effectively reduces the I2C communication overheads for reading from and writing to an array in the memory. The FIFO significantly reduces the need for clock stretching caused by the CPU not having read the data on time.

Universal asynchronous transmitter receiver (UART)

The full-feature UART can operate at up to 8 Mbps. It supports LIN (automotive single-wire interface), IrDA (Infrared interface), and SmartCard (ISO7816) protocols. In addition, it supports the 9-bit multiprocessor mode, which allows addressing of peripherals connected over common RX and TX lines. Common UART functions such as hardware flow control, parity, break detection, and frame error are supported. The SCB can be configured in half-duplex UART mode for single-wire communication.

Serial peripheral interface (SPI)

The SPI mode supports full Motorola SPI, Texas Instruments synchronous serial port (SSP) (essentially adds a start pulse used to synchronize SPI codecs), and National Semiconductor Microwire (a half-duplex form of SPI). The SPI block also supports an EZ-SPI mode in which data interchange is reduced to reading and writing an array in memory.

Fast SPI can support master and slave functionalities up to 50 MHz.

Controller area network flexible data-rate (CAN FD)

CAN FD features two channels including timestamp support and a 4-KB message RAM per channel. This block supports data rates of up to 8 Mbps.

Trigger multiplexer (Trigger MUX)

Trigger MUX is used to connect trigger and input/output signals between peripherals as well as GPIO pins. It can be used to connect several TCPWM counter channels to achieve multichannel support. It also provides the extended signal routing functionality such as routing any TCPWM counter PWM outputs to any GPIO pin through peri.tr_io_output[n] alternate function.

The trigger connections between TCPWM and HPPASS are also connected through the Trigger MUX. Any TCPWM counter can be configured to trigger any S/H circuit of the ADC inside HPPASS.

The digital comparator outputs from the ADC and analog comparator outputs are also connected to the TCPWM from the HPPASS through the Trigger MUX. It is possible to route any digital/analog comparator output to any TCPWM group and any counter inside the group.

The connections between the TCPWM and HPPASS are optimized for low latency.

Coordinate rotation digital computer (CORDIC)

CORDIC is used to precisely compute the transforms used in motor speed and position estimation as well as reference plane transforms commonly used in Field-Oriented Control (FOC). It calculates trigonometric functions in hardware to offload the processing from the main CPU. Supported algorithms include sine, cosine, arctan, sinh, cosh, arctanh, phase, sqrt, and park transform.

General-purpose input/output (GPIO) ports

The

PSOC™ Control C3

provides up to

50

GPIO pads with two pad-power-supply domains. Two of the GPIOs are multiplexed with analog inputs, making it possible to have a maximum of 18 analog input connections. The GPIO block has the following features:

Eight drive modes including strong push-pull, resistive pull-up and pull-down, open-drain and open-source, input-only, and disabled

Analog signal input capability (I/O buffers disabled; signal passed through switches)

Input threshold select (CMOS or LVTTL)

Individual control of input and output disables

Hold mode for latching the previous state (used for retaining the I/O state in Deep Sleep and Hibernate modes)

Selectable slew rates for dV/dt-related noise control

The pins are organized in logical entities called "ports". During power-on and reset, the blocks are forced to the disabled state so they do not crowbar any inputs and/or cause excess turn-on current. A multiplexing network known as a "high-speed I/O matrix" (HSIOM) is used to multiplex between various signals that may connect to an I/O pin.

Data Output and Pin State registers store the values to be driven on the pins and the pins' states.

Every I/O pin can generate an interrupt if so enabled, and each I/O port has an interrupt request (IRQ) and interrupt service routine (ISR) vector associated with it.

The I/O ports will retain their state during Hibernate mode. If the operation is restored using Reset, then the pins will go to the High-Z state; if the operation is restored by using the wake-up pin, the pin drivers will retain their previously frozen state until the firmware chooses to change it.

Simultaneous output switching in high-current mode requires attention to line termination and decoupling capacitor size to control switching transient voltages.

Smart I/O (Programmable I/O)

Each smart I/O block contains eight programmable LUT arrays out of which up to six LUT arrays are associated with a particular I/O port that allows integration of board-level glue logic and Boolean functions at the pins. The remaining free LUT arrays can be connected to the I/O LUT array outputs for creating more complex logic functions. It is similar to programmable array logic (PAL) or small programmable logic devices (PLDs). The smart I/O block is interposed between the port pins and the HSIOM (responsible for multiplexing signals from on-chip peripherals to and from the port pins) and the digital signal interconnect (DSI) signals. It is possible to bypass the smart I/O block in order not to impact the propagation delay for critical paths from the DSI to the port pins.

Figure 7.

Smart I/O block diagram

The structure is interposed between the GPIO port and the HSIOM.

Device firmware update (DFU)

The boot ROM supports firmware updates using a serial port. DFU functionality is disabled by default. It needs to be enabled in the OEM policy before use. More details regarding how to enable and use DFU can be found in

AN240106 - Getting started with PSOC™ Control C3 security

.

When enabled, DFU mode selection is initiated during device boot-up depending on the state of P2.2 and P2.3 pins as shown in the table:

P2.3 pin state | P2.2 pin state | DFU mode |

|---|---|---|

High-Z | High-Z | Disable |

High-Z | X | Disable |

X | High-Z | Disable |

Low | Low | Disable |

Low | High | I2C |

High | Low | UART |

High | High | SPI |

X = Don't care

Use pull-up or pull-down resistors of 1 kΩ or less connected to VDDIO_0 or VSS to set these pins to logic high or low. Pins can be left floating for High-Z state. When the device is in DFU mode, the following pins are used for serial communication:

Pin | I2C | UART | SPI |

|---|---|---|---|

P8.0 | CS | ||

P8.1 | SCL | RX | MOSI |

P8.2 | MISO | ||

P8.3 | SDA | TX | CLK |

The following parameters are used for the DFU communication protocols:

I2C: Speed = 400 kHz, Mode = Slave, 7-bit address, address = 0x35

UART: Baud = 115200, Bits = 8, Stop Bits = 1, RTS/CTS = No, Parity = None

SPI: Mode = Slave, Motorola 00 (MSB first, CPHA = 0, CPOL = 0), Speed <= 12 Mbps

Note:

Boot ROM DFU support is available only in 80-pin and 64-pin devices.

Serial wire JTAG debug port/Embedded trace macrocell

Serial wire JTAG debug port (SWJ-DP)

The

PSOC™ Control C3

MCU embeds the ARM® serial wire JTAG debug port (SWJ-DP) which supports 2-wire Serial Wire Debug (SWD) and 4-wire or 5-wire Joint Test Action Group (JTAG) interface. SWD interface is enabled by default after power on and JTAG interface is in disabled state. JTAG can be enabled in 4-wire or 5-wire mode by updating the OEM policy. For more information on updating the OEM policy, refer to the

AN240106 - Getting started with PSOC™ Control C3 security

.

Embedded trace macrocell (ETM)

Arm® embedded trace macrocell is supported by the

PSOC™ Control C3

. It allows reconstruction of program execution using high speed compressed data transmitted on the ETM pins. ETM interface includes a clock (trace.clock) pin and up to four data (trace.data0 to trace.data3) pins.

Pins

GPIO ports and analog inputs are powered by VDDx pins as follows:

P0: VBACKUP

P1, P2, P3, P4, P5, P6, P7: VDDIO_0

P8, P9: VDDIO_1

AN_A, AN_B: AVDD

The number of GPIOs is limited in some packages. The E-LQFP-80 package has the full 50 GPIOs and 16 dedicated analog inputs; the E-LQFP-64/VQNF-64 package has 39 GPIOs and 16 dedicated analog inputs; the E-LQFP-48/VQFN-48 package has 29 GPIOs and 10 dedicated analog inputs. For detailed information on the supported packages, see

gxg1730181873132.html#bcm1697083377157

section.

Pin | Capability | Packages | ||

|---|---|---|---|---|

E-LQFP-80 | E-LQFP-64/VQFN-64 | E-LQFP-48/VQFN-48 | ||

VDDD | - | 9 | 5 | 4 |

VDDA | - | 66 | 54 | 41 |

VDDIO_0_0 | - | 20 | 16 | 12 |

VDDIO_0_1 | - | 40 | 32 | 24 |

VDDIO_0_2 | - | 49 | - | - |

VDDIO_1 | - | 80 | 64 | 48 |

VCCD | - | 10 | 6 | 5 |

VSS | - | GND PAD | GND PAD | GND PAD |

VSS_0 | - | 6 | - | - |

VSS_1 | - | 7 | - | - |

VSS_2 | - | 77 | - | - |

VSS_3 | - | 78 | - | - |

VAREF_EXT | - | 65 | 53 | 40 |

VBACKUP | - | 11 | 7 | 6 |

AN_A0 | AD | 53 | 41 | 31 |

AN_A1 | AD | 54 | 42 | 32 |

AN_A2 | AD | 55 | 43 | 33 |

AN_A3 | AD | 56 | 44 | 34 |

AN_A4 | AD | 57 | 45 | 35 |

AN_A5 | AD | 58 | 46 | 36 |

AN_A6 | AD | 59 | 47 | - |

AN_A7 | AD | 60 | 48 | - |

AN_B0 | AD | 61 | 49 | - |

AN_B1 | AD | 62 | 50 | 37 |

AN_B2 | AD | 63 | 51 | 38 |

AN_B3 | AD | 64 | 52 | 39 |

AN_B4 | AM | 67 | 55 | 42 |

AN_B5 | AM | 68 | 56 | - |

AN_B6 | AM | 69 | 57 | - |

AN_B7 | AM | 70 | 58 | - |

XRES | - | 8 | 4 | 3 |

P0.0 | S | 12 | 8 | 7 |

P0.1 | S | 13 | 9 | - |

P1.0 | S | 14 | 10 | - |

P1.1 | S | 15 | 11 | - |

P1.2 | S | 16 | 12 | 8 |

P1.3 | S | 17 | 13 | 9 |

P2.0 | S | 18 | 14 | 10 |

P2.1 | S | 19 | 15 | 11 |

P2.2 | S | 21 | 17 | 13 |

P2.3 | S | 22 | 18 | 14 |

P3.0 | S | 23 | - | - |

P3.1 | S | 24 | - | - |

P3.2 | S | 25 | - | - |

P3.3 | S | 26 | - | - |

P4.0 | - | 27 | 19 | 15 |

P4.1 | - | 28 | 20 | 16 |

P4.2 | - | 29 | 21 | 17 |

P4.3 | - | 30 | 22 | 18 |

P4.4 | - | 31 | 23 | 19 |

P4.5 | - | 32 | 24 | 20 |

P4.6 | - | 33 | 25 | 21 |

P4.7 | - | 34 | 26 | 22 |

P5.0 | S | 35 | 27 | - |

P5.1 | S | 36 | 28 | - |

P5.2 | S | 37 | 29 | - |

P5.3 | S | 38 | 30 | - |

P6.0 | S | 39 | 31 | 23 |

P6.1 | S | 41 | 33 | 25 |

P6.2 | S | 42 | 34 | 26 |

P6.3 | S | 43 | 35 | 27 |

P7.0 | - | 44 | 36 | 28 |

P7.1 | - | 45 | 37 | 29 |

P7.2 | - | 46 | 38 | 30 |

P7.3 | - | 47 | 39 | - |

P7.4 | - | 48 | 40 | - |

P7.5 | - | 50 | - | - |

P7.6 | - | 51 | - | - |

P7.7 | - | 52 | - | - |

P8.0 | AM, AC | 71 | 59 | 43 |

P8.1 | AM | 72 | 60 | 44 |

P8.2 | AM, AC | 73 | 61 | 45 |

P8.3 | AM | 74 | 62 | 46 |

P8.4 | - | 75 | - | - |

P8.5 | - | 76 | - | - |

P9.0 | S | 79 | 63 | 47 |

P9.1 | S | 1 | 1 | - |

P9.2 | S | 2 | 2 | 1 |

P9.3 | S | 3 | 3 | 2 |

P9.4 | S | 4 | - | - |

P9.5 | S | 5 | - | - |

Abbreviation | Capability |

|---|---|

AD | Dedicated analog pin directly connected to sampler |

AM | Dedicated analog pin/analog capable GPIO pin connected to sampler through MUX |

AC | Analog capable GPIO pin (LPComp input) |

S | Smart IO capable GPIO |

Note:

All GPIO pins are PWM capable. Any TCPWM channel line or line_compl output can be routed to any GPIO pin

Number of LUTs is not impacted by the number of Smart IO capable GPIO pins available in lower pin count packages

Figure 8.

Device pinout for E-LQFP-80 package (top view)

Figure 9.

Device pinout for E-LQFP-64 package (top view)

Figure 10.

Device pinout for VQFN-64 package (top view)

Figure 11.

Device pinout for E-LQFP-48 package (top view)

Figure 12.

Device pinout for VQFN-48 package (top view)

GPIO alternate functions tables

GPIO | Alternate functions and HSIOM routes | |||

|---|---|---|---|---|

P0.0 | wco_out | fixed | smartio0.io0 | fixed |

ext_clk | ACT #8 | peri.tr_io_input[0]:0 | ACT #14 | |

peri.tr_io_output[0]:0 | ACT #15 | |||

P0.1 | wco_in | fixed | smartio0.io1 | fixed |

peri.tr_io_input[1]:0 | ACT #14 | peri.tr_io_output[1]:0 | ACT #15 | |

P1.0 | eco_in | fixed | smartio1.io0 | fixed |

peri.tr_io_output[58]:1 | ACT #1 | peri.tr_io_output[70]:1 | ACT #2 | |

scb1.uart.cts | ACT #4 | scb1.spi.select0 | ACT #6 | |

peri.tr_io_input[2]:0 | ACT #14 | peri.tr_io_output[2]:0 | ACT #15 | |

P1.1 | eco_out | fixed | smartio1.io1 | fixed |

peri.tr_io_output[59]:1 | ACT #1 | peri.tr_io_output[71]:1 | ACT #2 | |

scb1.uart.rts | ACT #4 | scb1.spi.clk | ACT #6 | |

peri.tr_io_input[3]:0 | ACT #14 | peri.tr_io_output[3]:0 | ACT #15 | |

P1.2 | smartio1.io2 | fixed | peri.tr_io_output[60]:1 | ACT #1 |

peri.tr_io_output[72]:1 | ACT #2 | scb1.uart.rx | ACT #4 | |

scb1.spi.mosi | ACT #6 | scb1.i2c.sda | ACT #7 | |

peri.tr_io_input[4]:0 | ACT #14 | peri.tr_io_output[4]:0 | ACT #15 | |

swj.swclk/tclk | DS #5 | |||

P1.3 | smartio1.io3 | fixed | peri.tr_io_output[61]:1 | ACT #1 |

peri.tr_io_output[73]:1 | ACT #2 | scb1.uart.tx | ACT #4 | |

scb1.spi.miso | ACT #6 | scb1.i2c.scl | ACT #7 | |

peri.tr_io_input[5]:0 | ACT #14 | peri.tr_io_output[5]:0 | ACT #15 | |

swj.swdio/tms | DS #5 | |||

P2.0 | hibernate_wakeup | fixed | smartio2.io0 | fixed |

peri.tr_io_output[58]:0 | ACT #1 | tcpwm0.g2.cnt6+ | ACT #2 | |

scb1.uart.cts | ACT #4 | scb1.spi.select0 | ACT #6 | |

peri.tr_io_input[6]:0 | ACT #14 | peri.tr_io_output[6]:0 | ACT #15 | |

swj.tdi | DS #5 | |||

P2.1 | smartio2.io1 | fixed | peri.tr_io_output[59]:0 | ACT #1 |

tcpwm0.g2.cnt6- | ACT #2 | cal_wave | DS #0 | |

scb1.uart.rts | ACT #4 | scb1.spi.clk | ACT #6 | |

scb1.i2c.scl | ACT #7 | peri.tr_io_input[7]:0 | ACT #14 | |

peri.tr_io_output[7]:0 | ACT #15 | swj.tdo | DS #5 | |

P2.2 | smartio2.io2 | fixed | peri.tr_io_output[60]:0 | ACT #1 |

tcpwm0.g2.cnt7+ | ACT #2 | scb1.uart.rx | ACT #4 | |

scb1.spi.mosi | ACT #6 | scb1.i2c.sda | ACT #7 | |

ext_clk | ACT #8 | peri.tr_io_input[8]:0 | ACT #14 | |

peri.tr_io_output[8]:0 | ACT #15 | |||

P2.3 | smartio2.io3 | fixed | peri.tr_io_output[61]:0 | ACT #1 |

tcpwm0.g2.cnt7- | ACT #2 | scb1.uart.tx | ACT #4 | |

scb1.spi.miso | ACT #6 | peri.tr_io_input[9]:0 | ACT #14 | |

peri.tr_io_output[9]:0 | ACT #15 | |||

P3.0 | smartio3.io0 | fixed | peri.tr_io_output[62]:0 | ACT #1 |

scb4.uart.cts | ACT #4 | scb4.spi.mosi | ACT #6 | |

peri.tr_io_input[10]:0 | ACT #14 | peri.tr_io_output[10]:0 | ACT #15 | |

P3.1 | smartio3.io1 | fixed | peri.tr_io_output[63]:0 | ACT #1 |

scb4.uart.rts | ACT #4 | scb4.spi.miso | ACT #6 | |

scb4.i2c.sda | ACT #7 | peri.tr_io_input[11]:0 | ACT #14 | |

peri.tr_io_output[11]:0 | ACT #15 | |||

P3.2 | smartio3.io2 | fixed | peri.tr_io_output[64]:0 | ACT #1 |

scb4.uart.rx | ACT #4 | scb4.spi.clk | ACT #6 | |

scb4.i2c.scl | ACT #7 | peri.tr_io_input[12]:0 | ACT #14 | |

peri.tr_io_output[12]:0 | ACT #15 | |||

P3.3 | smartio3.io3 | fixed | peri.tr_io_output[65]:0 | ACT #1 |

scb4.uart.tx | ACT #4 | scb4.spi.select0 | ACT #6 | |

peri.tr_io_input[13]:0 | ACT #14 | peri.tr_io_output[13]:0 | ACT #15 | |

P4.0 | peri.tr_io_output[50]:0 | ACT #0 | tcpwm0.g1.cnt4+ | ACT #1 |

scb4.uart.cts | ACT #4 | scb4.spi.mosi | ACT #6 | |

peri.tr_io_input[14]:0 | ACT #14 | peri.tr_io_output[14]:0 | ACT #15 | |

P4.1 | peri.tr_io_output[51]:0 | ACT #0 | tcpwm0.g1.cnt4- | ACT #1 |

scb4.uart.rts | ACT #4 | scb4.spi.miso | ACT #6 | |

scb4.i2c.sda | ACT #7 | peri.tr_io_input[15]:0 | ACT #14 | |

peri.tr_io_output[15]:0 | ACT #15 | |||

P4.2 | peri.tr_io_output[52]:0 | ACT #0 | tcpwm0.g1.cnt5+ | ACT #1 |

scb4.uart.rx | ACT #4 | scb4.spi.clk | ACT #6 | |

scb4.i2c.scl | ACT #7 | peri.tr_io_input[16]:0 | ACT #14 | |

peri.tr_io_output[16]:0 | ACT #15 | |||

P4.3 | peri.tr_io_output[53]:0 | ACT #0 | tcpwm0.g1.cnt5- | ACT #1 |

scb4.uart.tx | ACT #4 | scb4.spi.select0 | ACT #6 | |

peri.tr_io_input[17]:0 | ACT #14 | peri.tr_io_output[17]:0 | ACT #15 | |

P4.4 | peri.tr_io_output[54]:0 | ACT #0 | tcpwm0.g1.cnt6+ | ACT #1 |

peri.tr_io_input[18]:0 | ACT #14 | peri.tr_io_output[18]:0 | ACT #15 | |

P4.5 | peri.tr_io_output[55]:0 | ACT #0 | tcpwm0.g1.cnt6- | ACT #1 |

peri.tr_io_input[19]:0 | ACT #14 | peri.tr_io_output[19]:0 | ACT #15 | |

P4.6 | peri.tr_io_output[56]:0 | ACT #0 | tcpwm0.g1.cnt7+ | ACT #1 |

peri.tr_io_input[20]:0 | ACT #14 | peri.tr_io_output[20]:0 | ACT #15 | |

P4.7 | peri.tr_io_output[57]:0 | ACT #0 | tcpwm0.g1.cnt7- | ACT #1 |

peri.tr_io_input[21]:0 | ACT #14 | peri.tr_io_output[21]:0 | ACT #15 | |

P5.0 | smartio5.io0 | fixed | peri.tr_io_output[62]:1 | ACT #1 |

scb3.uart.cts | ACT #4 | scb3.spi.mosi | ACT #6 | |

scb3.i2c.sda | ACT #7 | peri.tr_io_input[22]:0 | ACT #14 | |

peri.tr_io_output[22]:0 | ACT #15 | |||

P5.1 | smartio5.io1 | fixed | peri.tr_io_output[63]:1 | ACT #1 |

scb3.uart.rts | ACT #4 | scb3.spi.miso | ACT #6 | |

scb3.i2c.scl | ACT #7 | peri.tr_io_input[23]:0 | ACT #14 | |

peri.tr_io_output[23]:0 | ACT #15 | |||

P5.2 | smartio5.io2 | fixed | peri.tr_io_output[64]:1 | ACT #1 |

can1.rx | ACT #3 | scb3.uart.rx | ACT #4 | |

scb3.spi.clk | ACT #6 | peri.tr_io_input[24]:0 | ACT #14 | |

peri.tr_io_output[24]:0 | ACT #15 | |||

P5.3 | smartio5.io3 | fixed | peri.tr_io_output[65]:1 | ACT #1 |

can1.tx | ACT #3 | scb3.uart.tx | ACT #4 | |

scb3.spi.select0 | ACT #6 | peri.tr_io_input[25]:0 | ACT #14 | |

peri.tr_io_output[25]:0 | ACT #15 | |||

P6.0 | smartio6.io0 | fixed | tcpwm0.g1.cnt4+ | ACT #1 |

peri.tr_io_output[66]:0 | ACT #2 | scb3.uart.cts | ACT #4 | |

scb3.spi.mosi | ACT #6 | scb3.i2c.sda | ACT #7 | |

peri.tr_io_input[26]:0 | ACT #14 | peri.tr_io_output[26]:0 | ACT #15 | |

P6.1 | smartio6.io1 | fixed | tcpwm0.g1.cnt4- | ACT #1 |

peri.tr_io_output[67]:0 | ACT #2 | scb3.uart.rts | ACT #4 | |

scb3.spi.miso | ACT #6 | scb3.i2c.scl | ACT #7 | |

peri.tr_io_input[27]:0 | ACT #14 | peri.tr_io_output[27]:0 | ACT #15 | |

P6.2 | smartio6.io2 | fixed | tcpwm0.g1.cnt5+ | ACT #1 |

peri.tr_io_output[68]:0 | ACT #2 | can1.rx | ACT #3 | |

scb3.uart.rx | ACT #4 | scb3.spi.clk | ACT #6 | |

peri.tr_io_input[28]:0 | ACT #14 | peri.tr_io_output[28]:0 | ACT #15 | |

P6.3 | smartio6.io3 | fixed | tcpwm0.g1.cnt5- | ACT #1 |

peri.tr_io_output[69]:0 | ACT #2 | can1.tx | ACT #3 | |

scb3.uart.tx | ACT #4 | scb3.spi.select0 | ACT #6 | |

cpuss.fault[0]:1 | ACT #9 | peri.tr_io_input[29]:0 | ACT #14 | |

peri.tr_io_output[29]:0 | ACT #15 | |||

P7.0 | peri.tr_io_output[50]:1 | ACT #0 | tcpwm0.g1.cnt6+ | ACT #1 |

peri.tr_io_output[70]:0 | ACT #2 | scb2.uart.cts | ACT #4 | |

scb2.spi.clk | ACT #5 | scb2.i2c.scl | ACT #7 | |

trace.data0 | ACT #9 | hppass.gpio_out0 | ACT #12 | |

peri.tr_io_input[30]:0 | ACT #14 | peri.tr_io_output[30]:0 | ACT #15 | |

P7.1 | peri.tr_io_output[51]:1 | ACT #0 | tcpwm0.g1.cnt6- | ACT #1 |

peri.tr_io_output[71]:0 | ACT #2 | scb2.uart.tx | ACT #4 | |

scb2.spi.mosi | ACT #5 | scb2.i2c.sda | ACT #7 | |

trace.data1 | ACT #9 | hppass.gpio_out1 | ACT #12 | |

peri.tr_io_input[31]:0 | ACT #14 | peri.tr_io_output[31]:0 | ACT #15 | |

P7.2 | peri.tr_io_output[52]:1 | ACT #0 | tcpwm0.g1.cnt7+ | ACT #1 |

peri.tr_io_output[72]:0 | ACT #2 | scb2.uart.rx | ACT #4 | |

scb2.spi.miso | ACT #5 | trace.data2 | ACT #9 | |

hppass.gpio_out2 | ACT #12 | peri.tr_io_input[32]:0 | ACT #14 | |

peri.tr_io_output[32]:0 | ACT #15 | |||

P7.3 | peri.tr_io_output[53]:1 | ACT #0 | tcpwm0.g1.cnt7- | ACT #1 |

peri.tr_io_output[73]:0 | ACT #2 | scb2.uart.rts | ACT #4 | |

scb2.spi.select0 | ACT #5 | trace.data3 | ACT #9 | |

hppass.gpio_out3 | ACT #12 | peri.tr_io_input[33]:0 | ACT #14 | |

peri.tr_io_output[33]:0 | ACT #15 | |||

P7.4 | peri.tr_io_output[54]:1 | ACT #0 | scb2.spi.select1 | ACT #5 |

trace.clock | ACT #9 | hppass.gpio_out4 | ACT #12 | |

peri.tr_io_input[34]:0 | ACT #14 | peri.tr_io_output[34]:0 | ACT #15 | |

P7.5 | peri.tr_io_output[55]:1 | ACT #0 | scb2.spi.select2 | ACT #5 |

peri.tr_io_input[35]:0 | ACT #14 | peri.tr_io_output[35]:0 | ACT #15 | |

P7.6 | peri.tr_io_output[56]:1 | ACT #0 | peri.tr_io_input[36]:0 | ACT #14 |

peri.tr_io_output[36]:0 | ACT #15 | |||

P7.7 | peri.tr_io_output[57]:1 | ACT #0 | peri.tr_io_input[37]:0 | ACT #14 |

peri.tr_io_output[37]:0 | ACT #15 | |||

P8.0 | lpcomp0.in+ | fixed | hppass.gpio_00_aio | fixed |

peri.tr_io_output[62]:2 | ACT #1 | tcpwm0.g2.cnt4+ | ACT #2 | |

scb5.uart.cts | ACT #4 | scb5.spi.select0 | ACT #5 | |

trace.data0 | ACT #9 | hppass.gpio_out0 | ACT #12 | |

peri.tr_io_input[38]:0 | ACT #14 | peri.tr_io_output[38]:0 | ACT #15 | |

swj.trstn | DS #5 | |||

P8.1 | lpcomp0.in- | fixed | peri.tr_io_output[63]:2 | ACT #1 |

tcpwm0.g2.cnt4- | ACT #2 | scb5.uart.rx | ACT #4 | |

scb5.spi.mosi | ACT #5 | scb5.i2c.scl | ACT #7 | |

trace.data1 | ACT #9 | hppass.gpio_out1 | ACT #12 | |

peri.tr_io_input[39]:0 | ACT #14 | peri.tr_io_output[39]:0 | ACT #15 | |

P8.2 | lpcomp1.in+ | fixed | hppass.gpio_01_aio | fixed |

peri.tr_io_output[64]:2 | ACT #1 | tcpwm0.g2.cnt5+ | ACT #2 | |

can0.rx | ACT #3 | scb5.uart.rts | ACT #4 | |

scb5.spi.miso | ACT #5 | trace.data2 | ACT #9 | |

hppass.gpio_out2 | ACT #12 | peri.tr_io_input[40]:0 | ACT #14 | |

peri.tr_io_output[40]:0 | ACT #15 | |||

P8.3 | lpcomp1.in- | fixed | peri.tr_io_output[65]:2 | ACT #1 |

tcpwm0.g2.cnt5- | ACT #2 | can0.tx | ACT #3 | |

scb5.uart.tx | ACT #4 | scb5.spi.clk | ACT #5 | |

scb5.i2c.sda | ACT #7 | trace.data3 | ACT #9 | |

hppass.gpio_out3 | ACT #12 | peri.tr_io_input[41]:0 | ACT #14 | |

peri.tr_io_output[41]:0 | ACT #15 | |||

P8.4 | scb5.spi.select1 | ACT #5 | peri.tr_io_input[42]:0 | ACT #14 |

peri.tr_io_output[42]:0 | ACT #15 | |||

P8.5 | scb5.spi.select2 | ACT #5 | peri.tr_io_input[43]:0 | ACT #14 |

peri.tr_io_output[43]:0 | ACT #15 | |||

P9.0 | hibernate_wakeup | fixed | smartio9.io0 | fixed |

tcpwm0.g2.cnt6+ | ACT #2 | scb0.spi.clk | DS #1 | |

scb0.uart.cts | DS #2 | scb0.i2c.scl | DS #3 | |

peri.tr_io_input[44]:0 | ACT #14 | peri.tr_io_output[44]:0 | ACT #15 | |

P9.1 | smartio9.io1 | fixed | tcpwm0.g2.cnt6- | ACT #2 |

scb0.spi.select0 | DS #1 | scb0.uart.rts | DS #2 | |

peri.tr_io_input[45]:0 | ACT #14 | peri.tr_io_output[45]:0 | ACT #15 | |

P9.2 | smartio9.io2 | fixed | tcpwm0.g2.cnt7+ | ACT #2 |

can0.rx | ACT #3 | scb0.spi.mosi | DS #1 | |

scb0.uart.rx | DS #2 | scb0.i2c.sda | DS #3 | |

trace.clock | ACT #9 | hppass.gpio_out4 | ACT #12 | |

peri.tr_io_input[46]:0 | ACT #14 | peri.tr_io_output[46]:0 | ACT #15 | |

P9.3 | smartio9.io3 | fixed | tcpwm0.g2.cnt7- | ACT #2 |

can0.tx | ACT #3 | scb0.spi.miso | DS #1 | |

scb0.uart.tx | DS #2 | cpuss.clk_fm_pump | ACT #8 | |

cpuss.fault[0]:0 | ACT #9 | peri.tr_io_input[47]:0 | ACT #14 | |

peri.tr_io_output[47]:0 | ACT #15 | |||

P9.4 | smartio9.io4 | fixed | scb0.spi.select1 | DS #1 |

peri.tr_io_input[48]:0 | ACT #14 | peri.tr_io_output[48]:0 | ACT #15 | |

P9.5 | vext_ref_reg | fixed | smartio9.io5 | fixed |

scb0.spi.select2 | DS #1 | peri.tr_io_input[49]:0 | ACT #14 | |

peri.tr_io_output[49]:0 | ACT #15 | |||

Function | GPIOs | Function | GPIOs | Function | GPIOs |

|---|---|---|---|---|---|

cal_wave | P2.1 | can0.rx | P8.2, P9.2 | can0.tx | P8.3, P9.3 |

can1.rx | P5.2, P6.2 | can1.tx | P5.3, P6.3 | cpuss.clk_fm_pump | P9.3 |

cpuss.fault[0]:0 | P9.3 | cpuss.fault[0]:1 | P6.3 | eco_in | P1.0 |

eco_out | P1.1 | ext_clk | P0.0, P2.2 | hibernate_wakeup | P2.0, P9.0 |

hppass.gpio_00_aio | P8.0 | hppass.gpio_01_aio | P8.2 | hppass.gpio_out0 | P7.0, P8.0 |

hppass.gpio_out1 | P7.1, P8.1 | hppass.gpio_out2 | P7.2, P8.2 | hppass.gpio_out3 | P7.3, P8.3 |

hppass.gpio_out4 | P7.4, P9.2 | lpcomp0.in+ | P8.0 | lpcomp0.in- | P8.1 |

lpcomp1.in+ | P8.2 | lpcomp1.in- | P8.3 | peri.tr_io_input[0]:0 | P0.0 |

peri.tr_io_input[10]:0 | P3.0 | peri.tr_io_input[11]:0 | P3.1 | peri.tr_io_input[12]:0 | P3.2 |

peri.tr_io_input[13]:0 | P3.3 | peri.tr_io_input[14]:0 | P4.0 | peri.tr_io_input[15]:0 | P4.1 |

peri.tr_io_input[16]:0 | P4.2 | peri.tr_io_input[17]:0 | P4.3 | peri.tr_io_input[18]:0 | P4.4 |

peri.tr_io_input[19]:0 | P4.5 | peri.tr_io_input[1]:0 | P0.1 | peri.tr_io_input[20]:0 | P4.6 |

peri.tr_io_input[21]:0 | P4.7 | peri.tr_io_input[22]:0 | P5.0 | peri.tr_io_input[23]:0 | P5.1 |

peri.tr_io_input[24]:0 | P5.2 | peri.tr_io_input[25]:0 | P5.3 | peri.tr_io_input[26]:0 | P6.0 |

peri.tr_io_input[27]:0 | P6.1 | peri.tr_io_input[28]:0 | P6.2 | peri.tr_io_input[29]:0 | P6.3 |

peri.tr_io_input[2]:0 | P1.0 | peri.tr_io_input[30]:0 | P7.0 | peri.tr_io_input[31]:0 | P7.1 |

peri.tr_io_input[32]:0 | P7.2 | peri.tr_io_input[33]:0 | P7.3 | peri.tr_io_input[34]:0 | P7.4 |

peri.tr_io_input[35]:0 | P7.5 | peri.tr_io_input[36]:0 | P7.6 | peri.tr_io_input[37]:0 | P7.7 |

peri.tr_io_input[38]:0 | P8.0 | peri.tr_io_input[39]:0 | P8.1 | peri.tr_io_input[3]:0 | P1.1 |

peri.tr_io_input[40]:0 | P8.2 | peri.tr_io_input[41]:0 | P8.3 | peri.tr_io_input[42]:0 | P8.4 |

peri.tr_io_input[43]:0 | P8.5 | peri.tr_io_input[44]:0 | P9.0 | peri.tr_io_input[45]:0 | P9.1 |

peri.tr_io_input[46]:0 | P9.2 | peri.tr_io_input[47]:0 | P9.3 | peri.tr_io_input[48]:0 | P9.4 |

peri.tr_io_input[49]:0 | P9.5 | peri.tr_io_input[4]:0 | P1.2 | peri.tr_io_input[5]:0 | P1.3 |

peri.tr_io_input[6]:0 | P2.0 | peri.tr_io_input[7]:0 | P2.1 | peri.tr_io_input[8]:0 | P2.2 |

peri.tr_io_input[9]:0 | P2.3 | peri.tr_io_output[0]:0 | P0.0 | peri.tr_io_output[10]:0 | P3.0 |

peri.tr_io_output[11]:0 | P3.1 | peri.tr_io_output[12]:0 | P3.2 | peri.tr_io_output[13]:0 | P3.3 |

peri.tr_io_output[14]:0 | P4.0 | peri.tr_io_output[15]:0 | P4.1 | peri.tr_io_output[16]:0 | P4.2 |

peri.tr_io_output[17]:0 | P4.3 | peri.tr_io_output[18]:0 | P4.4 | peri.tr_io_output[19]:0 | P4.5 |

peri.tr_io_output[1]:0 | P0.1 | peri.tr_io_output[20]:0 | P4.6 | peri.tr_io_output[21]:0 | P4.7 |

peri.tr_io_output[22]:0 | P5.0 | peri.tr_io_output[23]:0 | P5.1 | peri.tr_io_output[24]:0 | P5.2 |

peri.tr_io_output[25]:0 | P5.3 | peri.tr_io_output[26]:0 | P6.0 | peri.tr_io_output[27]:0 | P6.1 |

peri.tr_io_output[28]:0 | P6.2 | peri.tr_io_output[29]:0 | P6.3 | peri.tr_io_output[2]:0 | P1.0 |

peri.tr_io_output[30]:0 | P7.0 | peri.tr_io_output[31]:0 | P7.1 | peri.tr_io_output[32]:0 | P7.2 |

peri.tr_io_output[33]:0 | P7.3 | peri.tr_io_output[34]:0 | P7.4 | peri.tr_io_output[35]:0 | P7.5 |

peri.tr_io_output[36]:0 | P7.6 | peri.tr_io_output[37]:0 | P7.7 | peri.tr_io_output[38]:0 | P8.0 |

peri.tr_io_output[39]:0 | P8.1 | peri.tr_io_output[3]:0 | P1.1 | peri.tr_io_output[40]:0 | P8.2 |

peri.tr_io_output[41]:0 | P8.3 | peri.tr_io_output[42]:0 | P8.4 | peri.tr_io_output[43]:0 | P8.5 |

peri.tr_io_output[44]:0 | P9.0 | peri.tr_io_output[45]:0 | P9.1 | peri.tr_io_output[46]:0 | P9.2 |

peri.tr_io_output[47]:0 | P9.3 | peri.tr_io_output[48]:0 | P9.4 | peri.tr_io_output[49]:0 | P9.5 |

peri.tr_io_output[4]:0 | P1.2 | peri.tr_io_output[50]:0 | P4.0 | peri.tr_io_output[50]:1 | P7.0 |

peri.tr_io_output[51]:0 | P4.1 | peri.tr_io_output[51]:1 | P7.1 | peri.tr_io_output[52]:0 | P4.2 |

peri.tr_io_output[52]:1 | P7.2 | peri.tr_io_output[53]:0 | P4.3 | peri.tr_io_output[53]:1 | P7.3 |

peri.tr_io_output[54]:0 | P4.4 | peri.tr_io_output[54]:1 | P7.4 | peri.tr_io_output[55]:0 | P4.5 |

peri.tr_io_output[55]:1 | P7.5 | peri.tr_io_output[56]:0 | P4.6 | peri.tr_io_output[56]:1 | P7.6 |

peri.tr_io_output[57]:0 | P4.7 | peri.tr_io_output[57]:1 | P7.7 | peri.tr_io_output[58]:0 | P2.0 |

peri.tr_io_output[58]:1 | P1.0 | peri.tr_io_output[59]:0 | P2.1 | peri.tr_io_output[59]:1 | P1.1 |

peri.tr_io_output[5]:0 | P1.3 | peri.tr_io_output[60]:0 | P2.2 | peri.tr_io_output[60]:1 | P1.2 |

peri.tr_io_output[61]:0 | P2.3 | peri.tr_io_output[61]:1 | P1.3 | peri.tr_io_output[62]:0 | P3.0 |

peri.tr_io_output[62]:1 | P5.0 | peri.tr_io_output[62]:2 | P8.0 | peri.tr_io_output[63]:0 | P3.1 |

peri.tr_io_output[63]:1 | P5.1 | peri.tr_io_output[63]:2 | P8.1 | peri.tr_io_output[64]:0 | P3.2 |

peri.tr_io_output[64]:1 | P5.2 | peri.tr_io_output[64]:2 | P8.2 | peri.tr_io_output[65]:0 | P3.3 |

peri.tr_io_output[65]:1 | P5.3 | peri.tr_io_output[65]:2 | P8.3 | peri.tr_io_output[66]:0 | P6.0 |

peri.tr_io_output[67]:0 | P6.1 | peri.tr_io_output[68]:0 | P6.2 | peri.tr_io_output[69]:0 | P6.3 |

peri.tr_io_output[6]:0 | P2.0 | peri.tr_io_output[70]:0 | P7.0 | peri.tr_io_output[70]:1 | P1.0 |

peri.tr_io_output[71]:0 | P7.1 | peri.tr_io_output[71]:1 | P1.1 | peri.tr_io_output[72]:0 | P7.2 |

peri.tr_io_output[72]:1 | P1.2 | peri.tr_io_output[73]:0 | P7.3 | peri.tr_io_output[73]:1 | P1.3 |

peri.tr_io_output[7]:0 | P2.1 | peri.tr_io_output[8]:0 | P2.2 | peri.tr_io_output[9]:0 | P2.3 |

scb0.i2c.scl | P9.0 | scb0.i2c.sda | P9.2 | scb0.spi.clk | P9.0 |

scb0.spi.miso | P9.3 | scb0.spi.mosi | P9.2 | scb0.spi.select0 | P9.1 |

scb0.spi.select1 | P9.4 | scb0.spi.select2 | P9.5 | scb0.uart.cts | P9.0 |

scb0.uart.rts | P9.1 | scb0.uart.rx | P9.2 | scb0.uart.tx | P9.3 |

scb1.i2c.scl | P1.3, P2.1 | scb1.i2c.sda | P1.2, P2.2 | scb1.spi.clk | P1.1, P2.1 |

scb1.spi.miso | P1.3, P2.3 | scb1.spi.mosi | P1.2, P2.2 | scb1.spi.select0 | P1.0, P2.0 |

scb1.uart.cts | P1.0, P2.0 | scb1.uart.rts | P1.1, P2.1 | scb1.uart.rx | P1.2, P2.2 |

scb1.uart.tx | P1.3, P2.3 | scb2.i2c.scl | P7.0 | scb2.i2c.sda | P7.1 |

scb2.spi.clk | P7.0 | scb2.spi.miso | P7.2 | scb2.spi.mosi | P7.1 |

scb2.spi.select0 | P7.3 | scb2.spi.select1 | P7.4 | scb2.spi.select2 | P7.5 |

scb2.uart.cts | P7.0 | scb2.uart.rts | P7.3 | scb2.uart.rx | P7.2 |

scb2.uart.tx | P7.1 | scb3.i2c.scl | P5.1, P6.1 | scb3.i2c.sda | P5.0, P6.0 |

scb3.spi.clk | P5.2, P6.2 | scb3.spi.miso | P5.1, P6.1 | scb3.spi.mosi | P5.0, P6.0 |

scb3.spi.select0 | P5.3, P6.3 | scb3.uart.cts | P5.0, P6.0 | scb3.uart.rts | P5.1, P6.1 |

scb3.uart.rx | P5.2, P6.2 | scb3.uart.tx | P5.3, P6.3 | scb4.i2c.scl | P3.2, P4.2 |

scb4.i2c.sda | P3.1, P4.1 | scb4.spi.clk | P3.2, P4.2 | scb4.spi.miso | P3.1, P4.1 |

scb4.spi.mosi | P3.0, P4.0 | scb4.spi.select0 | P3.3, P4.3 | scb4.uart.cts | P3.0, P4.0 |

scb4.uart.rts | P3.1, P4.1 | scb4.uart.rx | P3.2, P4.2 | scb4.uart.tx | P3.3, P4.3 |

scb5.i2c.scl | P8.1 | scb5.i2c.sda | P8.3 | scb5.spi.clk | P8.3 |

scb5.spi.miso | P8.2 | scb5.spi.mosi | P8.1 | scb5.spi.select0 | P8.0 |

scb5.spi.select1 | P8.4 | scb5.spi.select2 | P8.5 | scb5.uart.cts | P8.0 |

scb5.uart.rts | P8.2 | scb5.uart.rx | P8.1 | scb5.uart.tx | P8.3 |

smartio0.io0 | P0.0 | smartio0.io1 | P0.1 | smartio1.io0 | P1.0 |

smartio1.io1 | P1.1 | smartio1.io2 | P1.2 | smartio1.io3 | P1.3 |

smartio2.io0 | P2.0 | smartio2.io1 | P2.1 | smartio2.io2 | P2.2 |

smartio2.io3 | P2.3 | smartio3.io0 | P3.0 | smartio3.io1 | P3.1 |

smartio3.io2 | P3.2 | smartio3.io3 | P3.3 | smartio5.io0 | P5.0 |

smartio5.io1 | P5.1 | smartio5.io2 | P5.2 | smartio5.io3 | P5.3 |

smartio6.io0 | P6.0 | smartio6.io1 | P6.1 | smartio6.io2 | P6.2 |

smartio6.io3 | P6.3 | smartio9.io0 | P9.0 | smartio9.io1 | P9.1 |

smartio9.io2 | P9.2 | smartio9.io3 | P9.3 | smartio9.io4 | P9.4 |

smartio9.io5 | P9.5 | swj.swclk/tclk | P1.2 | swj.swdio/tms | P1.3 |

swj.tdi | P2.0 | swj.tdo | P2.1 | swj.trstn | P8.0 |

tcpwm0.g1.cnt4+ | P4.0, P6.0 | tcpwm0.g1.cnt4- | P4.1, P6.1 | tcpwm0.g1.cnt5+ | P4.2, P6.2 |

tcpwm0.g1.cnt5- | P4.3, P6.3 | tcpwm0.g1.cnt6+ | P4.4, P7.0 | tcpwm0.g1.cnt6- | P4.5, P7.1 |

tcpwm0.g1.cnt7+ | P4.6, P7.2 | tcpwm0.g1.cnt7- | P4.7, P7.3 | tcpwm0.g2.cnt4+ | P8.0 |

tcpwm0.g2.cnt4- | P8.1 | tcpwm0.g2.cnt5+ | P8.2 | tcpwm0.g2.cnt5- | P8.3 |

tcpwm0.g2.cnt6+ | P2.0, P9.0 | tcpwm0.g2.cnt6- | P2.1, P9.1 | tcpwm0.g2.cnt7+ | P2.2, P9.2 |

tcpwm0.g2.cnt7- | P2.3, P9.3 | trace.clock | P7.4, P9.2 | trace.data0 | P7.0, P8.0 |

trace.data1 | P7.1, P8.1 | trace.data2 | P7.2, P8.2 | trace.data3 | P7.3, P8.3 |

vext_ref_reg | P9.5 | wco_in | P0.1 | wco_out | P0.0 |

The peri.tr_io_input[n] and peri.tr_io_output[n] provide one more level of trigger and signal routing option between the peripherals and the GPIO pins using the high-speed I/O matrix (HSIOM). The peri.tr_io_input[n] allows a GPIO pin to be used as peripheral trigger input source (external trigger). Similarly, the peri.tr_io_output[n] can be used to route peripheral triggers and some signals like TCPWM line_out and line_compl_out to a GPIO pin. For more information refer to the Trigger MUX connection tables in section 10.3 of the PSOC™ Control C3 architecture reference manual.

Electrical specifications

Absolute maximum ratings

Spec ID | Parameter | Symbol | Values | Unit | Note or test condition | ||

|---|---|---|---|---|---|---|---|

Min. | Typ. | Max. | |||||

SID1 | Analog or Digital Supply relative to Vss (Vssd=Vssa) | VDD_ABS | -0.5 | - | 4 | V | Absolute Maximum |

SID2 | Direct digital core voltage input relative to Vssd | VCCD_ABS | -0.5 | - | 1.2 | V | Absolute Maximum |

SID3 | GPIO voltage ; VDDD or VDDA | VGPIO_ABS | -0.5 | - | VDD+0.5 | V | Absolute Maximum |

SID4 | Current per GPIO | IGPIO_ABS | -25 | - | 25 | mA | Absolute Maximum |

SID5 | GPIO injection current per pin | IGPIO_injection | -0.5 | - | 0.5 | mA | Absolute Maximum |

SID3A | Electrostatic discharge Human Body Model | ESD_HBM | 2000 | - | - | V | Absolute Maximum |

SID4A | Electrostatic discharge Charged Device Model | ESD_CDM | 500 | - | - | V | Absolute Maximum |

SID5A | Pin current for latchup free operation | LU | -100 | - | 100 | mA | Absolute Maximum |

SIDWA8 | Maximum undershoot voltage for I/O | Vundershoot | - | - | -0.5 | V | Duration not to exceed 25% of the duty cycle |

SIDWA9 | Maximum overshoot voltage for I/O | Vovershoot | - | - | VDDIO + 0.5 | V | Duration not to exceed 25% of the duty cycle |

SIDWA10 | Maximum junction temperature | Tj | - | - | 125 | °C | |

Device level specifications

Power supplies

Spec ID | Parameter | Symbol | Values | Unit | Note or test condition | ||

|---|---|---|---|---|---|---|---|

Min. | Typ. | Max. | |||||

| DC Specifications | |||||||

SID6 | Internal Regulator | VDDD | 1.71 | - | 3.6 | V | |

SID7B | GPIO Supply for Ports 1, 2, 3, 4, 5, 6, 7 | VDDIO_0 | 1.71 | - | 3.6 | V | |

SID7EP | E-Fuse Programming time | EFUSETIME | - | - | 5.5 | μs | Switch on time of 0.5us included |

SID7C | GPIO Supply for Ports 8 and 9 | VDDIO_1 | 1.71 | - | 3.6 | V | |

SID7A | Analog power supply for ADC and Comparator | VDDA | 1.71 | - | 3.6 | V | |

SID6B | Backup Power; normally shorted to VDDD (supply PORT 0) | VBACKUP | 1.71 | - | 3.6 | V | Min. is 1.4 V in Backup mode |

SID8 | Output voltage (for core logic bypass) | VCCD (OD) | - | 1.2 | - | V | Over drive mode |

SID8A | Output voltage (for core logic bypass) | VCCD (LP) | - | 1.1 | - | V | High-speed mode |

SID8B | Output voltage (for core logic bypass) | VCCD (MF) | - | 1 | - | ULP mode. Valid for -20 to 125°C. | |

SID8C | Output voltage (for core logic bypass) | VCCD (ULP) | - | 0.9 | - | ULP mode. Valid for -20 to 125°C. | |

SID10 | External Regulator voltage (VCCD) bypass | CEFC | 3.76 | 4.7 | 5.6 | µF | X5R ceramic or better. Value for 0.8 to 1.1 V. |

SID11 | Power supply decoupling capacitor | CEXC | - | 10 | - | µF | X5R ceramic or better |

Deep Sleep Mode | |||||||

SIDDS1 | With internal LDO enabled and no SRAM retention | IDD33 | - | 6 | 8 | µA | Max value is at 85°C (not including analog leakage on VDDA and VAREF_EXT) |

SIDDS1_A | With internal LDO enabled and 64K SRAM retention | IDD33A | - | 7 | 11 | µA | Max value is at 85°C (not including analog leakage on VDDA and VAREF_EXT) |

| Hibernate Mode | |||||||

SIDHIB1 | VDDD = 1.8 V | IDD34 | - | 300 | - | nA | No clocks running (not including analog leakage on VDDA and VAREF_EXT) |

SIDHIB2 | VDDD = 3.3 V | IDD34A | - | 500 | - | nA | No clocks running (not including analog leakage on VDDA and VAREF_EXT) |

SIDHIB3 | VDDD = 1.8 V | IDD35 | - | 800 | - | nA | WCO is running, lpcomp active (not including analog leakage on VDDA and VAREF_EXT) |

SIDHIB4 | VDDD = 3.3 V | IDD35A | - | 1000 | - | nA | WCO is running, lpcomp active (not including analog leakage on VDDA and VAREF_EXT) |

SIDHIB5 | Leakage on analog supply and analog reference in hibernate mode | IDDA | - | 100 | - | nA | Typical silicon and typical temperature |

CPU currents and transition times

Spec ID | Parameter | Symbol | Values | Unit | Note or test condition | ||

|---|---|---|---|---|---|---|---|

Min. | Typ. | Max. | |||||

| Cortex® M33. Active Mode | |||||||

SIDC2 | Execute from Cache;CM33 Active 180 MHz. PLL. Dhrystone. OD mode | IDD4 | - | 25 | 45 | mA | VDDD=3.3 V, Max at 125°C |

SIDC2A | Execute from Cache;CM33 Active 180 MHz. PLL. Dhrystone. OD mode | IDD4A | - | 25 | 45 | mA | VDDD=1.8 V, Max at 125°C |

SIDC3 | Execute from Cache;CM33 Active 150 MHz. PLL. Dhrystone. LP Mode | IDD5 | - | 18 | 35 | mA | VDDD=3.3 V, Max at 125°C |

SIDC3A | Execute from Cache;CM33 Active 150 MHz. PLL. Dhrystone. LP Mode | IDD5A | - | 18 | 35 | mA | VDDD=1.8 V, Max at 125°C |

SIDC4 | Execute from Cache;CM33 Active 70 MHz. PLL. Dhrystone. MF Mode | IDD6 | - | 12 | 27 | mA | VDDD=3.3 V, Max at 125°C |

SIDC4A | Execute from Cache;CM33 Active 70 MHz. PLL. Dhrystone. MF Mode | IDD6A | - | 12 | 27 | mA | VDDD=1.8 V, Max at 125°C |

SIDC5 | Execute from Cache;CM33 Active 50 MHz. PLL. Dhrystone. ULP Mode | IDD7 | - | 7 | 18 | mA | VDDD=3.3 V, Max at 125°C |

SIDC5A | Execute from Cache;CM33 Active 50 MHz. PLL. Dhrystone. ULP Mode | IDD7A | - | 7 | 18 | mA | VDDD=1.8 V, Max at 125°C |

| Cortex® M33 Sleep Mode | |||||||

SIDS1 | CM33 Sleep 180 MHz. PLL. OD Mode | IDD11 | - | 10 | 15 | mA | VDDD=3.3 V, Max at 105°C |

SIDS1A | CM33 Sleep 180 MHz. PLL. OD Mode | IDD11A | - | 10 | 15 | mA | VDDD=1.8 V, Max at 105°C |

SIDS2 | CM33 Sleep 150 MHz. PLL. LP Mode | IDD12 | - | 7 | 11 | mA | VDDD=3.3 V, Max at 105°C |

SIDS2A | CM33 Sleep 150 MHz. PLL. LP Mode | IDD12A | - | 7.0 | 11 | mA | VDDD=1.8 V, Max at 105°C |

SIDS3 | CM33 Sleep 70 MHz. PLL. MF Mode | IDD13 | - | 4.5 | 10 | mA | VDDD=3.3 V, Max at 105°C |

SIDS3A | CM33 Sleep 70 MHz. PLL. MF Mode | IDD13A | - | 4.5 | 10 | mA | VDDD=1.8 V, Max at 105°C |

SIDS4 | CM33 Sleep 50 MHz. PLL. ULP Mode | IDD14 | - | 4 | 9 | mA | VDDD=3.3 V, Max at 105°C |

SIDS4A | CM33 Sleep 50 MHz. PLL. ULP Mode | IDD14A | - | 4 | 9 | mA | VDDD=1.8 V, Max at 105°C |

| Boot Time | |||||||

SIDBT1 | Boot time after reset | BTIME | - | - | 3000000 | cycles | Refer to CPU clock cycles |

| Power Mode Transition Times | |||||||

SID13A | Deep Sleep to Active transition time. | TDS_ACT | - | - | 45 | µs | DS to Active with 1.1 V operation |

SID13B | Deep Sleep to Active LP transition time | TDS_ACTLP | - | - | 26 | µs | DS to Active LP with 1.0 V operation |

SID13C | Deep Sleep-RAM to Active transition time | TDSR_ACT | - | - | 800 | µs | DS to Active with 1.1 V operation |

SID13D | Deep Sleep-RAM to Active LP transition time | TDSR_ACTULP | - | - | 800 | µs | DS-RAM to Active LP with 1.0 V operation |

SID14 | Hibernate to Active transition time | THIB_ACT | - | 2000 | - | µS | Including PLL lock time |

XRES

Spec ID | Parameter | Symbol | Values | Unit | Note or test condition | ||

|---|---|---|---|---|---|---|---|

Min. | Typ. | Max. | |||||

| XRES AC Specifications | |||||||

SID15 | POR or XRES release to Active transition time | TXRES_ACT | - | 2 | - | mS | With BOOT_OD_CLOCK=180MHz, LISTEN_WINDOW=9 and BOOT_SIMPLE_APP configuration |

SID16 | XRES Pulse width | TXRES_PW | 5 | - | - | µS | |

| XRES DC Specifications | |||||||

SID17 | IDD when XRES asserted | TXRES_IDD | - | 180 | - | nA | VDDD = 1.8 V |

SID17 | IDD when XRES asserted | TXRES_IDD_1 | - | 330 | - | nA | VDDD = 3.3 V |

SID77 | Input Voltage high threshold | VIH | 0.7*VDD | - | - | V | CMOS Input |

SID78 | Input Voltage low threshold | VIL | - | - | 0.3*VDD | V | CMOS Input |

SID80 | Input Capacitance | CIN | - | 3 | - | pF | XRES resistor removed |

SID81 | Input voltage hysteresis | VHYSXRES | - | 100 | - | mV | |

SID82 | Current through protection diode to VDD/Vss | IDIODE | - | - | 100 | µA | |

GPIO

Spec ID | Parameter | Symbol | Values | Unit | Note or test condition | ||

|---|---|---|---|---|---|---|---|

Min. | Typ. | Max. | |||||

| GPIO DC Specifications | |||||||

SID57 | Input Voltage high threshold | VIH | 0.7*VDD | - | - | V | CMOS Input |

SID58 | Input Voltage low threshold | VIL | - | - | 0.3*VDD | V | CMOS Input |

SID243 | LVTTL input, VDD >= 2.7 V | VIH | 2.0 | - | - | V | |

SID244 | LVTTL input, VDD >= 2.7 V | VIL | - | - | 0.8 | V | |

SID59 | Output Voltage high level | VOH | VDD-0.5 | - | - | V | Ioh = 6 mA |

SID62A | Output Voltage low level | VOL | - | - | 0.4 | V | Iol = 6 mA |

SID63 | Pull-up resistor | RPULLUP | 3.5 | 5.6 | 8.5 | kΩ | |

SID64 | Pull-down resistor | RPULLDOWN | 3.5 | 5.6 | 8.5 | kΩ | |

SID65 | Input leakage current(absolute value) | IIL | - | - | 2 | nA | 25°C, VDD = 3.0 V |

SID66 | Input Capacitance | CIN | - | - | 5 | pF | |

SID67 | Input hysteresis LVTTL VDD > 2.7 V | VHYSTTL | 100 | 0 | - | mV | |

SID68 | Input hysteresis CMOS | VHYSCMOS | 0.05*VDD | - | - | mV | |

SID69 | Current through protection diode to VDD/VSS | IDIODE | - | - | 100 | µA | |

SID69A | Maximum Total Source or Sink Chip Current | ITOT_GPIO | - | - | 200 | mA | |

| GPIO AC Specifications | |||||||

SID70 | Rise time in Fast Strong Mode. 10% to 90% of VDD | TRISEF | - | - | 2.5 | ns | Cload = 15 pF, 8 mA drive strength |

SID71 | Fall time in Fast Strong Mode. 10% to 90% of VDD. | TFALLF | - | - | 2.5 | ns | Cload = 15 pF, 8 mA drive strength |

SID72 | Rise time in Slow Strong Mode. 10% to 90% of VDD | TRISES_1 | - | - | 14.4 | ns | Cload = 15 pF, 8 mA drive strength, VDD < = 2.7 V |

SID72A | Rise time in Slow Strong Mode. 10% to 90% of VDD | TRISES_2 | - | - | 7.2 | ns | Cload = 15 pF, 8 mA drive strength, 2.7 V < VDD < = 3.6 |

SID73 | Fall time in Slow Strong Mode. 10% to 90% of VDD | TFALLS_1 | - | - | 14.4 | ns | Cload = 15 pF, 8 mA drive strength, VDD < = 2.7 V |

SID73A | Fall time in Slow Strong Mode. 10% to 90% of VDD | TFALLS_2 | - | - | 7.2 | ns | Cload = 15 pF, 8 mA drive strength, 2.7 V < VDD < = 3.6 |

SID73G | Fall time (30% to 70% of VDD) in Slow Strong mode | TFALL_I2C | 20*Vddio/5.5 | - | 250 | ns | Cload = 10 pF to 400 pF, 8 mA drive strength |

SID74 | GPIO Fout. Fast Strong mode. | FGPIOUT1 | - | - | 80 | MHz | 90/10%, 15 pF load, 60/40 duty cycle |

SID75 | GPIO Fout; Slow Strong mode. | FGPIOUT2 | - | - | 16.7 | MHz | 90/10%, 15 pF load, 60/40 duty cycle |

SID76 | GPIO Fout; Fast Strong mode. | FGPIOUT3 | - | - | 7 | MHz | 90/10%, 25 pF load, 60/40 duty cycle |

SID245 | GPIO Fout;Slow Strong mode. | FGPIOUT4 | - | - | 3.5 | MHz | 90/10%, 25 pF load, 60/40 duty cycle |

SID246 | GPIO input operating frequency;1.71 V < = VDD < = 3.6 V | FGPIOIN | - | - | 100 | MHz | 90/10% Vio |

Analog peripherals

Spec ID | Parameter | Symbol | Values | Unit | Note or test condition | ||

|---|---|---|---|---|---|---|---|

Min. | Typ. | Max. | |||||

| Analog Peripherals | |||||||

SIDAS1 | Leakage on single analog input pin | AIN_LEAK | - | 0.32 | 12 | nA | Maximum leakage at 125°C |

SIDAS2 | Input Capactiance of CSG | AIN_CAP_CSG | - | - | 1 | pF | Valid for VDDA >= 2.7 V |

SIDAS2A | Input Capactiance of ADC | AIN_CAP_ADC | - | - | 3 | pF | Valid for VDDA >= 2.7 V |