PSOC™ Control C3 architecture reference manual

Reference manual

About this document

Scope and purpose

This document provides comprehensive information about Infineon's

PSOC™ Control C3

series of microcontrollers. These 32-bit, single-core chips are part of a high-performance, low-power, and secure family of MCUs specifically designed for real-time control, enhanced sensing, secure, and low-power applications.

Intended audience

This document is intended for hardware engineers, embedded software developers, and system architects who want to understand the architecture of Infineon's

PSOC™ Control C3

series of microcontrollers.

Introduction

This document provides information about Infineon's

PSOC™ Control C3

series of microcontrollers designed for industrial applications. These microcontrollers feature an Arm® Cortex®-M33 CPU and integrated programmable peripherals. Specifically designed for real-time applications, they are manufactured using an advanced 40-nm process. Additionally, they offer a range of low-power modes, security features, a flexible clocking system, rich communication peripherals, advanced digital and analog peripherals, and compatibility with industry-standard development tools.

Detailed features

This device has the following features:

CPU subsystem

Arm® Cortex®-M33 running up to

180 MHz

Digital signal processor (DSP), floating-point unit (FPU), memory protection unit (MPU), 16 KB I-cache

Two direct memory access (DMA) controllers with 16 channels each

Security

Platform security architecture level 2 (PSA L2) certified

Step-wise authentication of execution images until the control is handed over to the user code

Secure execution of code in the execute-only mode for protected routines

Image authentication and integrity check

TrustZone framework that establishes an isolated device root of trust (RoT) for trust attestation and software management

Memory

On-chip flash with ECC support

Up to 256-KB flash with read while write (RWW) capability, 64 KB ROM for boot code, and bootloader functions

Built-in device firmware upgrade (DFU) support in boot ROM via serial interface (UART/I2C/SPI)

SRAM with ECC support

64 KB

full SRAM available in Deep Sleep

SRAM data path is protected with a hardware mechanism (ECC) for soft error detection and correction

Clocking subsystem

8 MHz IMO with Deep Sleep operation offering ±2% accuracy

48 MHz internal high-frequency oscillator (IHO) offering ±1% accuracy

32 kHz internal low frequency oscillator (ILO) offering ±10% accuracy

4 to 35 MHz external crystal oscillator (ECO) support

32.768 kHz external watch crystal oscillator (WCO) usable for real-time clock (RTC)

External clock (EXTCLK): Maximum frequency 80 MHz

One frequency lock loop (FLL) with 24-100 MHz output range

Two digital phase-locked loops, DPLL#0 and DPLL#1, with 25-250 MHz output range

Low power (1.71 V to 3.6 V) operation

Six power modes (Active, Sleep, Deep Sleep, Deep Sleep-RAM, Deep Sleep-OFF, and Hibernate) for fine-grained power management

Deep Sleep mode current of 11 µA at 3.3-V external supply using an internal voltage regulator with 64-KB SRAM retention, LPComp, and Deep Sleep SCB

Hibernate mode current with RTC and LPComp of up to 1000 nA

Communication peripherals

Serial communication blocks (SCBs)

Up to six independent run-time-reconfigurable SCBs; each is software-configurable as I2C, SPI, or UART in master or slave mode

One SCB also supports Deep Sleep operation and wake-up from Deep Sleep in I2C slave and SPI slave modes

One SCB has fast SPI support of up to 50 MHz

SCB supports single-wire half-duplex mode for UART

CAN FD

Up to two CAN FD channels with a single instance with operation of up to 8 Mbps

High-performance, programmable analog subsystem (HPPASS)

Analog-to-digital converter (ADC)

One 12-bit,

12-Msps

SAR ADC

Up to 16 dedicated analog pads, connected to up to 16 parallel sample stages

Two additional GPIOs can be used as analog inputs

Up to 16 sample/hold (S/H) circuits in SAR ADC connected to pins directly or through AMUX

One S/H circuit in SAR ADC is internally connected to analog references and a temperature sensor

Configurable input gain of 1, 3, 6, and 12 on all 16 S/H circuits

Digital comparator at the output to compare the ADC result against programmed boundary values

Digital comparator outputs can be connected to timer/counter pulse-width modulator (TCPWM) (low latency between the modules)

Analog comparators

Five Active comparators without Deep Sleep functionality, each with a 10-bit DAC to generate the comparator reference

Each comparator supports an external reference/threshold through pins

Active comparator can be used with the built-in DAC in Hysteresis mode

Two additional comparators in LPComp are available in Active/Deep Sleep/Hibernate modes

Comparator outputs can be brought to pins for control loop applications

Comparator outputs can be connected to TCPWM (low latency between the modules)

Logical OR of multiple comparator trigger outputs connected as an input trigger to TCPWM via trigger MUX

Real-time control peripherals

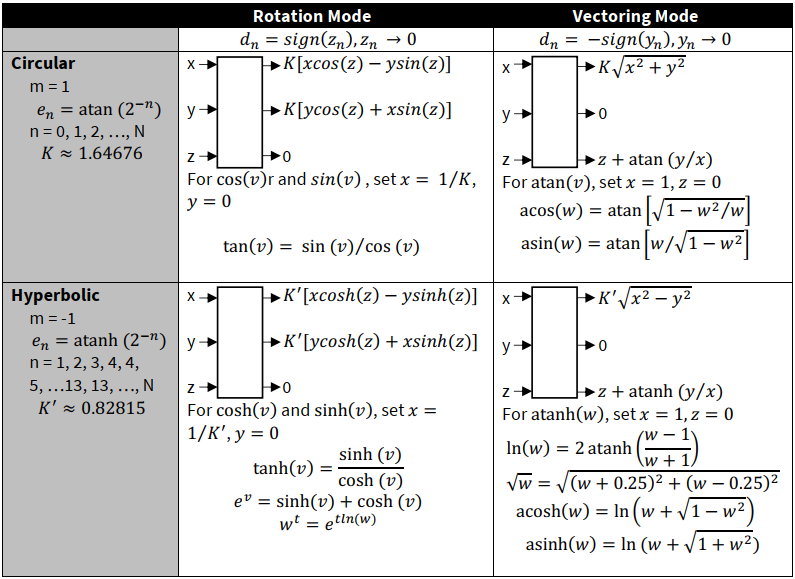

Coordinate rotation digital computer (CORDIC)

Supports all CORDIC operating modes for solving circular (trigonometric), hyperbolic functions, and integrated independent lookup tables to accelerate calculation

Timer/counter pulse-width modulator (TCPWM)

Sixteen 16-bit TCPWM channels

Four 32-bit TCPWM channels

supporting high-resolution PWM generation (HRPWM) for PWM outputs

Center-aligned, edge, and pseudorandom modes

Comparator-based triggering of kill signals

Shadow update of duty, period, dead-time, output signal polarity, and dithering (pseudorandom mode)

Multichannel control: In a group of eight TCPWM channels, one channel within a group can trigger another channel

Ability to logically combine the outputs of multiple channels through Smart I/O

Dedicated output triggers mux in a group to allow flexibility to the PWM channel as a trigger and/or gate signals to the HPPASS

Hall sensor interface with autonomous BLDC block commutation support

Quadrature encoder interface to decode motor speed and rotor position

HRPWM feature for period, duty, and dead-time insertion with a typical resolution of less than 80 ps

I/O subsystem

Programmable GPIO pins

Up to

66

functional pins (

50

digital GPIOs; 2 out of

50

GPIOs can be used for analog inputs + 16 dedicated analog-only inputs)

Programmable drive modes, strengths, and slew rates

Programmable digital

Up to

seven

Smart I/O capable ports (

I/Os, 56 LUTs) enable Boolean operations on I/O signals

Cryptography

Cryptography accelerator

Hardware acceleration for symmetric (AES-128) and asymmetric cryptographic algorithms (RSA and elliptic curve cryptography (ECC)) supported by vector unit (VU) and hash functions (SHA-256)

True random number generator (TRNG) function

Architecture

Figure 1.

Functional block diagram

Document organization and conventions

Major sections

The information in this reference manual is organized as follows:

Chapter – Presents the chapters specific to an individual aspect of the device. These are the detailed implementation and use information for some aspect of the integrated circuit

Registers summary – Summary of registers associated with the chapter

Registers Reference Manual - Supplies all device register details summarized in the reference manual. This is an additional document

Document conventions

Register conventions

Register conventions are detailed in the Registers Reference Manual.

Numeric naming

Hexadecimal numbers are represented with all letters in uppercase with an appended lowercase ‘h’ (for example, ‘14h’ or 3Ah) and hexadecimal numbers may also be represented by a ‘0x’ prefix, the C coding convention. Binary numbers have an appended lowercase ‘b’ (for example, 01010100b or 01000011b’). Numbers not indicated by an ‘h’ or ‘b’ are decimal.

Unit of measure

lists the units of measure used in this document.

Abbreviation | Unit of measure |

|---|---|

bps | bits per second |

°C | degrees Celsius |

dB | decibels |

dBm | decibels-milliwatts |

fF | femto farads |

G | Giga |

Hz | Hertz |

k | kilo, 1000 |

K | kilo, 2^10 |

KB | 1024 bytes, or approximately 1000 bytes |

Kbit | 1024 bits |

kHz | kilo Hertz (32.000) |

kΩ | kilo Ohms |

MHz | mega Hertz |

MΩ | mega Ohms |

µA | micro Amperes |

µF | micro Farads |

µs | micro seconds |

µV | micro volts |

µVrms | micro volts root-mean-square |

mA | milli amperes |

ms | milli seconds |

mV | milli Volts |

nA | nano Amperes |

ns | nano seconds |

nV | nano Volts |

Ω | ohms |

pF | pico Farads |

pp | peak-to-peak |

ppm | parts per million |

SPS | samples per second |

σ | sigma: one standard deviation |

V | Volts |

Acronyms

lists the acronyms and their definitions.

Acronym | Definition |

|---|---|

AC | Autonomous controller |

ACK | Acknowledge |

ADC | Analog-to-digital converter |

AES | Advanced Encryption Standard |

AF | Analog filter |

AHB | AMBA high-performance bus, an Arm® ® data transfer bus |

AIRCR | Application interrupt and reset Control Register |

AMBA | Advanced Microcontroller Bus Architecture |

ARB | Arbitration |

BGR | Band gap reference |

BOD | Brown-out detect |

CAN | Controller area network |

CAN-FD | Controller area network flexible data-rate |

CC0 | Capture/Compare0 |

CC1 | Capture/Compare1 |

CM-33 | Cortex® M33 |

CORDIC | Coordinate Rotation Digital Computer |

CPU | Central processing unit |

CPUSS | CPU subsystem |

CSG | Comparator and slope generator |

CSV | Cock supervision |

CTS | Clear to Send |

DAC | Digital-to-analog converter |

DAP | Debug access port |

DF | Digital filter |

DMA | Direct memory access |

DMAC | Direct memory access controller |

DPLL | Digital phase-locked loop |

DSI | Digital system interconnect |

DSP | Digital signal processing |

DU | Data unit |

DW | Data wire |

ECC | Error correcting code |

ECO | External crystal oscillator |

Em_EEPROM | Emulated Electrically Erasable Programmable Read-only Memory |

EOC | End of conversion |

EPPB | External private peripheral us |

FIFO | First in first out |

FIR | Finite impulse response |

FLL | Frequency locked loop |

FM | Flash macro |

FPU | Floating point unit |

FSM | Finite-state machine |

GPIO | General-purpose input output |

HPPASS | High-performance programmable analog subsystem |

HRPWM | High-resolution PWM |

HSIOM | High-speed I/O matrix |

I2C | Inter-integrated circuit |

I-Cache | Instruction cache |

ICER | Interrupt clear enable register |

IDAU | Implementation defined attribution unit |

IHO | Internal high-speed oscillator |

ILO | Internal low-speed oscillator |

IMO | Internal main oscillator |

INFRA | Infrastructure |

IOSS | I/O subsystem |

IPC | Inter processor communication |

IRQ | Interrupt request |

ISER | Interrupt set enable register |

ISR | Interrupt service routine |

ITNS | Interrupt target non-secure |

LCS | Life cycle stage |

LDO | Low dropout |

LFCLK | Low frequency clock |

LIN | Local interconnect network |

LP | Low power |

LPCOMP | Low-power comparator |

LUT | Look-up table |

LVD | Low-voltage detect |

MCU | Microcontroller unit |

MCWDT | Multi-counter watchdog timer |

MF | Medium frequency |

MISO | Master in slave out |

MMIO | Memory-mapped I/O |

MOSI | Master out slave in |

MOTIF | Motion interface |

MPC | Memory protection controller |

MPS | Magnitude PreScaler |

MPU | Memory protection unit |

MSC | Master security controller |

MSP | Main stack pointer |

MTQ | Minimum time quantum |

NACK | No acknowledgment |

NMI | Non-maskable interrupt |

NVIC | Nested vectored interrupt controller |

NVM | Nonvolatile memory |

OD | Overdrive |

OTP | One-time programmable |

OV | Over flow |

PC | Protection context |

PDL | Peripheral driver library |

PendSV | Pending supervisory |

PERI | Peripheral interconnect |

PID | Protected identifier |

PLL | Phase-locked loop |

POR | Power-on reset |

PPB | Private peripheral bus |

PPC | Peripheral protection controller |

PPU | Power policy unit |

PSP | Process stack pointer |

PSR | Program and status register |

PWM | Pulse width modulation |

PWMDT | Pulse width modulation with dead time insertion |

RAM | Random access memory |

RMA | Return merchandise authorization |

RTC | Real time clock |

RTS | Request to send |

RX | Receive |

SAR | Successive approximation register |

SAU | Secure attribution unit |

SCB | Serial communication block |

SCL | Serial clock |

SDA | Serial data |

SFR | Special function register |

SHA | Secure hash algorithm |

SoC | System on-chip |

SPI | Serial peripheral interface |

SRAM | Static random access memory |

SRAMC | Static random access memory controller |

SRSS | System resource subsystem |

SVCall | Supervisory call |

SWD | Single-wire debug |

TC | Terminal count |

TCPWM | Timer counter pulse width modulation |

TQ | Time quantum |

TRNG | True random number generator |

TX | Transmit |

UART | Universal asynchronous receiver/transmitter |

UART_MP | UART multi-processor |

ULP | Ultra low power |

UN | Underflow |

VTOR | Vector table offset register |

VU | Vector unit |

WCO | Watch crystal oscillator |

WDT | Watchdog timer |

WFE | Wait for event |

WFI | Wait for interrupt |

WIC | Wake-up interrupt controller |

WS | Wait states |

XRES | External reset |

CPU subsystem (CPUSS)

The CPU subsystem is based on the 32-bit Arm® Cortex®-M33 (CM33) CPU. It is designed for security, control, communication, short interrupt response time, high code density, and high 32-bit throughput while maintaining a strict cost and power consumption budget.

This section provides only an overview of the Arm Cortex® CPU in

PSOC™ Control C3

MCU. For details, see the Arm documentation sets for

cortex®-M33

.

Features

The

PSOC™ Control C3

MCU Arm® Cortex®-M33 (CM33) CPU has the following features:

Maximum clock frequency of 180 MHz @ over drive (OD) mode

Single-precision floating-point unit (FPU) and DSP extension

Memory protection unit (MPU) with up to 8 regions per security state (secure and non-secure)

Nested vectored interrupt controller (NVIC) integrated with the CPU core yielding low interrupt latency

Wakeup interrupt controller (WIC) that allows the CPU to wake up from the Deep Sleep power mode through Deep Sleep interrupts

16 KB instruction cache (I-cache) on Cortex®-M33 C-AHB bus with four-way set associativity

Supports TrustZone-M memory mapping for secure/non-secure aliasing based on programmable secure attribution unit (SAU) and a fixed implementation defined attribution unit (IDAU)

Architecture

CM33 is a 32-bit processor with a 32-bit data path, 32-bit registers, and a 32-bit memory interface. The CPU supports a wide variety of instructions in the thumb instruction set. The CM33 CPU supports thread and handler operating modes (refer to the

Operating modes and privilege levels

section). Additionally, the CM33 CPU supports secure and non-secure security states based on the security extension.

The CM33 instruction set includes:

Signed and unsigned, 32×32 -> 32-bit and 32×32 -> 64-bit, multiply and multiply accumulate, all single-cycle

Signed and unsigned 32-bit divides that take 2 to 11 cycles (depending on values)

DSP instructions

Complex memory load and store access

Complex bit manipulation

The CM33 processor with FPU supports single precision arithmetic as defined by the FPv5 architecture. This is compliant with the ANSI/IEEE Std 754-2008, IEEE standard for binary floating-point arithmetic.

CPUSS

The

PSOC™ Control C3

CPUSS is a security, control, and communication CPU that is built on a Cortex®-M33 (CM33) core and runs at up to 180 MHz.

The CM33 CPU is a 3-stage pipeline (3PIP) from Arm® based on the Arm® v8-M architecture having a low-power domain with rapid clock switching. The CPUSS implements Arm® TrustZone-M compatible security and protection infrastructure. It provides the initial boot for security and protection schemes.

The CM33 CPU is a TrustZone-M CPU that implements an inbuilt security extension. As part of the security extension, the CM33 implements a secure attribution unit (SAU) inside the CPU. The TrustZone-M architecture also defines an external interface to the CPU, which can be connected to an implementation defined attribution unit (IDAU)

For non-CPU masters in CPUSS, a master security controller (MSC) is instantiated along with an implementation defined attribution unit (IDAU) to distinguish secure/non-secure transfers. For more details, refer to the TrustZone section

The CPUSS has a 16 KB 4-way set associative instruction cache on the C-AHB bus. CPUSS supports on-chip SRAM controller and memories. It provides C-AHB bus access from SRAM for code execution. The CPUSS includes a 128-bit AHB5 bus interface for instruction fetch and data access from FLASH (NVM), as well as internal SRAMs, which are accessible on their aliased addresses. Also it supports a 32-bit AHB5 bus interface to access the memory-mapped Flash, internal SRAM present in the system memory map.

The CPUSS includes two DMA controllers supporting 16 channels with Arm® Q-channel support. These channels are primarily used to service the SCB, CORDIC, and TCPWM peripherals. The CPUSS includes four inter-processor communication (IPC) hardware for secure and non-secure applications to communicate and synchronize their activities.

The CPUSS has clk_hf0 clock domain for the majority of hardware modules.

clk_hf0: Up to 180 MHz @ 1.2 V. Used by majorities of the CPUSS including I-Cache, AHB bus infrastructures, DMA, MSC/IDAU/MPC, and all on-chip memory controllers running at a single synchronous frequency

The CPUSS implements a centralized fault reporting infrastructure (only a single fault interrupt handler is required), which captures faults related to (not an exclusive listing) MPC/PPC violations, peripheral-specific errors, memory controller-specific errors such as ECC errors, and time-out errors.

In CPUSS, the active power domain becomes active or initialized first (by default, following the power-on reset (POR)). Refer the device power modes section for more details.

Address and memory maps

The CPU has a fixed address map. The default memory map of the CPU covers the range 0x00000000 - 0xFFFFFFFF. For the default memory map, see the memory model section of

Arm® Cortex®-M33 Processor Technical Reference Manual

. This 32-bit (4GB) address space is further partitioned into non-secure and secure memory regions as shown in

Table 3

. Based on Arm® TrustZone, bit [28] of the address defines if a memory is secure or non-secure, resulting in the following memory map.

Access type | Address range | Subregion name | Bank mode | Size | Region name - interface |

|---|---|---|---|---|---|

Non-secure | 0x22000000 – 0x2203FFFF | Flash (NVM) | Single bank | 256 KB | SRAM region - S-bus |

Secure | 0x32000000 - 0x3203FFFF | 256 KB | |||

Non-secure | 0x02000000 - 0x0203FFFF | Single bank | 256 KB | Code region - C-bus | |

Secure | 0x12000000 - 0x1203FFFF | 256 KB | |||

Non-secure | 0x22000000 - 0x2201FFFF | Dual bank (Bank 0) | 128 KB | SRAM region - S-bus | |

0x22800000 - 0x2281FFFF | Dual bank (Bank 1) | 128 KB | |||

Secure | 0x32000000 - 0x3201FFFF | Dual bank (Bank 0) | 128 KB | ||

0x32800000 - 0x3281FFFF | Dual bank (Bank 1) | 128 KB | |||

Non-secure | 0x02000000 - 0x0201FFFF | Dual bank (Bank 0) | 128 KB | Code region - C-bus | |

0x02800000 - 0x0281FFFF | Dual bank (Bank 1) | 128 KB | |||

Secure | 0x12000000 - 0x1201FFFF | Dual bank (Bank 0) | 128 KB | ||

0x12800000 - 0x1281FFFF | Dual bank (Bank 1) | 128 KB | |||

Non-secure | 0x04000000 – 0x0400FFFF | SRAM | N/A | 64 KB | Code region - C-bus |

Secure | 0x14000000 – 0x1400FFFF | N/A | 64 KB | ||

Non-secure | 0x24000000 - 0x2400FFFF | N/A | 64 KB | SRAM region - S-bus | |

Secure | 0x34000000 - 0x3400FFFF | N/A | 64 KB | ||

Non-secure | 0x23400000 - 0x23407FFF | SFLASH | N/A | 32 KB | SRAM region - S-bus |

Secure | 0x33400000 - 0x33407FFF | N/A | 32 KB | SRAM region - S-bus | |

Non-secure | 0x03400000 - 0x03407FFF | N/A | 32 KB | Code region - C-bus | |

Secure | 0x13400000 - 0x13407FFF | N/A | 32 KB | Code region - C-bus | |

Non-secure | 0x00800000 – 0x0080FFFF | Reserved | N/A | 64 KB | ROM region |

Secure | 0x10800000 – 0x1080FFFF | N/A | 64 KB | ||

Non-secure | 0x42000000 - 0x43FFFFFF | SYSCPUSS peripheral (SYS MMIO) | N/A | 32 MB | Peripheral region |

Secure | 0x52000000 - 0x53FFFFFF | N/A | 32 MB |

Note:

Secure and non-secure memory pairs are the same physical memory but mapped differently depending on whether they are configured as secure or non-secure.

Gaps in the address space are reserved. Do not access these gaps; if accessed, it can result in hard faults or BUS ERROR depending on which bus segment or peripheral an address is allocated to. Coherency of caches during PC (protection context) switches are all maintained by the software. For CM33, all accessible address spaces in FLASH are cacheable.

All peripheral address spaces specified in 0x4000_0000/0x5000_0000 are NOT cacheable. The XIP execution instruction from this address space causes MemFault. Address aliasing only applies to SRAM when accessed by the CM33 processor via code bus to facilitate code execution out of SRAM memory.

Note:

The CM33_S_VECTOR_TABLE_BASE, CM33_NS_VECTOR_TABLE_BASE registers determine the location of the secure and non-secure vector table for the CM33 CPU.

Wait state lookup tables

The wait state lookup tables show the wait states for different memory modules.

Parameter | Symbol | Values | Note or test condition | ||

|---|---|---|---|---|---|

Min | Typ | Max | |||

Memory wait states | |||||

Wait states | M33 cache | - | - | 0 | |

Wait states from CM33 | M33 SRAM | - | 0 | 3 | Max is 3 with ECC enabled |

Wait states from flash via C-bus (cached) | M33 Flash | 3* | - | 9 | Depending on cache hit, pre-fetch and opcode |

Wait states from flash via S-bus | M33 Flash | - | - | 9 | |

Note:

The wait state lookup tables are applicable for all power modes (ULP/MF/LP/OD).

Note:

[*] M33

Flash

Min is 0 on cache hit

Operating modes and privilege levels

The CM33 CPU supports both secure and non-secure states. The CPU has thread and handler operating modes and can run in either thumb or debug operating states. In addition, the processor can limit or exclude access to some resources by executing code in privileged or unprivileged mode.

See the

Arm®v8-M Architecture Reference Manual

for more information about the modes of operation and execution.

Security states

When the Arm® v8‑M Security Extension is included in the processor, the programmer model includes two orthogonal security states: secure and non-secure. The CM33 CPU has a security extension enabled it always resets into the secure state.

Registers in the system control space are banked across secure and non-secure states and the non-secure register view is available at an aliased address to the secure state.

Operating modes

For each security state, the processor can operate in thread or handler mode.

Thread mode

: Used to execute application software. The processor enters the thread mode on reset, or as a result of an exception return to the thread mode. The thread mode includes privileged and unprivileged codes

Handler mode

: Used to handle exceptions. The processor enters the handler mode as a result of an exception. The handler mode includes only the privileged code

The processor can change the security state on taking an exception. For example, when a secure exception is taken from the non-secure state, the thread mode enters the secure state handler mode. The processor can also call secure functions from the non-secure state and non-secure functions from the secure state. The security extension includes requirements for these calls to prevent secure data from being accessed in the non-secure state.

Operating states

The processor can operate in the thumb or debug state:

The thumb state is the state of normal execution running 16-bit and 32-bit half-word aligned thumb instructions

The debug state is the state when the processor is in halting debug

Privilege levels

Unprivileged:

The software has limited access to the move from the general-purpose register to the special register (MSR) and move from special register to general-purpose register (MRS) instructions, and cannot use the change processor state/disable interrupts (CPSID) and change processor state/enable interrupts (CPSIE) instructions. It cannot access the system timer, NVIC, or system control block. Restricted access to memory or peripherals

Privileged:

The software can use all the instructions and has access to all resources

In the thread mode, the CONTROL register controls whether software execution is privileged or unprivileged. In the handler mode, software execution is always privileged. Only privileged software can write to the CONTROL register to change the privilege level. Unprivileged software can use the SVC instruction to transfer control to the privileged software.

In the handler mode, the MSP is always used. The exception entry and return mechanisms automatically update the CONTROL register, which may change depending on whether MSP or PSP is used.

In the thread mode, use the MSR instruction to set the stack pointer bit in the CONTROL register. When changing the stack pointer, use an ISB instruction immediately after the MSR instruction. This ensures that instructions after the ISB execute using the new stack pointer.

Instruction set

The CM33 CPU supports all the 16-bit thumb instructions defined by the Arm®v8‑M architecture. In addition to that, the processor implements the T32 instruction set based on the thumb-2 technology, ensuring high code density and reduced program memory requirements.

The CM33 CPU implements the following instruction from Arm®v8‑M:

All base instructions

All instructions in the main extension

All instructions in the security extension when security extension is enabled

All instructions in the DSP extension (optional)

All single-precision instructions and double-precision load and store instructions in the floating-point extension when FPU is enabled

For more information about these instructions, see section 3 - The Cortex®-M33 Instruction Set of the Arm® Cortex®- M33 Devices Generic User Guide.

The processor also implements custom datapath extension (CDE) instructions. The CDE introduces 2×3 classes of instructions in the coprocessor instruction space:

Three classes operate on the general-purpose register file

Three classes operate on the floating-point register file

For specific information on the CDE instructions implemented in the processor, see section 9. Arm® custom instructions in Arm® Cortex®-M33 processor RM.

Registers summary

The CM33 CPU has the following 32-bit core registers. When the security extension is included, some of the registers are banked. The secure view of these registers is available when the CPU is in the secure state and the non-secure view when the CPU is in non-secure state.

Name | Type 1 | Required privilege 2 | Reset value | Description |

|---|---|---|---|---|

R0-R12 | RW | Either | UNKNOWN | R0-R12 are general-purpose registers for data operations. |

MSP (R13) | RW | Either | - | The stack pointer (SP) is register R13. In Thread mode, the CONTROL register indicates the stack pointer to use, Main Stack Pointer (MSP) or Process Stack Pointer (PSP). When the Arm®v8‑M Security Extension is included, there are two MSP registers in the Cortex®-M33 processor:

When the Arm®v8‑M Security Extension is included, there are two PSP registers in the Cortex®-M33 processor:

|

PSP (R13) | RW | Either | UNKNOWN | |

MSPLIM | RW | Privileged | 0x00000000 | The stack limit registers limit the extent to which the MSP and PSP registers can descend respectively. When the Arm®v8‑M Security Extension is included, there are two MSPLIM registers in the Cortex®-M33 processor:

When the Arm®v8‑M Security Extension is included, there are two PSPLIM registers in the Cortex®-M33 processor:

|

PSPLIM | RW | Privileged | 0x00000000 | |

LR (R14) | RW | Either | UNKNOWN | The Link Register (LR) is register R14. It stores the return information for subroutines, function calls, and exceptions. |

PC (R15) | RW | Either | - 3 | The Program Counter (PC) is register R15. It contains the current program address. |

xPSR | RW | Either | - | The Program Status Register (PSR) combines:

These registers provide different views of the PSR. |

APSR | RW | Either | UNKNOWN | The APSR contains the current state of the condition flags from previous instruction executions. |

IPSR | RO | Privileged | 0x00000000 | The IPSR contains the exception number of the current ISR. |

EPSR | RO | Privileged | - 4 | The EPSR contains the thumb state bit and the execution state bits for the If-then (IT) instruction, and interruptible-continuable instruction (ICI) field for an interrupted load multiple or store multiple instruction. |

PRIMASK | RW | Privileged | 0x00000000 | The PRIMASK register prevents activation of exceptions with configurable priority. When the Arm®v8‑M Security Extension is included, there are two PRIMASK registers in the Cortex®-M33 processor:

|

BASEPRI | RW | Privileged | 0x00000000 | The BASEPRI register defines the minimum priority for exception processing. When the Arm®v8‑M Security Extension is included, there are two BASEPRI registers in the Cortex®-M33 processor:

|

FAULTMASK | RW | Privileged | 0x00000000 | The FAULTMASK register prevents activation of all exceptions except for NON-MASKABLE INTERRUPT (NMI) and optionally secure HardFault. When the Arm®v8‑M Security Extension is included, there are two FAULTMASK registers in the Cortex®-M33 processor:

|

CONTROL | RW | Privileged | 0x00000000 | The CONTROL register controls the stack used, and optionally the privilege level, when the processor is in the thread mode. When the Arm®v8‑M Security Extension is included, there are two CONTROL registers in the Cortex®-M33 processor:

|

The CM33 floating-point unit (FPU) has the following registers:

Thirty-two 32-bit single-precision registers, S0 to S31. These registers can also be addressed as sixteen 64-bit double-precision registers, D0 to D15

The four FPU control and status registers are as follows:

FPCCR – Floating-point Context Control Register

FPCAR – Floating-point Context Address Register

FPSCR – Floating-point Status Control Register

FPDSCR – Floating-point Default Status Control Register

For more information on how these registers are used, see the Arm® Cortex®-M33 reference manual.

Use the MSR and MRS instructions to access the PSR, PRIMASK, CONTROL, FAULTMASK, and BASEPRI registers. The following tables show how the PSR bits are assigned. See the Combined Program Status Register section in the Arm® Cortex®-M33 reference manual for detailed information.

Bit | Name | Usage |

|---|---|---|

31 | N | Negative flag |

30 | Z | Zero flag |

29 | C | Carry or borrow a flag |

28 | V | Overflow flag |

27 | Q | DSP overflow and saturation flag |

26:20 | - | Reserved |

19:16 | GE[3:0] | Greater than or equal flags |

15:0 | - | Reserved |

Bit | Name | Usage |

|---|---|---|

31:9 | - | Reserved |

8:0 | Exception number | This is the number of the current exceptions:

|

Bit | Name | Usage |

|---|---|---|

31:27 | - | Reserved, RES0 |

26:25, 15:10 | ICI | Interruptible-continuable instruction bits |

26:25, 15:10 | IT | Indicates the execution state bits of the IT instruction |

26:25, 11:10, 15:12 | ECI | Exception continuation flags for beat-wise vector instructions. This field encodes which beats of the in-flight instructions have completed. |

24 | T | Thumb state bit |

23:16 | - |

1

Describes the access type during program execution in the thread mode and the handler mode. Debug access can differ.

2

An entry of either means privileged and unprivileged software can access the register.

3

Soft reset to the value retrieved by the reset handler.

1

Describes the access type during program execution in the thread mode and the handler mode. Debug access can differ.

2

An entry of either means privileged and unprivileged software can access the register.

3

Soft reset to the value retrieved by the reset handler.

Bus infrastructure

The bus infrastructure in a system-on-chip (SoC) forms the backbone of communication between various components within the chip. It is a bus network that connects different IP blocks, such as processors, memory, peripherals, and accelerators. The bus infrastructure provides a standardized interface for data and control signals, enabling seamless interaction and data exchange among these components. It typically consists of different types of buses, such as system buses, interconnects, and peripheral buses, each serving a specific purpose. System buses and interconnects, such as the Advanced High-Performance Bus (AHB), facilitate high-bandwidth communication between processors, memory, and other critical components.

The

PSOC™ Control C3

MCU family features a SYSCPUSS, which consists of AHB5-based bus infrastructure that interconnects multiple bus masters with slaves. The bus interconnect uses bridges, upsizers, and downsizers to connect to other interconnects of varying bus widths, allowing access from multiple masters to slaves and enabling concurrent access and efficient operation even when several high-speed peripherals are working at the same time. This bus infrastructure for

PSOC™ Control C3

devices is shown in

Figure 2

.

Figure 2.

Bus infrastructure for

PSOC™ Control C3

devices

SYSCPUSS AHB5 interconnect

The SYSCPUSS (CM33 CPU) uses a 128-bit and 32-bit multilayer AHB5 bus matrix interconnect. The AHB5 bus masters may reside in the SYSCPUSS or outside of the SYSCPUSS (the SYSCPUSS external bus masters). Similarly, the AHB5 bus slaves may reside inside the SYSCPUSS (for example, the on-chip memory controllers) or outside of the SYSCPUSS (for example, slaves connected to the peripheral interconnect (PERI) or to the external slave interfaces).

The SYSCPUSS AHB5 bus matrix interconnects the following masters and slaves:

Masters:

Cortex®-M33 Code AHB (C-AHB) bus via Instruction cache (I-cache)

Cortex®-M33 Slave AHB (S-AHB) bus

Two direct memory access – Datawire (DMA0, DMA1)

One Cryptographic accelerator (CryptoLite)

Slaves:

Flash controller inside SYSCPUSS

One SRAM controller inside SYSCPUSS (SRAM0)

One ROM inside SYSCPUSS

CM33 to peripheral interconnect (PERI_CM33)

One AHB DMA to peripheral interconnect (PERI_DMA)

AHB5 bus matrix interconnect

The SYSCPUSS uses a round-robin with latency scheme to implement bus arbitration in the AHB5 interconnect.

The following table shows the SYSCPUSS AHB5 bus matrix interconnect:

Bus masters | Bus slaves | ||||

Flash | ROM | SRAM0 | PERI_CM33 | PERI_DMA | |

CM33_C-AHB | X | X | x | - | |

CM33_S-AHB | x | - | X | X | - |

DMA0 | X | - | X | - | X |

DMA1 | X | - | X | - | X |

CryptoLite | X | - | X | - | X |

Where,

"

X

" = connection, bold font type denotes 128-bit bus

"-" = no connection

"x" = connection, aliased address path

"X" = connection

"

x

" = connection, aliased address path, bold font type denotes 128-bit bus

Note:

Memory aliasing allows the CM33 C-AHB bus (I-Cache) to access system SRAM. The CM33 S-AHB bus uses the aliased address path and writes into flash (in C-AHB bus address space). Data can be read from the flash aliased address, but it is not preferred because it is not cached by the CM33's I-cache

All CM33 C-AHB bus accesses are cacheable

DMA writes to aliased addresses using S-AHB bus address space (above 0x20000000)

Write on aliased addresses from the DMA or CM33 S-AHB bus must be followed by a cache invalidation sequence to ensure that stale data does not remain in the cache

PERI_CM33 and PERI_DMA interfaces provide access to the peripherals connected via peripheral interconnect (PERI)

SYSCPU buses

Cortex-M33 C-AHB bus

This bus connects the C-AHB bus of the Cortex®-M33 core to the bus matrix through the instruction cache. This bus is used for instruction fetch and data access to the internal and external memories mapped in the code region. The targets of this bus are the flash, internal SRAM, and ROM.

Cortex-M33 S-AHB bus

This bus connects the S-AHB bus of the Cortex®-M33 core to the bus matrix. This bus is used by the core to access data located in a peripheral or SRAM area. The target of this bus are the aliased flash, internal SRAM, and peripherals connected via PERI_CM33.

DMA bus

This bus connects the bus matrix to the 32-bit AHB master interface of the DMA, which shares the clock with the CM33 CPU. The targets of this bus are the flash, internal SRAM, and peripherals connected via PERI_DMA.

AHB5 MMIO

The memory-mapped I/O registers for CM33, CryptoLite, DMA0/1, CPUSS, and all other peripheral configurations are accessible via the AHB5 MMIO bus interface.

Peripheral interconnect (PERI)

The peripheral interconnect (PERI) implements the AHB5 bus matrix infrastructure, connecting AHB masters to groups of peripheral devices. It allows internal/external masters of SYSCPUSS to interface with peripherals operating in the low-power domain. These peripheral devices include all memory-mapped registers (MMIO registers) of PERI, PCLK, and external peripheral devices, as well as synchronous and asynchronous peripherals mapped in the peripheral address space:

0x4200_0000 ~ 0x43FF_FFFF (Non-secure address map)

0x5200_0000 ~ 0x53FF_FFFF (Secure address map)

In the

PSOC™ Control C3

MCU family, there is one PERI instance. As shown in the following table, PERI comprises of six peripheral groups that connect slave peripherals present in the corresponding peripheral group to the SYSCPUSS and other AHB masters.

Peripheral group | Slave peripheral | Peripheral type | Description |

|---|---|---|---|

PERI GROUP 0 | Peripheral interconnect MMIO registers | Internal | SYSCPUSS platform component without I/O subsystem |

Peripheral Protection Control (PPC) | |||

PERI_PCLK registers | |||

APB Slave group-0, SRAM0, PROM, Flash, MXCM33-0, DW-0/1, SYSCPUSS, IPC, Fault structures MMIO registers | |||

SRSS core | Peripheral | ||

SRSS power mode | |||

SRSS backup | |||

Cryptographic accelerator (CryptoLite) | |||

Coordinate rotation digital computer (CORDIC) | |||

Debug registers | |||

PERI GROUP 1 | High-Speed I/O Matrix (HSIOM) | Peripheral | Async peripherals |

GPIO | |||

Smart I/O | |||

Low-power comparator (LPComp) | |||

PERI GROUP 2 | DFT | Peripheral | |

Efuse | |||

PERI GROUP 3 | Controller area network flexible data-rate (CAN FD) | Peripheral | Async peripherals |

Serial Communication Block (SPI/UART/I2C) (SCB0) | |||

Serial Communication Block (SPI/UART/I2C) (SCB[1:4]) | |||

PERI GROUP 4 | Timer/Counter/PWM (TCPWM) | Peripheral | Async peripherals |

High-performance programmable analog subsystem (HPPASS) | |||

PERI GROUP 5 | Serial Communication Block (SPI/UART/I2C) (SCB[5]) | Peripheral | High-speed SPI |

The AHB bus interfaces of the peripheral slaves in a peripheral group all operate on the same frequency, “clk_group[i]”. To reduce power consumption, slaves can be disabled using SL_CTL[i].ENABLED[j].

Multiplexing trigger signals is done by the trigger component. For more information, see the

Trigger multiplexer (Trigger MUX)

chapter.

AHB bus error handling

The following bus errors are possible in the bus infrastructure:

AHB error response detected at the master interface

AHB error response from the peripheral decoder (peripheral decoder gives error response in any of the scenario’s: “access to the respective slave is disabled/reset by using SL_* registers” (refer to the

PSOC™ Control C3

MCU registers reference manual for more information on these registers) or “access to an unmapped slave address” or “error response from the respective peripheral itself”)

No response for the AHB transaction from the peripheral for a higher number of cycles than expected

PERI uses the fault interface to report these errors.

Bus master peripherals

Direct memory access (DMA-DW)

The DMA0/1 can be used as an AHB master of the CPU subsystem. The DMA-DW is ideal for small data size and transactional DMA, which is typically used to send bytes between peripherals, for example, from ADC to RAM. The DMA-DW uses a 32-bit AHB bus.

CryptoLite

CryptoLite offers an AHB-Lite master interface, which supports 8/16/32-bit AHB-Lite transfers. The AHB-Lite master interface enables the subsystem to access operation operand data from system memories (for example, flash or SRAM memories). Memory buffer accesses can be 8/16/32-bit accesses.

Inter processor communication (IPC)

Inter-processor communication (IPC) provides the functionality for secure applications and non-secure applications to communicate and synchronize their activities. IPC hardware is implemented using two register structures.

IPC Channel: Communication and synchronization between processors are achieved using this structure

IPC Interrupt: Each interrupt structure configures an interrupt line, which can be triggered by a ‘notify’ or ‘release’ event of any IPC channel

The channel and interrupt structures are independent and have no correlation to each other, as shown in

Figure 3

. This allows for building varying models of interfaces, as shown in the

Typical usage models

.

Figure 3.

IPC register architecture

Features

The features of IPC are as follows:

Implements locks for mutual exclusion and synchronization between secure and non-secure applications

Allows sending messages between secure and non-secure applications

Supports up to 16 channels for communication

Supports up to 16 interrupts, which can be triggered using notify or release events from the channels

Architecture

IPC channel

An IPC channel is implemented as six hardware registers, as shown in

Figure 4

. The IPC channel registers are accessible to both secure and non-secure applications in the system.

IPC_STRUCTx_ACQUIRE: This register determines the lock feature of the IPC. The IPC channel is acquired by reading this register. If the SUCCESS field returns a value of ‘1’, it means that the read acquired the lock. If the SUCCESS field returns a value of '0', it means that the read operation failed to acquire the lock. The P, NS, PC, and MS fields represent the access attributes of the transaction that previously obtained the lock successfully, and the current access does not affect these fields.

Note that a single read access performs two functions:

The attempt to acquire a lock

Return the result of the acquisition attempt (SUCCESS field)

The atomicity of these two functions is essential in a CPU with multiple tasks that can preempt each other. When acquired, this register is released by writing any value into the IPC_STRUCTx_RELEASE register. If the register is already in an acquired state, another attempt to read it will not be able to acquire it

IPC_STRUCTx_NOTIFY: This register is used to generate an IPC notify event. Each bit in this register corresponds to an IPC interrupt structure. The notify event generated from an IPC channel can trigger any or multiple interrupt structures

IPC_STRUCTx_RELEASE: This field unlocks and triggers release events for the IPC interrupt structures, but only when the lock is obtained (LOCK_STATUS.ACQUIRED is '1'). The release event generated by an IPC channel can trigger any or multiple interrupt structures. To only release the IPC channel and not generate an interrupt, you can write a zero into the IPC release register. Masking of the interrupt can also be achieved by the IPC_INTR_STRUCTx_INTR_MASK register

IPC_STRUCTx_DATA0 and IPC_STRUCTx_DATA1: These registers are designed to hold data, and they are both 32-bit in size. These registers can be considered as the shared data memory for the channel. Typically, these registers will hold messages that need to be communicated between secure and non-secure applications. If the messages are larger than the combined 64-bit size, place pointers in one or both of these registers

IPC_STRUCTx_LOCK_STATUS: This register provides the instantaneous lock status for the IPC channel. If the channel is acquired (LOCK_STATUS.ACQUIRED is '1'), it shows the protection context, security, and other information in the respective bit fields. However, if the lock is not acquired (LOCK_STATUS.ACQUIRED is '0'), the values in fields P, NS, PC, and MS are not valid. The lock status reading only gives an immediate status, which can change in the next cycle

Figure 4.

IPC channel structure

IPC interrupt

Each IPC interrupt line in the system has a corresponding IPC interrupt structure. An IPC interrupt can be triggered by a notify or a release event from any of the IPC channels in the system. You can choose to mask any of the sources of these events using the IPC interrupt registers.

Figure 5

shows the registers in an IPC interrupt structure.

IPC_INTR_STRUCTx_INTR: This register provides the instantaneous status of the interrupt sources. Note that there are 16 notify and 16 release event bits in this register. These are the notify and release events corresponding to the 16 IPC channels. When a notify event is triggered in IPC channel 0, the corresponding Notify 0 bit is activated in the interrupt registers. A write of ‘1’ to a bit will clear the interrupt

IPC_INTR_STRUCTx_INTR_MASK: The bit in this register masks the interrupt sources. Only the interrupt sources with their masks enabled can trigger the interrupt

IPC_INTR_STRUCTx_INTR_SET: A write of ‘1’ into this register sets the interrupt

IPC_INTR_STRUCTx_INTR_MASKED: This register provides the instantaneous value of the interrupts after they are masked. The values in this register are IPC_INTR_STRUCTx_INTR and IPC_INTR_STRUCTx_INTR_MASK

Figure 5.

IPC interrupt structure

IPC channels and interrupts

The IPC block has a set of associated IPC interrupts. Each IPC interrupt register structure corresponds to an IPC interrupt line. This interrupt can trigger an interrupt on any of the processors in the system. The interrupt routing for processors is dependent on the device architecture.

Each IPC channel has a release and notify register, which can drive events to any of the IPC interrupts. An illustration of this relationship between the IPC channels and the IPC interrupt structure is shown in

Figure 6

.

Figure 6.

IPC channels and interrupts

Implementing locks

The IPC channels can be used to implement locks, which are typically used between secure and non-secure applications to enable some form of mutually exclusive access to a shared resource. When secure and non-secure applications share a resource, the secure or non-secure application can acquire and release the IPC channel. So secure and non-secure applications can assume an IPC channel as a lock. The semantics of this code are that access to the shared resource is gated by the secure and non-secure application ownership of the channel. So the secure or non-secure application must acquire the IPC channel before they can access the shared resource.

A failure to acquire the IPC channel by the secure or non-secure application signifies a lock on the shared resource. Note that the IPC channel does not enforce which application acquires or releases the channel. Secure or non-secure applications can both acquire or release the IPC channel.

Message passing

IPC channels can be used to communicate messages between secure and non-secure applications. In this use case, the channel is used in conjunction with the interrupt structures. The IPC channel is used to lock access to the data registers. The IPC channel is acquired by the sender and used to populate the message. The receiver reads the message and then releases the channel. Thus, between the sender transmitting data into the channel and the receiver reading it, the channel is locked for all other task access. The sender uses a notify event on the receiver’s IPC interrupt to denote a send operation. The receiver acts on this interrupt and reads the data from the data registers. After the reception is complete, the receiver releases the channel and can also generate a release event for the sender's IPC interrupt. Note that the action of locking the channel does not restrict access to the data registers in hardware. This is a semantic that should be enforced by software.

shows an example of a sender (a non-secure application) sending data to a receiver (a secure application). IPC interrupt A is configured to interrupt non-secure application. IPC interrupt B is configured to interrupt secure application.

The sender will attempt to acquire the IPC channel by reading the IPC_STRUCTx_ACQUIRE register. If the channel is acquired, the sender has ownership of the channel for data transmission. This also changes the status of the channel and its corresponding IPC_STRUCTx_LOCK_STATUS register. If the channel is not acquired, the sender should wait until the channel is free for acquisition. This can be done by polling the IPC channel’s IPC_STRUCTx_LOCK_STATUS register

After the IPC channel is acquired, the sender has control of the channel for communication and places the data in the IPC_STRUCTx_DATA0 and IPC_STRUCTx_DATA1 registers

Now that the message is placed in the IPC channel, the sender generates a notify event on the receiver’s interrupt line. It achieves this by setting the corresponding bit in the IPC channel’s IPC_STRUCTx_NOTIFY register. This event creates a notify event at IPC interrupt B (IPC_INTR_STRUCTx_INTR). If the IPC channel’s notify event is enabled by setting the mask bit (IPC_INTR_STRUCTx_INTR_MASK 31:16) in the IPC interrupt B, this will generate an interrupt in the receiver

When it receives IPC interrupt B, the receiver can poll the IPC_INTR_STRUCTx_INTR_MASKED register to understand which IPC channel triggered the notify event. Based on this, the receiver identifies the channel to read and reads from the IPC channel’s IPC_STRUCTx_DATA0 and IPC_STRUCTx_DATA1 registers. The receiver has now received the data sent by the sender. It needs to release the channel so that other processes can use it

The receiver releases the channel. It also optionally generates a release event on the sender’s IPC interrupt A. This generates a release event interrupt on the sender if the corresponding channel release event is masked

On receiving the release interrupt, the sender can act on the event based on the application requirement. It can either try to reacquire the channel for further transmission or go to other tasks because the transmission is complete.

Figure 7.

Sending messages using IPC

In the previous example, the size of the data being transmitted was only 64 bits. Larger messages can be sent as pointers. The sender can allocate a larger message structure in memory and pass the pointers to the data registers, see

Figure 8

for usage. Note that the user code must implement the synchronization of the message read process.

The implementation can stall the channel until the receiver has used all the data in the message packet and the message packet can be rewritten. This is worthless because it will stall other inter-process communications as the number of IPC channels is limited

The receiver can release the channel as soon as it receives the pointer to the message packet. It implements the synchronization logic in the message packet as a flag, which the sender sets on write complete and the receiver clears on read complete

Figure 8.

Communicating larger messages

Typical usage models

The unique channel and interrupt architecture of the

PSOC™ Control C3

IPC allows for a range of usage models for communication between secure and non-secure applications. Some of these are listed here as an example. Note that the communication models possible, based on the IPC architecture, are not restricted to the ones listed in this document. Also note that this document only provides a high-level usage model and does not provide details of data management in the communication. This must be determined based on the specific application use case.

Full-duplex communication

In this usage model, an IPC channel is used according to the direction of communication between secure and non-secure applications. In this example, IPC channel X is dedicated to data communication from non-secure application to secure application and IPC channel Y is for data communication from secure application to non-secure application. The IPC interrupt X will signal events on secure application. Therefore, its interrupt output is connected to the secure application's system interrupts. The events are triggered by writing into the IPC interrupt register structure over the system bus. Similarly, IPC interrupt Y is dedicated to non-secure application.

Figure 9.

Full-duplex IPC between secure and non-secure application

Half-duplex with independent event handling

In this case, only one IPC channel is used to set up the transfer between the secure and non-secure applications. This means that only one side controls data transfer at a time. The channel's lock register must be used to avoid contention of the one shared IPC channel. Two independent events are supported since two IPC interrupt structures are used. This model is shown in

Figure 10

.

Figure 10.

Half-duplex with independent event handling

Half-duplex with shared event handling

In this model, both the IPC channel and interrupt are shared between the secure and non-secure applications. Since the interrupt is also shared, access to the interrupt registers must be managed using the IPC lock of the channel. As shown in

Figure 11

, the IPC interrupt is set up to trigger interrupts in both secure and non-secure applications. Therefore, secure or non-secure application interrupts should have logic in their ISR to check which application is in control of the IPC and determine if the message and event were for that application.

Figure 11.

Half-duplex with shared event handling

Flash

The

PSOC™ Control C3

flash offers high bulk program performance and supports ultra-low-power operation. Flash is typically used to store CPU instructions and data when the device's power is off. Flash may be written, but the process is much slower and more restrictive than for SRAM. This chapter explains the geometry and capability of flash memory.

Features

Flash has the following features:

Flash memory size of up to 256 KB

512-byte row size; minimum programmable unit

9-bit ECC for single error correction and dual error detection (SECDED)

Supports the Read While Write feature

Flash memory protection using the memory protection controller (MPC)

Supports a programmable number of wait states

Arm® Q-Channel LPI for low-power mode management

10 - 20 year retention

Endurance of 100k program cycles

Configuration

Block diagram

This section explains the major components within the FLASHC.

Figure 12.

FLASHC high-level block diagram

Flash geometry

The following figure shows the geometry of Flash Macro (FM).

Figure 13.

Flash geometry

Read Word: Flash Macros (FMs) have a Read Word size that is read and returned on each read command. Each word is 128 data bits with 9 bits of ECC

Rows: Rows are associated with a wordline in the FM and can only be programmed/erased in their entirety. This is composed of 32 units of Read Word. Each wordline size is 512 bytes

Sector: A sector is composed of 256 rows. Each sector size is 128 KB

33

rd

column: In the FM, when erase/program cycles occur to the other rows in the same sector, the unselected rows see a program disturb, which degrades the endurance/retention of memory cells. The 33

rd

column is used as a counter to track the oldest row and the youngest row in the sector through these count values. The data from the 33

rd

column is used to initiate a refresh operation

Refresh rows: These are additional pages in each sector only to support refresh operations. A refresh operation involves erasing and destroying original data in a row before reprogramming it. Any interruptions during this sequence may leave critical rows of data in a corrupted or erased state. Therefore, data from the pages to be refreshed is copied to refresh rows. Then the rows to be refreshed are erased and reprogrammed with the same data from the refresh rows with a new counter value. Refresh is not allowed in sector 1 because SFLASH is shared with this sector. The access to the refresh rows must be configured to a Protection Context (PC) of 0, 1, or 2 to prevent corruption of the recovery process. It is the responsibility of the OEM code to test for refresh and to initiate the flash refresh routine when required

Note:

Any EEPROM emulation memory must be allocated in physical sector 0.

Bank modes and address mapping

This flash memory controller has a dual-bank mode feature. When using dual-bank mode, the flash memory region is split into two half-banks. One is called Bank 0, and the other is called the Bank 1.

FM supports a Read While Write operation on the same flash. This means a write can be done on one logical bank and a read can be done from the other bank. If the write and read is done from the same logical bank, it will result in an error.

The main flash region supports dual-bank mode. The user can select the mode through FLASH_CTL.BANK_MODE.

This is to support Firmware updates of the software image in flash memory.

These address maps are configurable to support bank swapping as follows:

When configuring single bank mode, the entire main flash regions are mapped as a single contiguous address region

When configuring dual bank mode, the main flash region is split into two halves, and each half is presented as a separate address region. Furthermore, these halves can be swapped to support same-location firmware upgrades

– Choosing mapping A will present the Bank 0 in the lower region and the Bank 1 in the upper region.

– Choosing mapping B will present the Bank 0 in the upper region and the Bank 1 in the lower region.

When switching flash banks, the following rules must be followed:

The BANK_MODE LSB must be changed in order for the banks to switch correctly. Modifying BANK_MAPPING without modifying the BANK_MODE LSB may result in errors

Refer to

Table 11

for flash address mapping.

Flash controller

The flash controller provides the following FM platform controller functionality:

Read from FM on the 128-bit AHB5 host interface with MPC protection connected to the 128-bit CODE interconnect

Write sequence initiation to FM on the same 128-bit AHB5 host interface or on the 32-bit AHB5 MMIO interface. The continuous sequence proceeding for control and status check is achieved through the 32-bit AHB5 MMIO interface connected to the peripheral interconnect with PPC protection

There can be three modes of operation for FM: full R-bus, full C-bus, and RWW (Read While Write) modes

The FLASHC converts the AHB5 transaction into an R-bus interface for FM data read

The wait states (FLASH_CTL.RBUS_WS) on the 128-bit AHB5 host interface for FM data read

32-bit AHB5 MMIO interface for the FLASHC MMIO and FM MMIO access for FM read, write, and control/configuration:

32-bit word-aligned access only

Peripheral protection using the Peripheral Protection Controller (PPC) within the PERI

The FLASHC converts the AHB5 MMIO transaction into a C-bus interface for FM sequence proceeding

The fault interface supports connections to the CPUSS central fault reporting infrastructure

Configurable single or dual bank modes of the FM

Power modes

The

PSOC™ Control C3

supports system power modes including OFF, HIBERNATE, DEEPSLEEP_OFF, DEEPSLEEP_RAM, DEEPSLEEP, and ACTIVE. The following table shows system and flash power mode mapping.

System power modes | FM power modes | FM time to wake | Condition |

|---|---|---|---|

Hibernate | Hibernate | < 10 us | All analog circuits Off |

DEEPSLEEP_OFF | Hibernate | < 10 us | All analog circuits Off |

DEEPSLEEP_RAM | Hibernate | < 10 us | All analog circuits Off |

DEEPSLEEP | Hibernate | < 10 us | All analog circuits Off |

SLEEP | Standby | - | All analog circuits On, No clock |

ACTIVE | Active | - | All analog circuits On, clock present |

Read While Write support

The

PSOC™ Control C3

MCU supports read operations on one sector while programming or erasing in another area. The FM contains two sectors, each 128 KB in size. The RWW feature is available between sectors, the application can read or execute from one sector while there is an ongoing write or erase operation in another sector. However, when the code execution or read is in the last 16 bytes of a given sector (say sector 0) and the flash write/erase operation is in the next sector (sector 1), an RWW violation may occur if cache pre-fetch is enabled. This is because pre-fetch will fetch the next 16 bytes of data, which is part of sector 1, while a write operation is underway in the same sector. This will result in a fault and should be considered during firmware design. Firmware can be designed to place dead code or constant data in the last 16 bytes of every sector, making sure the last 16 bytes of a sector are never accessed, or it can disable cache pre-fetch during a flash write or erase operation.

The RWW FMs can be used as a traditional one that is Read Operations through Read-bus, Read or Write Operations through Control-bus, or in RWW mode, for which Read Operations occur through Read-bus while the part is written through Control-bus. The Read-bus and Control-bus have separate sector and row address registers and pre-decoders, their outputs being multiplexed at sector level. During the write operation, the concurrent read cannot happen in the same sector.

During RWW, the following operations can be performed on the Write Sector:

Row erase or program

Sector erase or pre-program

During RWW, the following are not available:

Data read in the Write Sector

Bulk Erase or Pre-Program

Test Modes

ECC

The flash controller supports Error Correcting Code (ECC). The FM uses an additional 9 bits for every word of 128 bits to perform Single Error Correction (SEC) and Dual Error Detection (DED). Due to ECC, the internal read width is extended from 128 bits to 137 bits.

The ECC block can be tested by injecting incorrect ECC values. See

ECC (error) injection

for details.

ECC generation/encoding

The ECC Encoder is located in the FM, while the ECC Decoder is located in the flash controller within CPUSS. While in full C-bus or RWW mode, it is software configuration that either FM hardware-generated ECC or software-specified ECC written into FM follow FM C-bus ECC generation/encoding on the write sequence.

When FM ANA_CTL0.ECC_ENC_DIS == 1’b0 implies the ECC encoder is enabled for the FM with the ECC feature. The PL ECC bits are loaded automatically

When FM ANA_CTL0. ECC_ENC_DIS == 1’b1 implies the ECC encoder is disabled. FM will use the ECC parity from FM_PL_ECC.DATA9

ECC (error) injection

ECC injection can be enabled or disabled based on the register ECC_INJ_EN.ECC_INJ_ENABLE. In full R-bus or RWW mode, ECC parity can be injected based on ECC_INJ_EN.ECC_INJ_ENABLE to replace ECC parity delivered by Flash Macro. The ECC_CTL.WORD_ADDR and ECC_CTL.PARITY registers specify the address and the parity to be injected. ECC_CTL.PARITY is injected when ECC_INJ_EN.ECC_INJ_PC and ECC_CTL.WORD_ADDR both match the AHB5 read transaction over the 128-bit interface.

While in full R-bus or RWW mode, ECC parity (to replace ECC parity delivered by FM) can be injected prior to the ECC correction or decoding logic during the read. The flash MMIO ECC_INJ_EN/ECC_INJ_CTL can be enabled and configured to inject 9-bit ECC based on the Program Counter and address of the 128-bit long-word.

When ECC_INJ_EN.ECC_INJ_ENABLE is LOW, ECC_INJ_EN.ECC_INJ_PC inherits Program Counter (PC) from the master who enables/configures ECC_INJ_ENABLE HIGH.

When ECC_INJ_ENABLE is HIGH, only the PC specified by ECC_INJ_PC can access (read/write) ECC_INJ_EN (ENABLE, ECC_ERROR, and ECC_INJ_PC bits)

PC violation results in a bus error, and there is no additional fault/interrupt triggered. The only exception is PC0, which can access (read/write) ECC_INJ_EN at any time to break the potential deadlock of ECC_INJ_EN

ECC_INJ_CTL.WORD_ADDR specifies address (based on module-internal offset address) and ECC_INJ_CTL.PARITY, parity, to be injected.

When ECC_INJ_ENABLE is HIGH, only the PC specified by ECC_INJ_PC can access (read/write) ECC_INJ_CTL

PC violation results in a bus error, and there is no additional fault/interrupt triggered

PARITY is injected when ECC_INJ_PC and WORD_ADDR both match the AHB read transaction over the 128-bit interface.

ECC_INJ_CTL.PARITY replaces ECC parity from FM and is used by the ECC correction/decoding logic

ECC_INJ_EN.ECC_ERROR:

LOW (1’b0): If the injected ECC does not trigger any non-recoverable error (ECC errors <= 1)

HIGH (1’b1): If the injected ECC triggers a non-recoverable error (ECC errors >= 2). The AHB read transaction results in a bus error. There is no additional fault/interrupt triggered

ECC injection is subject to MPC protection. Each PC is allowed only to inject ECC parity into its allocated address blocks/ranges.

To disable ECC injection, the PC specified by ECC_INJ_PC should clear ECC_INJ_EN (reset ECC_INJ_ENABLE and ECC_ERROR bits). PC0 can also clear ECC_INJ_EN at any time.

FLASHC hardware clears ECC_INJ_CTL autonomously while ECC_INJ_EN is being cleared.

Security and protection

The FLASHC 128-bit AHB5 host interface is protected using MPC. The MPC implements Secure/Non-Secure block-based protection similar to the Arm® SIE-200 MPC. However, the functionality is extended to provide block-based protection for each protection context (PC) as well.

Refer to

Memory Protection Controller (MPC)

for details on MPC.

Note:

Flash write can only be done from a secure application.

Note:

FLASHC APIs can be called only from secure application.

API library

The Peripheral Driver Library (PDL) provides user access to low power mode configuration, FM sector write protection, Read While Write, and read/write operations on FM. For more information, refer to the

Peripheral Driver Library API Reference Manual

.

SRAM controller

This section explains the

PSOC™ Control C3

MCU SRAM controller, its features, architecture, and wait states. The SRAM controller enables the CPU to read and write parts of the

PSOC™ Control C3

MCU's SRAM.

In the

PSOC™ Control C3

MCU, the size of the SRAM is 64 KB. To know more about SRAM instances and their start addresses, see the

Address and memory maps

section of the CPU subsystem.

Features

The SRAM controller has the following features:

Supports 8, 16, and 32-bit access

Provides exclusive access support using Exclusive Access Monitor (EAM) from Arm® SIE-200

SRAM memory protection using the MPC (Memory Protection Controller)

SRAM power mode control using Arm® PPU (Power Policy Unit)

The SRAM controller supports the Error Correction Code (ECC) for the SRAM

See the device datasheet for electrical specifications.

Architecture

The SRAM controller has an AHB5 interface that connects to the AHB5 infrastructure. The AHB5 transfers are the origin for all SRAM accesses. The SRAM controller differentiates between the following three types of AHB5 transfers:

AHB5 read transfers

32-bit AHB5 write transfers

8-bit and 16-bit AHB5 write transfers (also referred to as

partial AHB5 write transfers

)

AHB5 read transfers

AHB5 reads transfers, and a read transfer is translated into SRAM read access.

32-bit AHB5 write transfers

A 32-bit AHB5 write transfer is translated into SRAM write access.

Partial AHB5 write transfers

Partial writes (8-bits and 16-bits) are supported through read, modify, and write by applying the associated mask during write.

Power partition control

The PWR_MACRO_CTL register controls the power state of each SRAM power partition independently. Each bit of PWR_MACRO_CTL.OFF[31:0] represents the individual state of each SRAM power partition. Enabling the bit corresponding to the particular power partition turns OFF the partitions, and disabling the bit turns ON the respective partitions. It is mandatory to ensure STATUS.PWR_DONE becomes 1 after these PWR_MACRO_CTL register contents are changed to ensure the SRAM mode transition is completed successfully. Each power partition contains a (RAM[ ]_MACRO_NR/RAM[ ]_PWR_GROUP_NR) number of base SRAM units. In

PSOC™ Control C3

MCU, RAMC0_MACRO_NR = 8 and RAMC0_PWR_GROUP_NR = 8 create 8 power partitions with 1 macro in each power partition.

The PWR_MACRO_CTL_LOCK register controls the accidental writes into the PWR_MACRO_CTL register by prohibiting read/write access when this (PWR_MACRO_CTL_LOCK[1:0]) field is not equal to zero.

Note:

The partition that is OFF loses its data content. The same is true for this partition in DEEPSLEEP-OFF, DEEPSLEEP-RAM, and DEEPSLEEP system power modes. A partition that is ON is available for operation in Active power mode. This partition retains the data contents in the DEEPSLEEP-RAM and DEEPSLEEP system power modes and loses the contents in the DEEPSLEEP-OFF system power mode.

Error Correcting Code (ECC)

The SRAM controller supports Error Correcting Code (ECC) for the SRAM.

The 7-bit SECDED parity covers the 32-bit data word as a single entity, there is no dedicated parity for the four 8-bit bytes within the data. Therefore, any partial 8-bit or 16-bit AHB5 write bus transfer requires a SRAM read access and a SRAM write access.

32-bit AHB5 write bus transfers require only a single SRAM write access

8-bit and 16-bit AHB5 write bus transfers require an additional SRAM read access that precedes the SRAM write access to retrieve the missing data bytes

When a non-recoverable error that is error of more than 1 bit is detected, the data word that is used as the result for an AHB5 bus transfer is incorrect, but NO AHB5 bus error is generated. Instead, the error is communicated through the CPUSS fault reporting infrastructure.

ECC Error Injection

The Error Injection mechanism is supported by 32-bit data word write into an address defined in ECC_MATCH. Reading from the address defined in ECC_MATCH.WORD_ADDR triggers correctable or uncorrectable fault indication, if the value in ECC_CTL.PARITY has 1, 2, or more errors compared to expected ECC value.

ECC error report functionality

The ECC syndrome logic reports recoverable and non-recoverable errors to the CPUSS fault reporting infrastructure. The ECC syndrome logic corrects recoverable errors, error up to one bit is recoverable .

Partial AHB5 write transfers

Error reported during partial write transfer involving SRAM read are listed as below

Correctable Error (1-bit error):

This corrected 32-bit data word is then merged with the write data with appropriate mask and stored in the write buffer. A future write-buffer request results in a SRAM write access with the merged write data

Multiple-bit error:

the error is communicated through the CPUSS fault reporting infrastructure

AHB5 read transfers

During the AHB read transfers below are possible scenarios.

Correctable Error (1-bit error):

The corrected data is returned to the AHB5 interface. If ECC auto-correct functionality is enabled, then the corrected data is also stored in write-buffer. A future write-buffer request results in a SRAM write access with the corrected data

Multiple-bit error:

Corrupted-data (multiple-bit error data) is returned to the AHB master on hrdata[31:0]

Correctable ECC error reporting

When the auto-correct functionality is enabled for 1-bit correctable ECC errors, the corrected data and merged data during partial write along with the corresponding AHB address is stored in the WRITE-BUFFER. Until the data for this AHB address is written back from the WRITE_BUFFER to the SRAM macro, all future accesses to this AHB address result in the data being read from the WRITE_BUFFER.

Non-correctable ECC error reporting

When a non-recoverable error is detected, this is reported only via fault reporting structure and no AHB bus error is generated. Further, the data word that is used as the result for an AHB5 bus transfer is incorrect.

Wait states

There are no wait states as there are only AHB5 requests. There shall be up to three wait states for read operation if ECC is enabled.

Interrupts

Features

The

PSOC™ Control C3

supports the following interrupt features:

Supports 140 system interrupts

Four interrupts can be mapped to the CPU's non-maskable interrupt (NMI)

All interrupt sources are capable of waking the CPU from CPU Sleep power mode

30 interrupt sources are capable of waking the Cortex®-M33 from CPU DeepSleep power mode

Nested vectored interrupt controller (NVIC) integrated with CPU core, yielding low interrupt latency

Wakeup interrupt controller (WIC) enabling interrupt detection (CPU wakeup) in CPU DeepSleep power mode

A vector table may be placed in either volatile or non-volatile memory

Separate vector tables for Cortex®-M33 secure and non-secure states

Configurable priority levels for each interrupt, eight levels on the Cortex®-M33

Level-triggered interrupt signals

Architecture

Figure 14.

PSOC™ Control C3

interrupt architecture block diagram

shows the

PSOC™ Control C3

interrupt architecture. The Cortex®-M33 has system interrupt sources directly connected to the IRQn of the NVIC. The NVIC handles enabling/disabling individual interrupt IRQs, priority resolution, and communication with the CPU core. The other exceptions, such as NMI and hard faults, are not shown in

Figure 14

because they are part of CPU core-generated events, unlike interrupts, which are generated by peripherals external to the CPU.

In addition to the NVIC, the

PSOC™ Control C3

supports wakeup interrupt controllers (WIC) for the CPU and interrupt synchronization blocks that synchronize the interrupts to the CPU's CLK_HF0 domain (adds two CLK_HF0 cycles of delay for synchronization). The WIC provides detection of interrupts in the CPU DeepSleep power mode.

Interrupts and exceptions operation

Interrupt/exception handling

The following sequence of events occurs when an interrupt or exception event is triggered:

The assumption is that all the interrupt and exception signals are initially low (idle or inactive state) and the processor executes the main code. Any interrupt signal that is held asserted is registered by the NVIC, if the interrupt or exception is enabled to be serviced by the CPU. The signal is now in a pending state, waiting to be serviced by the CPU

On detecting the signal from the NVIC, the CPU stores its current context by pushing the contents of the CPU registers onto the stack