Overview

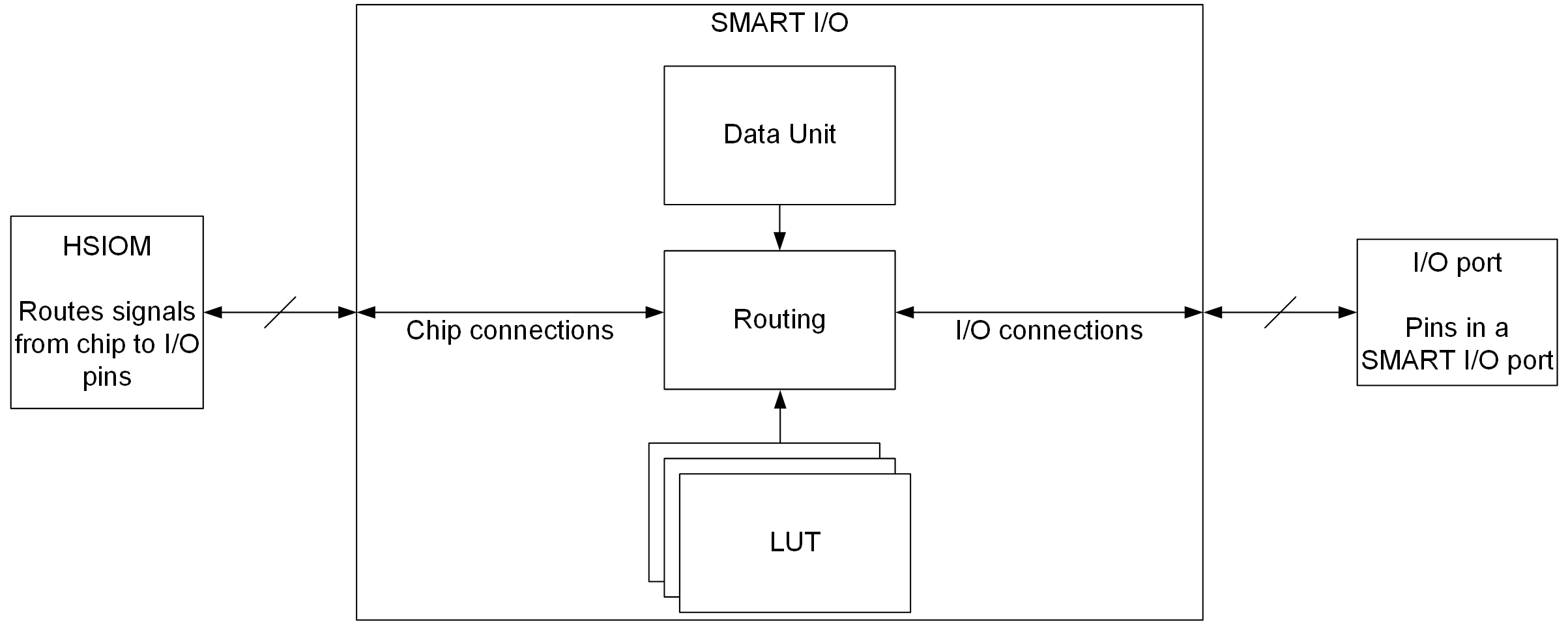

The Smart I/O block adds programmable logic to an I/O port. It is positioned in the signal path between the high-speed I/O matrix (HSIOM) and the I/O port. The HSIOM multiplexes the output signals from fixed-function peripherals and the CPU to a specific port pin and vice-versa. The Smart I/O block is placed on this signal path, acting as a bridge that can process signals between port pins and the HSIOM, as shown in the following diagram. For more information about the Smart I/O block, refer to the device Technical Reference Manual.

There are several areas in the GUI to configure signals: Chip, I/O, Data Unit, and LUT. Inputs to the chip from the I/O port can be logically operated upon before being routed to the peripheral blocks and connectivity of the chip. Likewise, outputs from the peripheral blocks and internal connectivity of the chip can be logically operated upon before being routed to the I/O port.

The programmable logic fabric of the Smart I/O can be purely combinatorial or registered with a choice of clock selection. The functionality is completely user-defined, and each path can be selectively bypassed if certain routes are not required by the fabric.

Each Smart I/O is associated with a particular I/O port and consumes the port entirely. If the Smart I/O is not enabled, then the Smart I/O functionality for that port is bypassed.

Note:

Bypassed means each chip terminal is routed directly to the corresponding I/O terminal.