KIT_PSE84_EVAL PSOC™ Edge E84 Evaluation Kit guide

About this document

Scope and purpose

This document serves as a guide for using the KIT_PSE84_EVAL PSOC™ Edge E84 evaluation kit. The document explains the kit operation, describes the out-of-the-box (OOB) example and its operation, and provides hardware details of the board.

Intended audience

This evaluation board is intended for PSOC™ Edge E84 users to familiarize with the MCU and connectivity devices. This board is intended to be used under laboratory conditions.

Reference documents

This user guide should be read in conjunction with the following documents:

Important notice

“Evaluation Boards and Reference Boards” shall mean

products embedded on a printed circuit board (PCB) for demonstration and/or

evaluation purposes, which include, without limitation, demonstration, reference

and evaluation boards, kits and design (collectively referred to as “Reference

Board”).

Environmental conditions have been considered in

the design of the Evaluation Boards and Reference Boards provided by Infineon

Technologies. The design of the Evaluation Boards and Reference Boards has been

tested by Infineon Technologies only as described in this document. The design

is not qualified in terms of safety requirements, manufacturing and operation

over the entire operating temperature range or lifetime.

The Evaluation Boards and Reference Boards provided

by Infineon Technologies are subject to functional testing only under typical

load conditions. Evaluation Boards and Reference Boards are not subject to the

same procedures as regular products regarding returned material analysis (RMA),

process change notification (PCN) and product discontinuation (PD).

Evaluation Boards and Reference Boards are not

commercialized products, and are solely intended for evaluation and testing

purposes. In particular, they shall not be used for reliability testing or

production. The Evaluation Boards and Reference Boards may therefore not comply

with CE or similar standards (including but not limited to the EMC Directive

2004/EC/108 and the EMC Act) and may not fulfill other requirements of the

country in which they are operated by the customer. The customer shall ensure

that all Evaluation Boards and Reference Boards will be handled in a way which

is compliant with the relevant requirements and standards of the country in

which they are operated.

The Evaluation Boards and Reference Boards as well

as the information provided in this document are addressed only to qualified and

skilled technical staff, for laboratory usage, and shall be used and managed

according to the terms and conditions set forth in this document and in other

related documentation supplied with the respective Evaluation Board or Reference

Board.

It is the responsibility of the customer’s

technical departments to evaluate the suitability of the Evaluation Boards and

Reference Boards for the intended application, and to evaluate the completeness

and correctness of the information provided in this document with respect to

such application.

The customer is obliged to ensure that the use of

the Evaluation Boards and Reference Boards does not cause any harm to persons or

third party property.

The Evaluation Boards and Reference Boards and any

information in this document is provided "as is" and Infineon Technologies

disclaims any warranties, express or implied, including but not limited to

warranties of non-infringement of third party rights and implied warranties of

fitness for any purpose, or for merchantability.

Infineon Technologies shall not be responsible for

any damages resulting from the use of the Evaluation Boards and Reference Boards

and/or from any information provided in this document. The customer is obliged

to defend, indemnify and hold Infineon Technologies harmless from and against

any claims or damages arising out of or resulting from any use thereof.

Infineon Technologies reserves the right to modify

this document and/or any information provided herein at any time without further

notice.

Safety precautions

Note:

Please note the following warnings regarding the hazards associated with development systems

| Caution: The evaluation or reference board contains parts and assemblies sensitive to electrostatic discharge (ESD). Electrostatic control precautions are required when installing, testing, servicing or repairing the assembly. Component damage may result if ESD control procedures are not followed. If you are not familiar with electrostatic control procedures, refer to the applicable ESD protection handbooks and guidelines. |

Introduction

The PSOC™ Edge E84 evaluation kit enables you to evaluate and develop your applications using the

PSOC™ Edge E84 series MCU

(called “PSOC™ E84”) and a multitude of on-board multimedia, Machine Learning (ML), and connectivity features like MIPI-DSI displays, audio interfaces, and AIROC™ Wi-Fi & Bluetooth® combo-based connectivity modules.

PSOC™ E84 is an ultra-low-power PSOC™ device specifically designed for ML, wearables, and IoT products like smart thermostats, smart locks, smart home appliances, and industrial HMI. Refer to

datasheet

for detailed feature description of PSOC™ E84 MCU.

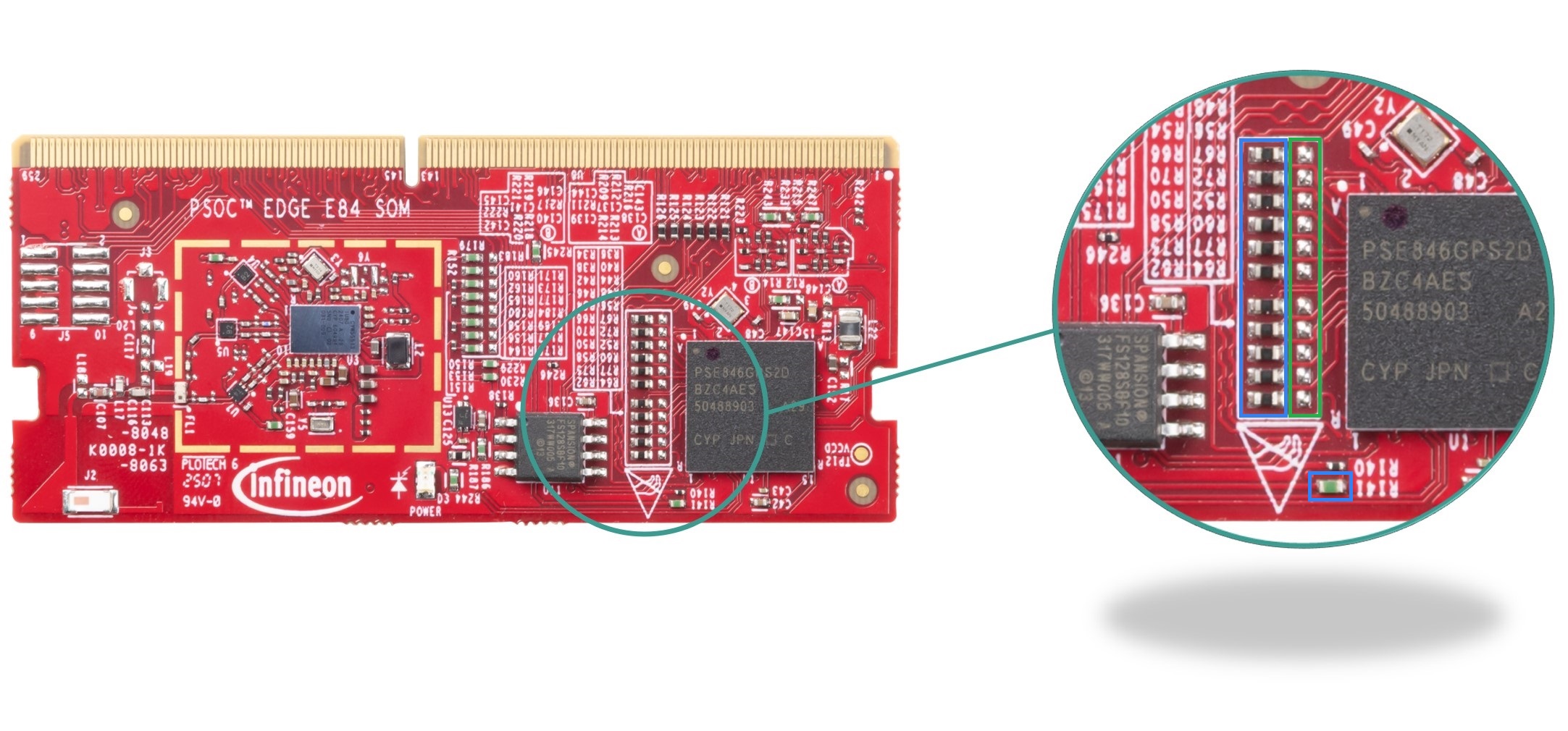

The evaluation kit carries a PSOC™ E84 MCU on a SODIMM-based detachable SOM board connected to the baseboard. The MCU SOM also has 128 Mb of QSPI flash, 1Gb of Octal flash, 128 Mb of Octal RAM, PSOC™ 4000T as CAPSENSE™ co-processor, and on-board AIROC™ Wi-Fi & Bluetooth® combo.

The baseboard has M.2 interface connectors for interfacing external radio modules based on AIROC™ Wi-Fi & Bluetooth® combos and external memory interfaces. The base-board features an on-board programmer/debugger (KitProg3), ETM/JTAG/SWD debug headers, a custom display capacitive touch panel connector, an R-Pi compatible MIPI-DSI connector and a MIPI-DSI custom display connector, analog and PDM microphones, a headphone connector, a speaker, USB host Type-A and USB device Type-C connectors, an RJ45 Ethernet connector, an M.2 (B-key) memory interface and an M.2 (E-key) radio interface, Infineon’s Shield2Go interface, MikroElektronika's mikroBUS compatible headers, a 6-Axis IMU sensor, a 3-axis magnetometer, a microSD card holder, CAPSENSE™ buttons and slide, user LEDs, and user buttons. The MCU power domain supports 2.7 V, 3.3 V, and 4.2 V operating voltages, and the peripheral power domain supports 1.8 V and 3.3 V operating voltages.

You can use ModusToolbox™ software to develop and debug your PSOC™ E84 MCU projects.

ModusToolbox™ software

is a set of tools that enable you to integrate these devices into your existing development methodology.

Kit contents

The following are kit contents:

PSOC™ Edge E84 evaluation kit

PSOC™ Edge E8 base board

PSOC™ Edge E84 SOM (MOD_PSE84_SOMS2)

USB Type-C to Type-C cable

4.3 inch display with capacitive touch screen

0.3 MP USB camera Module with USB Type-A cable

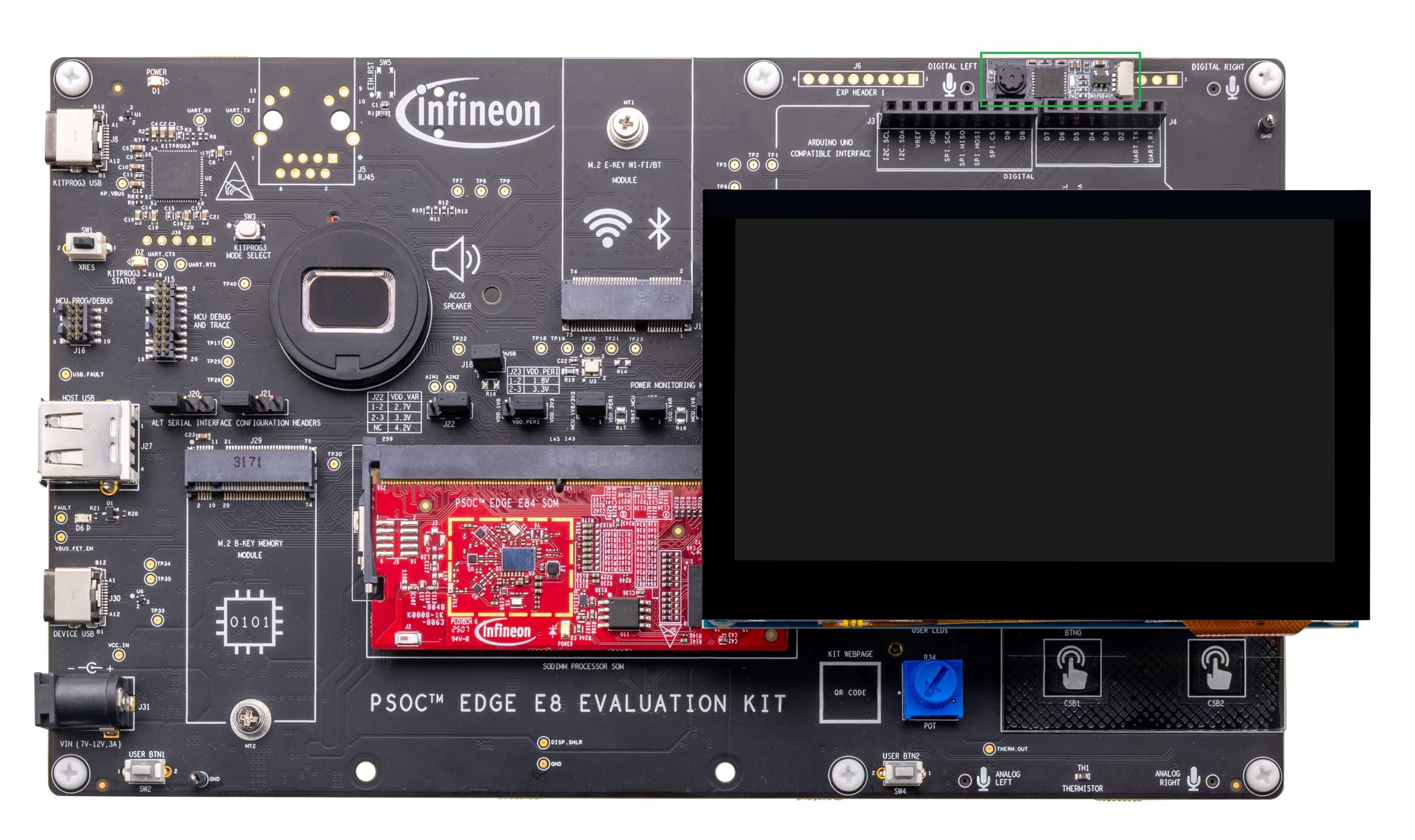

Figure 1.

Kit contents

Inspect the contents of the kit; if you find any parts missing, go to the

Infineon Support Page

.

Getting started

This guide will help you to get acquainted with PSOC™ Edge E84 evaluation kit:

The Kit operation chapter describes the major features of the PSOC™ E84 MCU evaluation board and functionalities such as programming, debugging, and the USB-UART and USB-I2C bridges

The Hardware chapter provides a detailed hardware description, kit schematics, and the Bill of Materials (BOM). This chapter also gives info on reworks required on kit to use alternate functions

Application development using PSOC™ E84 MCU Evaluation Kit is supported in ModusToolbox™ software. ModusToolbox™ software is a free development ecosystem that includes the Eclipse IDE for ModusToolbox™ software and the PSOC™ E84 SDK with PSOC™ E84 MCU. Using ModusToolbox™ software, you can enable and configure device resources, middleware libraries write C or assembly source code, program and debug the device. You can download the software from ModusToolbox™ home page . See the ModusToolbox™ software installation guide for additional information

There are wide range of code examples to evaluate the PSOC™ E84 MCU Evaluation Kit. These examples help you familiarize PSOC™ E84 MCU and create your own design. These examples can be accessed through ModusToolbox™ Project Creator tool. Alternatively, you can also visit Infineon Code examples for ModusToolbox™ software page to access these examples

Board details

The PSOC™ E84 Evaluation Kit has the following features:

PSOC™ E84 MCU - PSE846GPS4DBZC4A, See the device datasheet for more details

Onboard AIROC™ Wi-Fi & Bluetooth® combo - CYW55513IUBGT

PSOC™ 4000T as CAPSENSE™ coprocessor

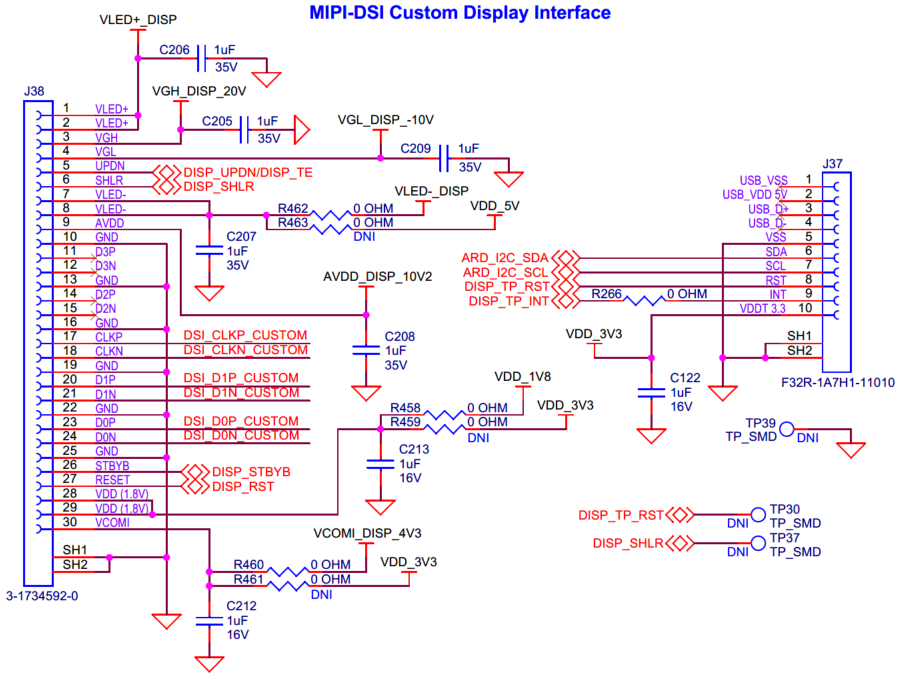

Display interfaces for custom capacitive touch panels, R-Pi compatible MIPI-DSI displays, and MIPI-DSI custom displays

Analog and PDM microphones, a headphone connector provision and an onboard speaker for audio applications

6-axis accelerometer and gyroscope IMU and a 3-axis magnetometer

Connectors for high-speed connectivity interfaces, such as Ethernet and USB

KitProg3 onboard SWD programmer/debugger, USB-UART, and USB-I2C bridge functionality

128 Mbit external Quad SPI flash, 1 Gbit external Octal flash, and 128 Mbit Octal RAM provide fast, expandable memory for data and code

M.2 (B-key) interface for external memory devices

M.2 (E-key) interface for radio connectivity modules

CAPSENSE™ touch-sensing slider (5 elements), two buttons, and proximity sense are based on self-capacitance (CSD) and mutual-capacitance (CSX) based sensing

Add-on board interface compatible with mikroBUS by MikroElektronika

Add-on board interface compatible with Infineon’s Shield2Go

Add-on board interface compatible with Arduino UNO R3

Selectable input supply voltages of 1.2 V, 3.3 V, and 4.2 V for the PSOC™ E84 MCU

Selectable input supply voltages of 1.8 V or 3.3 V for the onboard peripherals

Three user LEDs, two user buttons, and a reset button for the PSOC™ E84 MCU

A potentiometer that can be used to simulate analog sensor output

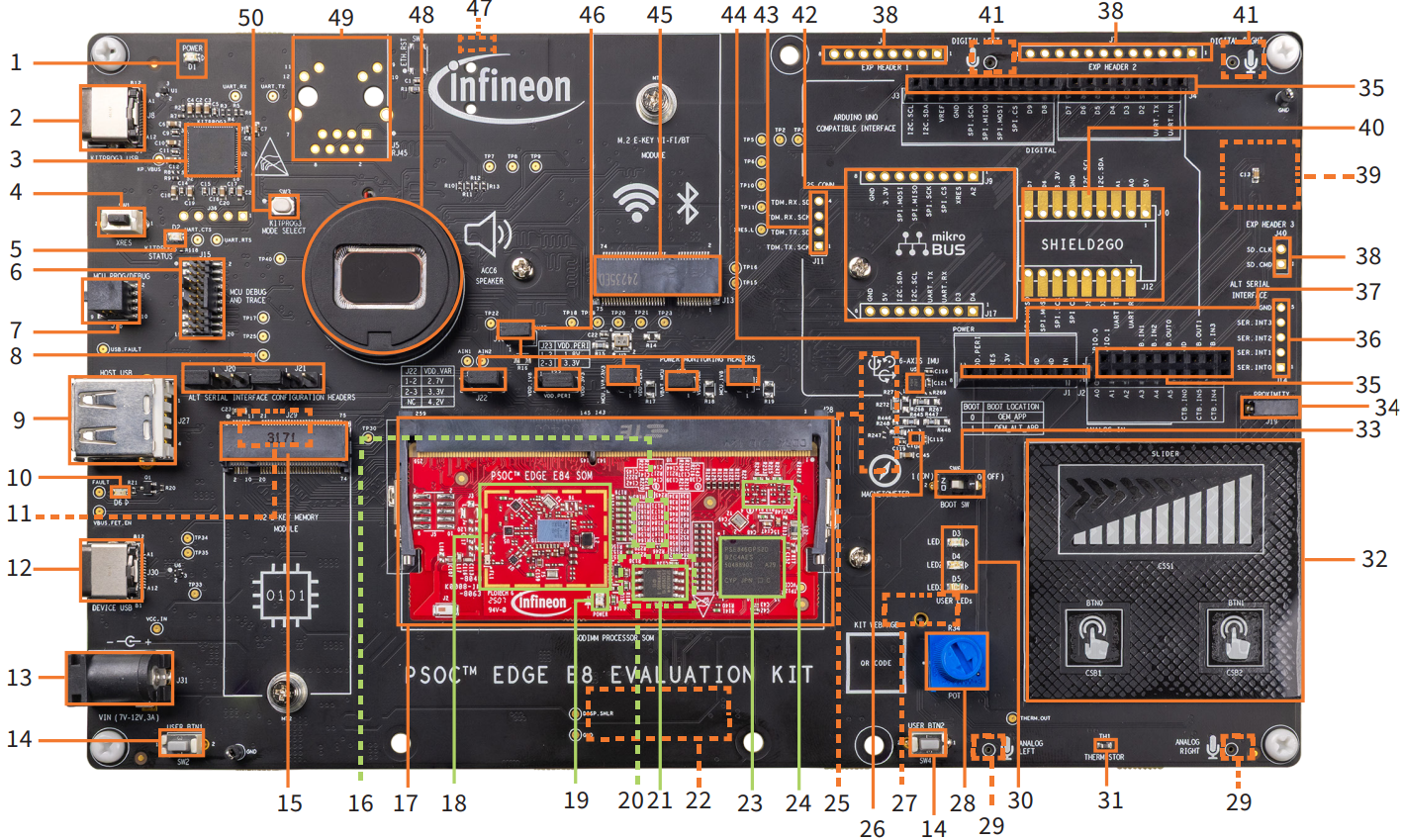

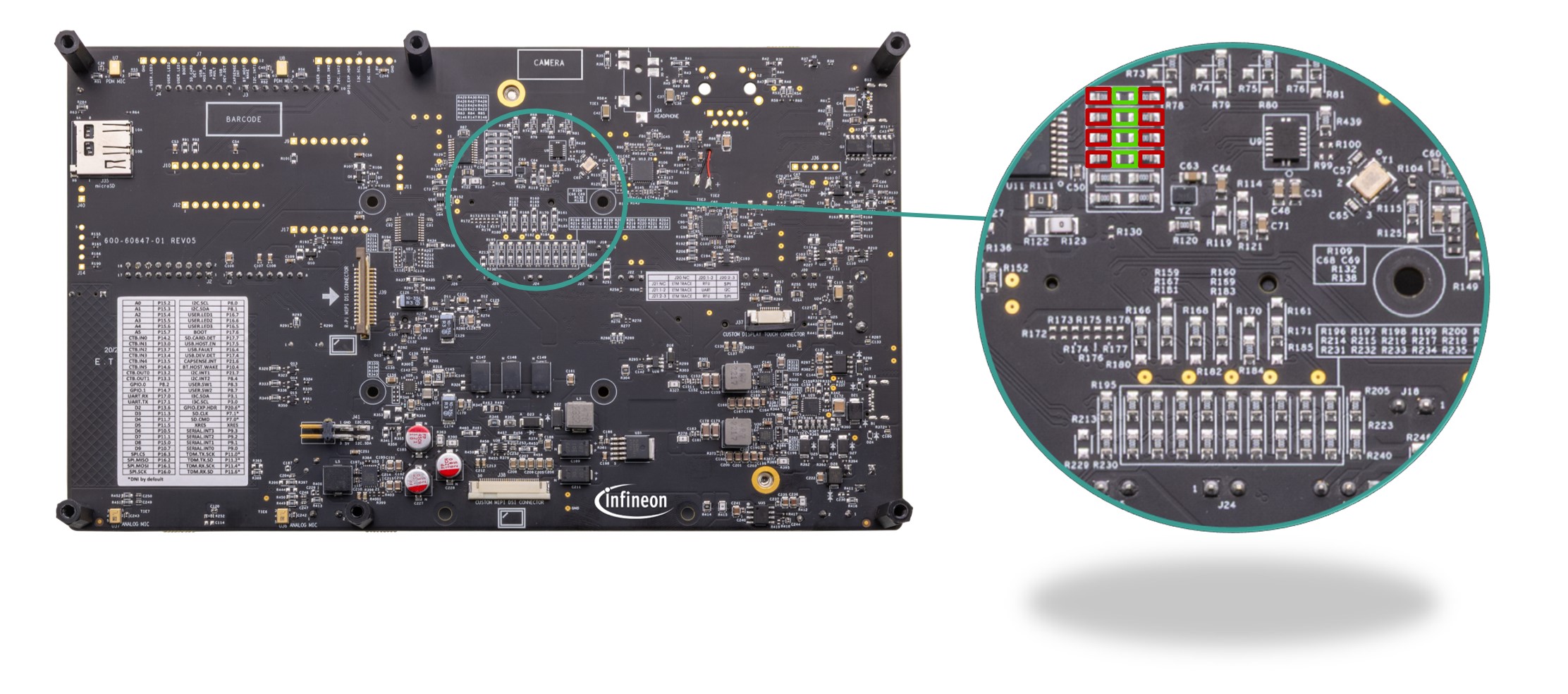

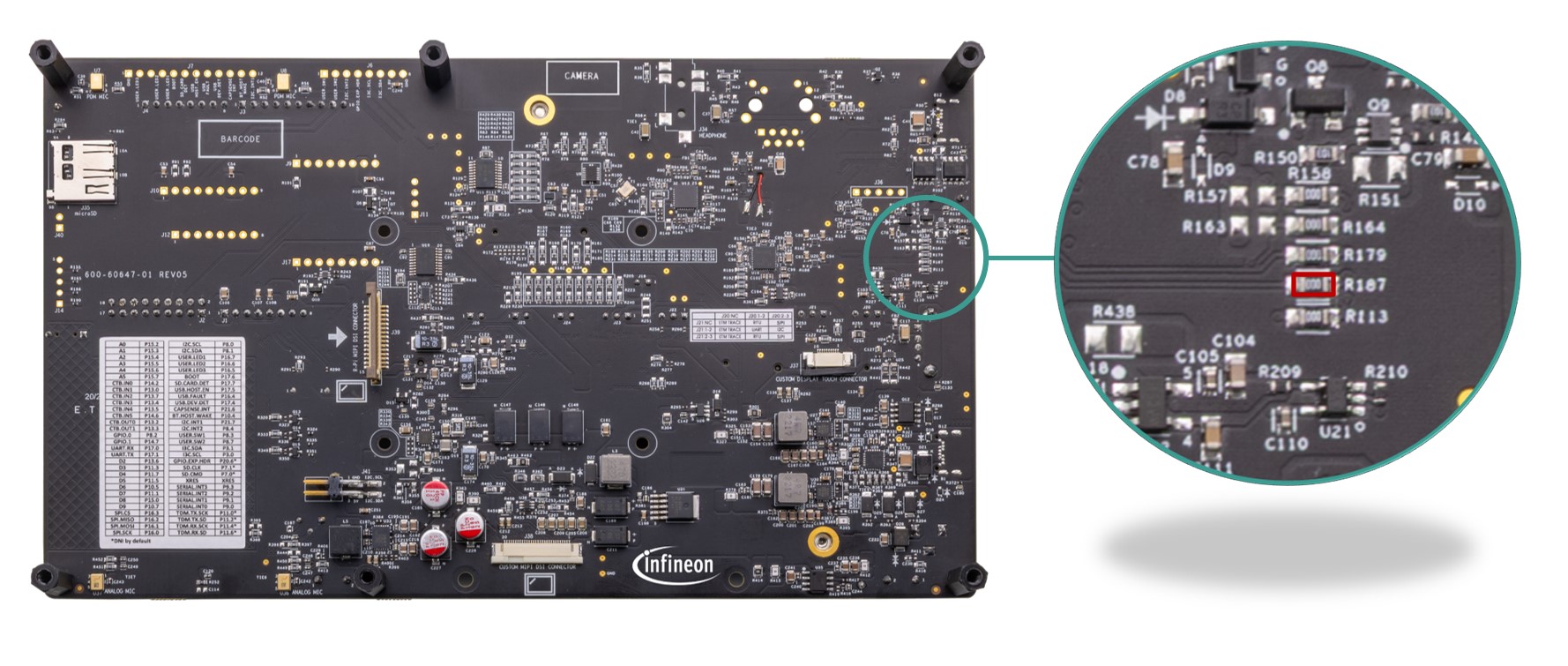

Figure 2.

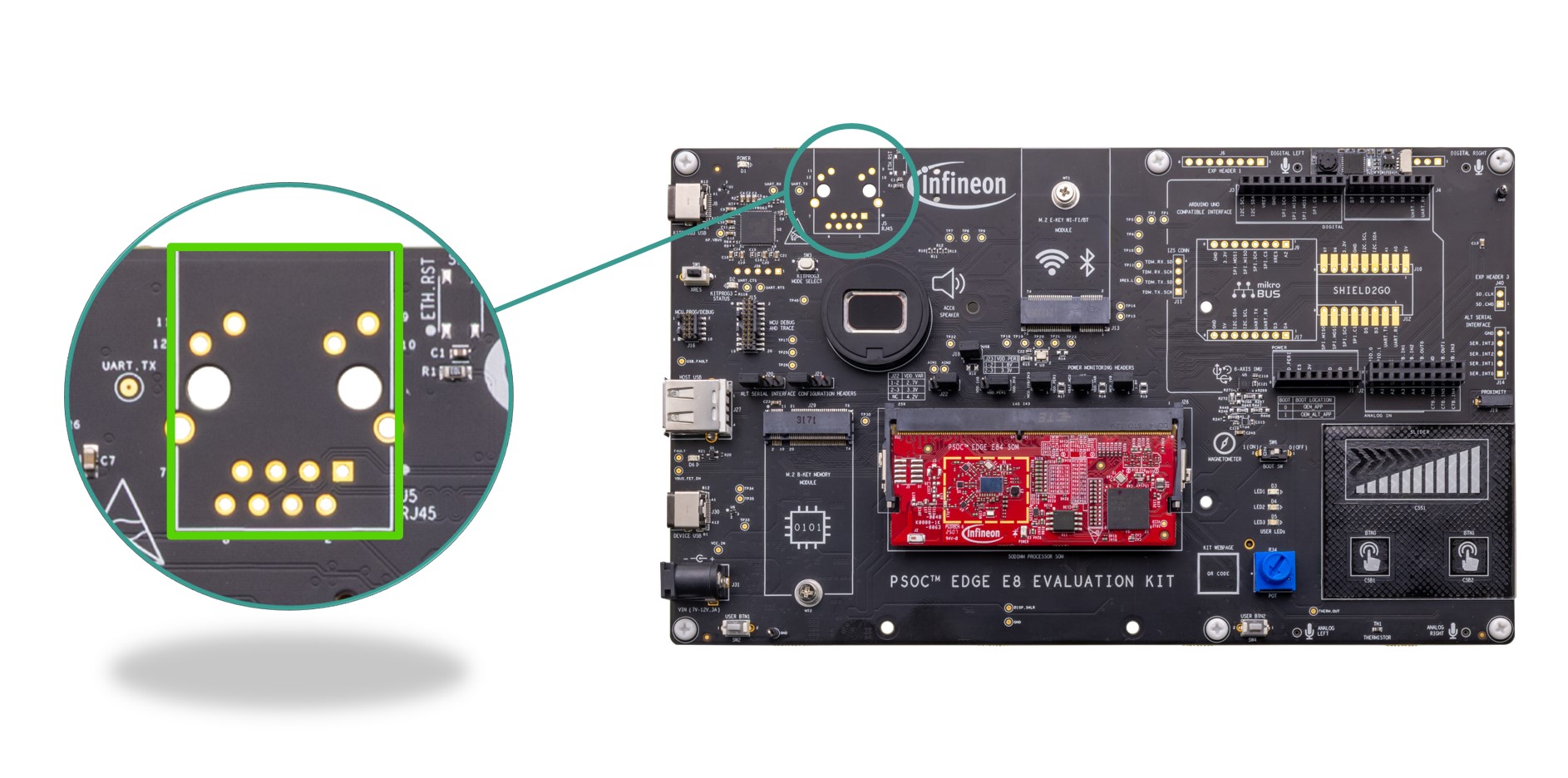

Baseboard with SOM connected - Top View

Baseboard Power LED (

D1

)

KitProg3 Program/Debug USB Type-C connector (

J8

)

PSOC™ 5LP-based KitProg3 programmer and debugger (CY8C5868LTI-LP039,

U2

)

Reset button (

SW1

)

KitProg3 status LED (

D2

)

PSOC™ Edge E84 MCU ETM/JTAG debug and trace header (

J15

)

PSOC™ Edge E84 MCU 10-pin SWD/JTAG program and debug header (

J16

)

Alternative serial interface configuration headers (

J20

,

J21

)

PSOC™ Edge E84 MCU USB host Type-A connector (

J27

)

USB Type-C Power Delivery (PD) fault LED (

D6

)

Custom display capacitive touch panel connector (

J37

)

PSOC™ Edge E84 MCU USB device Type-C connector (

J30

)

External power supply VIN connector (

J31

)

PSOC™ Edge E84 MCU user buttons (

SW2

,

SW4

)

M.2 (B-key) memory interface connector (

J29

)

128 Mbit Octal-SPI HYPERRAM™ (S70KS1283GABHI020,

U12

)

Processor system-on-module (SoM) 260-pin SODIMM connector (

J28

)

CYW55513 tri-band (Wi-Fi & Bluetooth®) combo radio (

U3

) section

Processor System on Module (SoM) power LED (

D3

)

1 Gbit Octal-SPI NOR flash (S28HS01GTGZBH1030,

U10

)

2

128 Mbit Quad-SPI NOR flash (S25FS128SAGMFB100,

U11

)

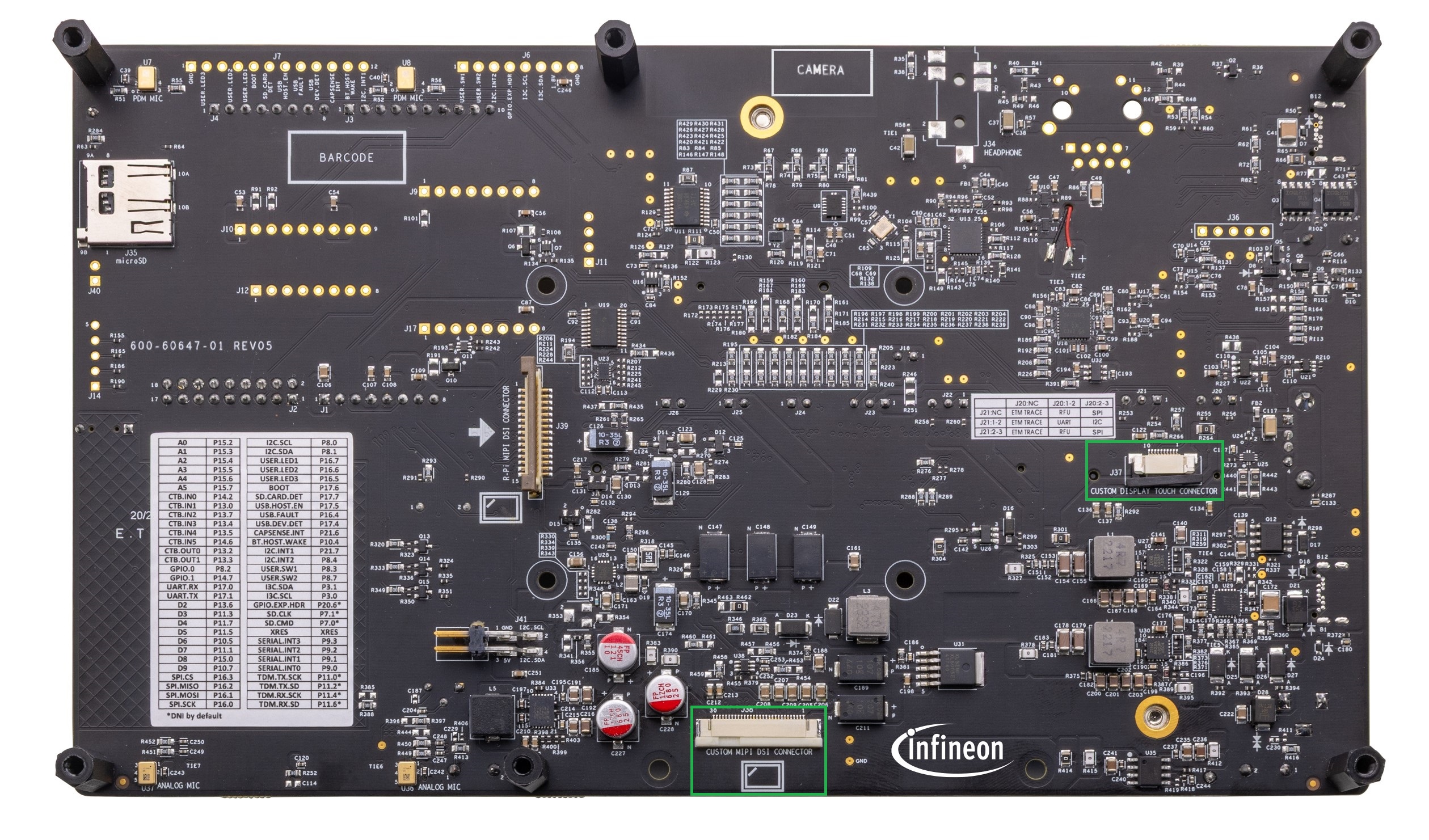

MIPI-DSI custom display connector (

J38)

1

PSOC™ Edge E84 MCU (PSE846GPS4DBZC4A,

U1

)

PSOC™ 4000T CAPSENSE™ co-processor (

U9

)

2

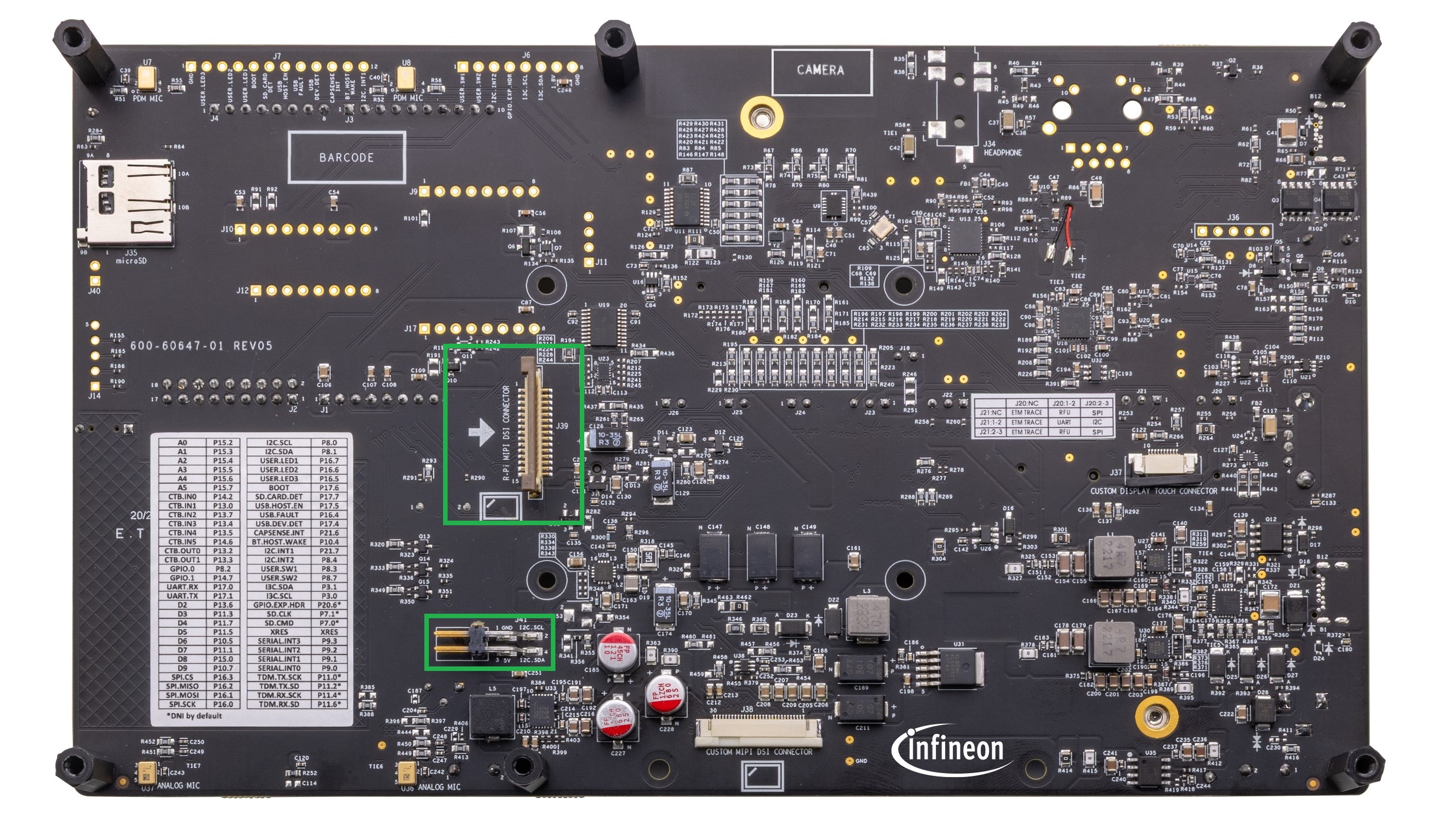

Raspberry Pi-compatible MIPI-DSI display connector (

J39

)

1

3-axis magnetometer (BMM350,

U4

)

Raspberry Pi compatible display capacitive touch connector (

J41

)

1

Linear potentiometer (

R34

)

Analog microphones (IM73A135V01XTSA1,

U36

and

U37

)

1

User LEDs (

D3

,

D4

,

D5

)

Thermistor (

TH1

)

CAPSENSE™ buttons and slider (

CSB1

,

CSB2

,

CSS1

)

Boot configuration switch (

SW6

)

Proximity sense connector (

J19

)

I/O headers compatible with Arduino UNO R3 (J2, J3, J4)

Alternative serial interface I/O header (

J14

)

Power header compatible with Arduino UNO R3 (

J1

)

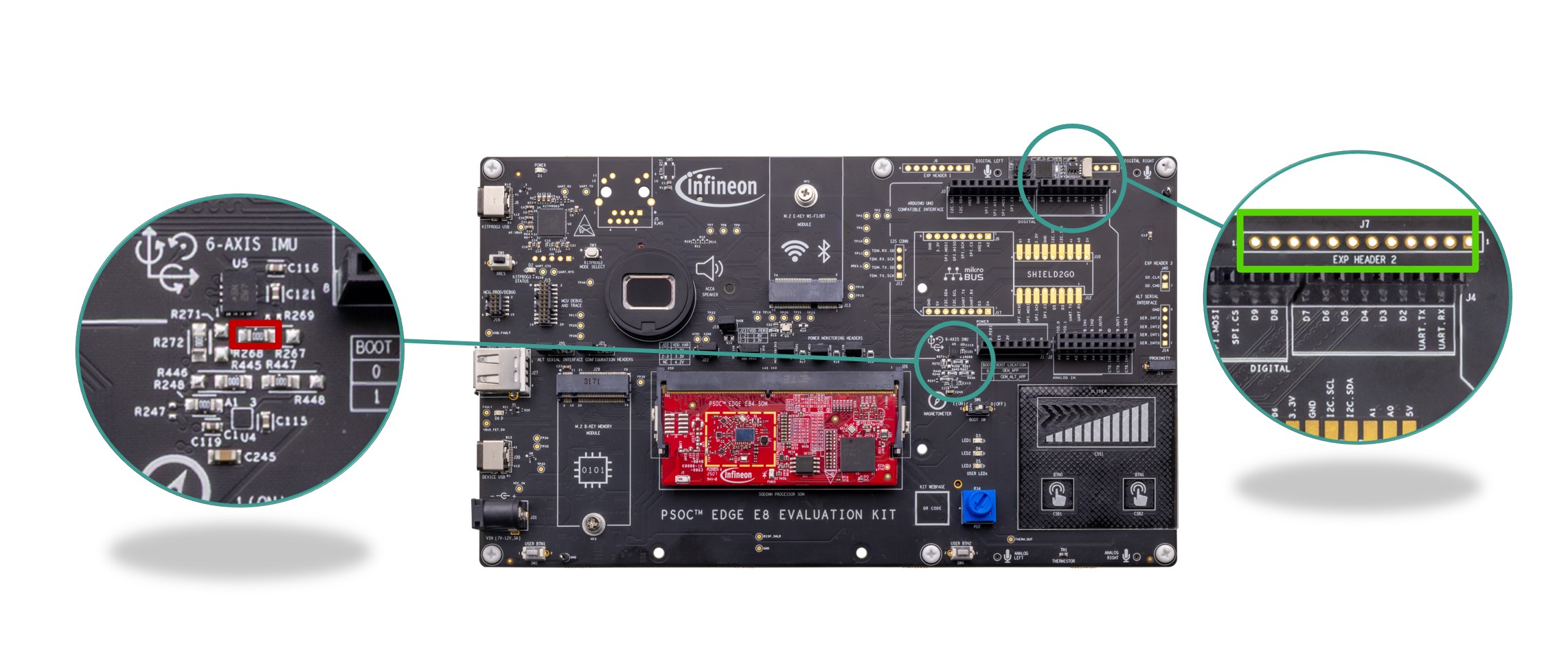

PSOC™ Edge E84 MCU expansion I/O headers (

J6

,

J7

,

J40

)

3

MicroSD card holder (

J35

)

1

Infineon's Shield2Go interface headers (

J10

,

J12

)

3

PDM microphones (IM72D128V01XTMA1,

U7

and

U8

)

1

mikroBUS-compatible headers by MikroElektronika (

J9

,

J17

)

3

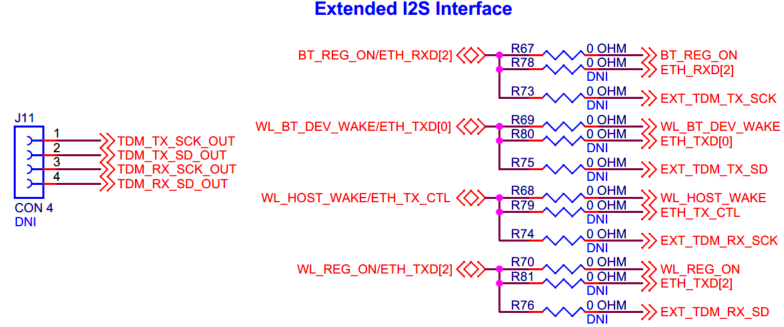

Extended I2S header (

J11

)

3

6-axis accelerometer and gyroscope IMU (BMI270,

U5

)

M.2 (E-key) radio interface connector (

J13

)

PSOC™ Edge E84 MCU power selection/monitoring headers (

J18

,

J22

,

J23

,

J24

,

J25

,

J26

)

Headphone connector (

J34

)

3

Speaker (

ACC6

)

RJ45 Ethernet MagJack connector (

J5

)

3

KitProg3 programming mode selection button (

SW3

)

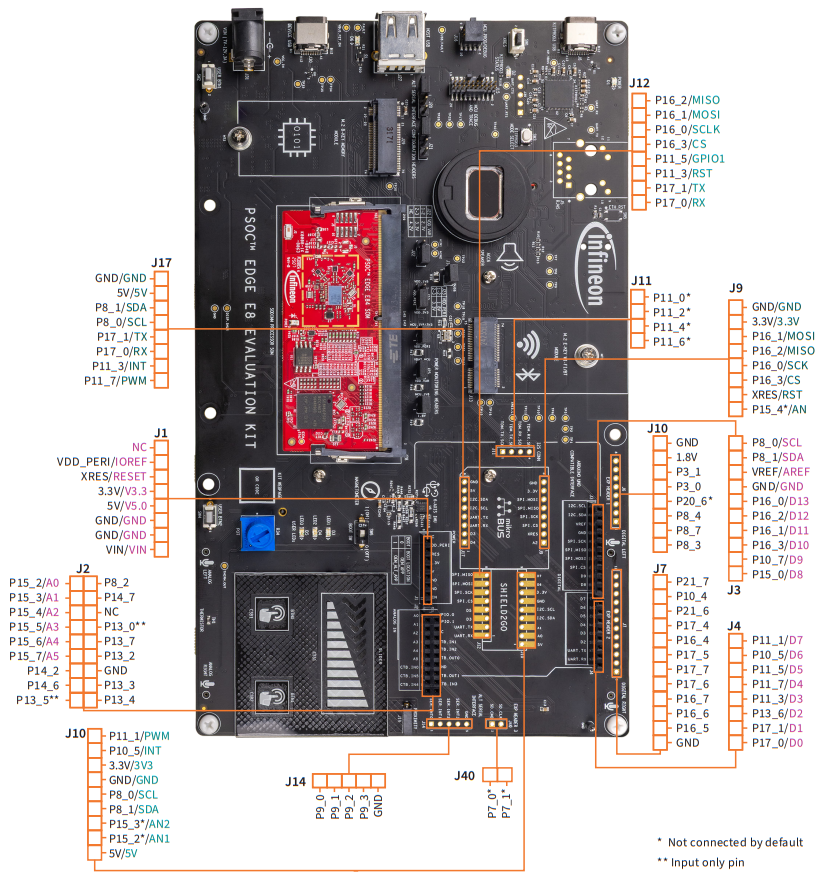

Figure 3.

PSOC™ Edge E84 board pin out details

PSOC™ Edge E84 I/O | Header | Function | Logic level |

|---|---|---|---|

P3[0] | J6.5 | I3C SCL | 1.8 V |

P3[1] | J6.4 | I3C SDA | 1.8 V |

P7[0] | J40.1 | GPIO | 1.8 V |

P7[1] | J40.2 | GPIO | 1.8 V |

P8[0] | J3.10, J17.5, J10.5 | I2C SCL pin compatible with Arduino/mikroBUS by MikroElektronika/Infineon's Shield2Go | 1.8 V (MCU side), VDD_PERI (1.8 V/3.3 V) (header side) |

P8[1] | J3.9, J17.6, J10.4 | I2C SDA pin compatible with Arduino/mikroBUS by MikroElektronika/Infineon's Shield2Go | 1.8 V (MCU side), VDD_PERI (1.8 V/3.3 V) (header side) |

P8[2] | J2.2 | GPIO0 for motor control/GPIO | 1.8 V |

P8[3] | J6.1 | User button 1 with hibernate wakeup capability, GPIO | 1.8 V |

P8[4] | J6.3 | I2C interrupt 2 pin connected to magnetometer sensor, GPIO | 1.8 V |

P8[7] | J6.2 | User button 2 with hibernate wakeup capability, GPIO | 1.8 V |

P9[0] | J14.1 | Alternate serial interface pin (SPI Chip Select/UART RTS) | 1.8 V |

P9[1] | J14.2 | Alternate serial interface pin (SPI MISO/UART CTS) | 1.8 V |

P9[2] | J14.3 | Alternate serial interface pin (SPI MOSI/I2C SDA/UART TX) | 1.8 V |

P9[3] | J14.4 | Alternate serial interface pin (SPI CLK/I2C SCL/UART RX) | 1.8 V |

P10[4] | J7.11 | Bluetooth® host wakeup pin, GPIO | 1.8 V |

P10[5] | J4.7, J10.8 | D6 pin compatible with Arduino, INT/GPIO3 pin of Infineon's Shield2Go | 1.8 V |

P10[7] | J3.2 | D9 pin compatible with Arduino | 1.8 V |

P11[0] | J11.1 | Extended I2S interface TX SCK | 1.8 V |

P11[1] | J4.8, J10.9 | D7 pin compatible with Arduino, PWM/GPIO4 pin of Infineon's Shield2Go | 1.8 V |

P11[2] | J11.2 | Extended I2S interface TX SD | 1.8 V |

P11[3] | J4.4, J17.2, J12.3 | D3 pin compatible with Arduino, INT pin compatible with mikroBUS, RST/GPIO2 pin of Infineon's Shield2Go | 1.8 V |

P11[4] | J11.3 | Extended I2S interface RX SCK | 1.8 V |

P11[5] | J4.6, J12.4 | D5 pin compatible with Arduino, GPIO1 pin of Infineon's Shield2Go | 1.8 V |

P11[6] | J11.4 | Extended I2S interface RX SD | 1.8 V |

P11[7] | J4.5, J17.1 | D4 pin compatible with Arduino, PWM pin compatible with mikroBUS | 1.8 V |

P13[0] | J2.8 | CTB IN1 pin for motor control/GPIO | 1.8 V |

P13[2] | J2.12 | CTB OUT0 pin for motor control/GPIO | 1.8 V |

P13[3] | J2.16 | CTB OUT1 pin for motor control/GPIO | 1.8 V |

P13[4] | J2.18 | CTB IN3 pin for motor control/GPIO | 1.8 V |

P13[5] | J2.17 | CTB IN4 pin for motor control/GPIO | 1.8 V |

P13[6] | J4.3 | D2 pin compatible with Arduino | 1.8 V |

P13[7] | J2.10 | CTB IN2 pin for motor control/GPIO | 1.8 V |

P14[1] | J6.6 | CTB/GPIO3 pin | 1.8 V |

P14[2] | J2.13 | CTB IN0 pin for motor control/GPIO | 1.8 V |

P14[3] | J6.8 | CTB/GPIO1 pin | 1.8 V |

P14[5] | J6.7 | CTB/GPIO2 pin | 1.8 V |

P14[6] | J2.15 | CTB IN5/DAC0 pin for motor control/GPIO | 1.8 V |

P14[7] | J2.4 | GPIO1 for motor control/GPIO | 1.8 V |

P15[0] | J3.1 | D8 pin compatible with Arduino | 1.8 V |

P15[2] | J2.1, J10.2 | A0 pin compatible with Arduino, AN1 pin of Infineon's Shield2Go | 1.8 V |

P15[3] | J2.3, J10.3 | A1 pin compatible with Arduino, AN2 pin of Infineon's Shield2Go | 1.8 V |

P15[4] | J2.5, J9.1 | A2 pin compatible with Arduino, AN pin compatible with mikroBUS | 1.8 V |

P15[5] | J2.7 | A3 pin compatible with Arduino | 1.8 V |

P15[6] | J2.9 | A4 pin compatible with Arduino | 1.8 V |

P15[7] | J2.11 | A5 pin compatible with Arduino | 1.8 V |

P16[0] | J3.6, J9.4, J12.6 | SPI SCK pin compatible with Arduino | VDD_PERI (1.8 V/3.3 V) |

P16[1] | J3.4, J9.6, J12.7 | SPI MOSI pin compatible with Arduino/mikroBUS by MikroElektronika/Infineon's Shield2Go | VDD_PERI (1.8 V/3.3 V) |

P16[2] | J3.5, J9.5, J12.8 | SPI MISO pin compatible with Arduino/mikroBUS by MikroElektronika/Infineon's Shield2Go | VDD_PERI (1.8 V/3.3 V) |

P16[3] | J3.3, J9.3, J12.5 | SPI CS pin compatible with Arduino/mikroBUS by MikroElektronika/Infineon's Shield2Go | VDD_PERI (1.8 V/3.3 V) |

P16[4] | J7.8 | USB host fault report pin, GPIO | VDD_PERI (1.8 V/3.3 V) |

P16[5] | J7.2 | USER LED 3 pin, GPIO | VDD_PERI (1.8 V/3.3 V) |

P16[6] | J7.3 | USER LED 2 pin, GPIO | VDD_PERI (1.8 V/3.3 V) |

P16[7] | J7.4 | USER LED 1 pin, GPIO | VDD_PERI (1.8 V/3.3 V) |

P17[0] | J4.1, J17.3, J12.1 | UART RX pin compatible with Arduino/mikroBUS by MikroElektronika/Infineon's Shield2Go | VDD_PERI (1.8 V/3.3 V) |

P17[1] | J4.2, J17.4, J12.2 | UART TX pin compatible with Arduino/mikroBUS by MikroElektronika/Infineon's Shield2Go | VDD_PERI (1.8 V/3.3 V) |

P17[4] | J7.9 | USB device VBUS detect pin, GPIO in header | VDD_PERI (1.8 V/3.3 V) |

P17[5] | J7.7 | USB host enable pin, GPIO | VDD_PERI (1.8 V/3.3 V) |

P17[6] | J7.5 | BOOT select pin, GPIO | VDD_PERI (1.8 V/3.3 V) |

P17[7] | J7.6 | SD card detect pin, GPIO | VDD_PERI (1.8 V/3.3 V) |

P21[6] | J7.10 | CAPSENSE™ INT pin, GPIO | 1.8 V |

P21[7] | J7.12 | I2C interrupt 1 pin connected to 6-axis IMU sensor, GPIO | 1.8 V |

Additional learning resources

Infineon provides a wealth of data in the

PSOC™ Edge E84

webpage to:

Select the right PSOC™ device for the design

Quickly and effectively integrate the device into the design

Technical support

For assistance, go to Infineon

support

page. Visit

Infineon Developer Community

to ask any product-related questions.

User can also use the following support resources if you need quick assistance:

Documentation conventions

Convention | Usage |

|---|---|

Courier New | Displays user-entered text and source code |

Italics | Displays file names and reference documentation: Read about the sourcefile.hex file in the PSOC™ Creator user guide . |

File > Open | Represents menu paths: File > Open > New Project |

Bold | Displays commands, menu paths, and icon names in procedures: Click the File icon and then click Open . |

Times New Roman | Displays an equation: 2 + 2 = 4 |

Text in gray boxes | Describes Cautions or unique functionality of the product. |

Kit operation

Theory of operation

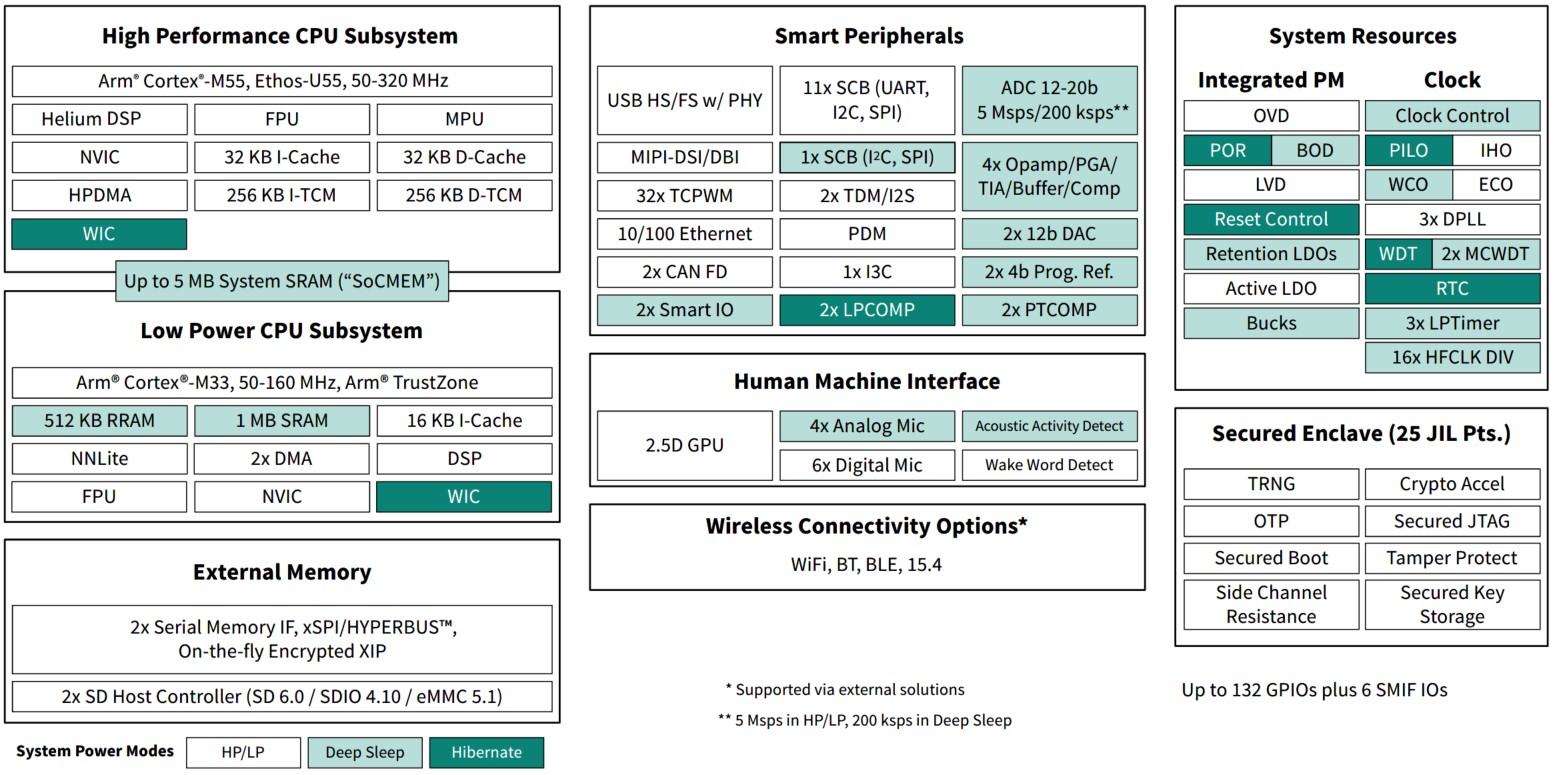

The PSOC™ Edge E84 EVK is built around a PSOC™ Edge E84.

Figure 4

shows the Architecture block diagram of the PSOC™ Edge E84 MCU used on the board. For details of device features, see the

datasheet

.

Figure 4.

PSOC™ Edge E84 MCU block diagram

Figure 5.

PSOC™ Edge E84 Evaluation Board top-level block diagram

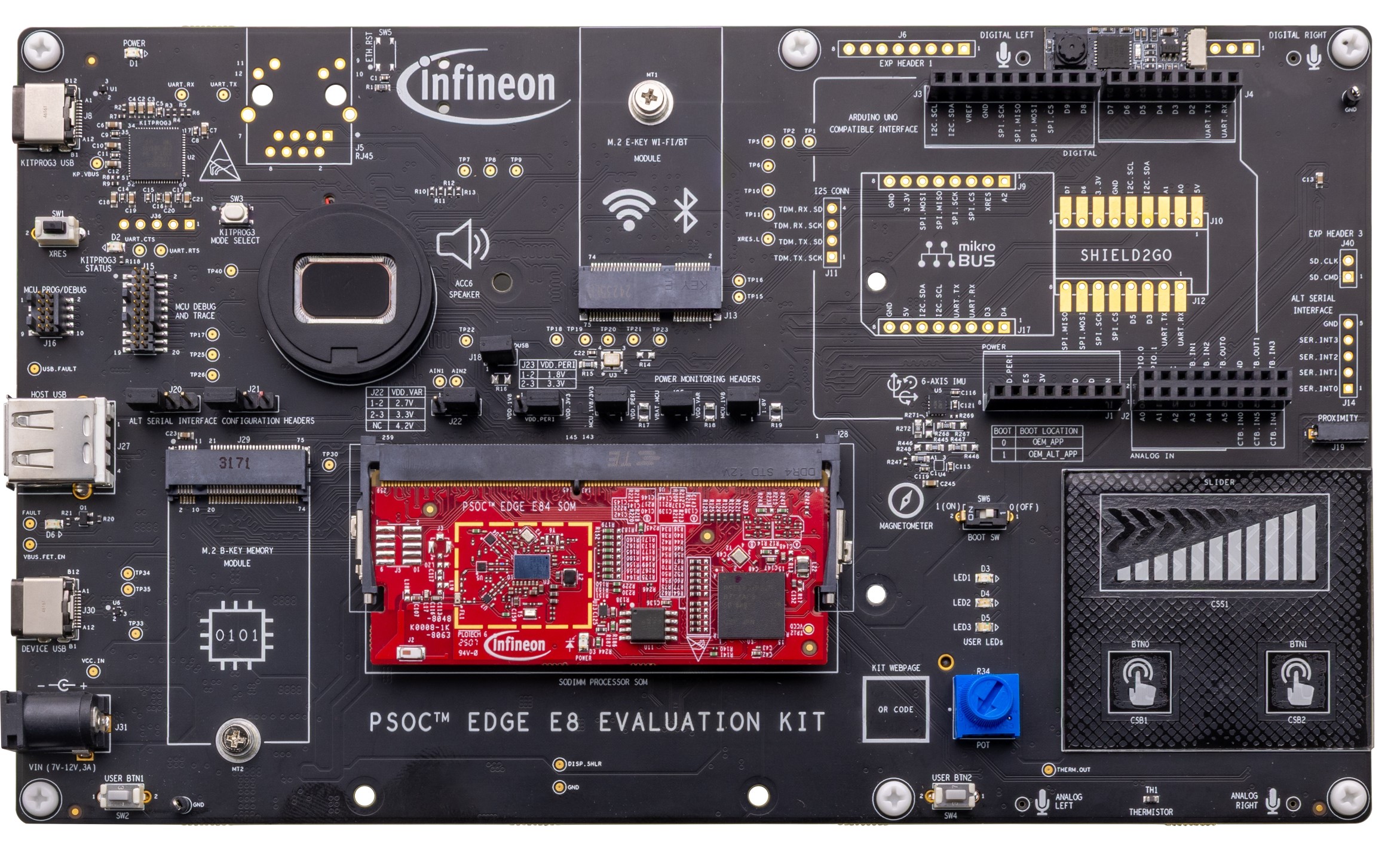

Figure 6.

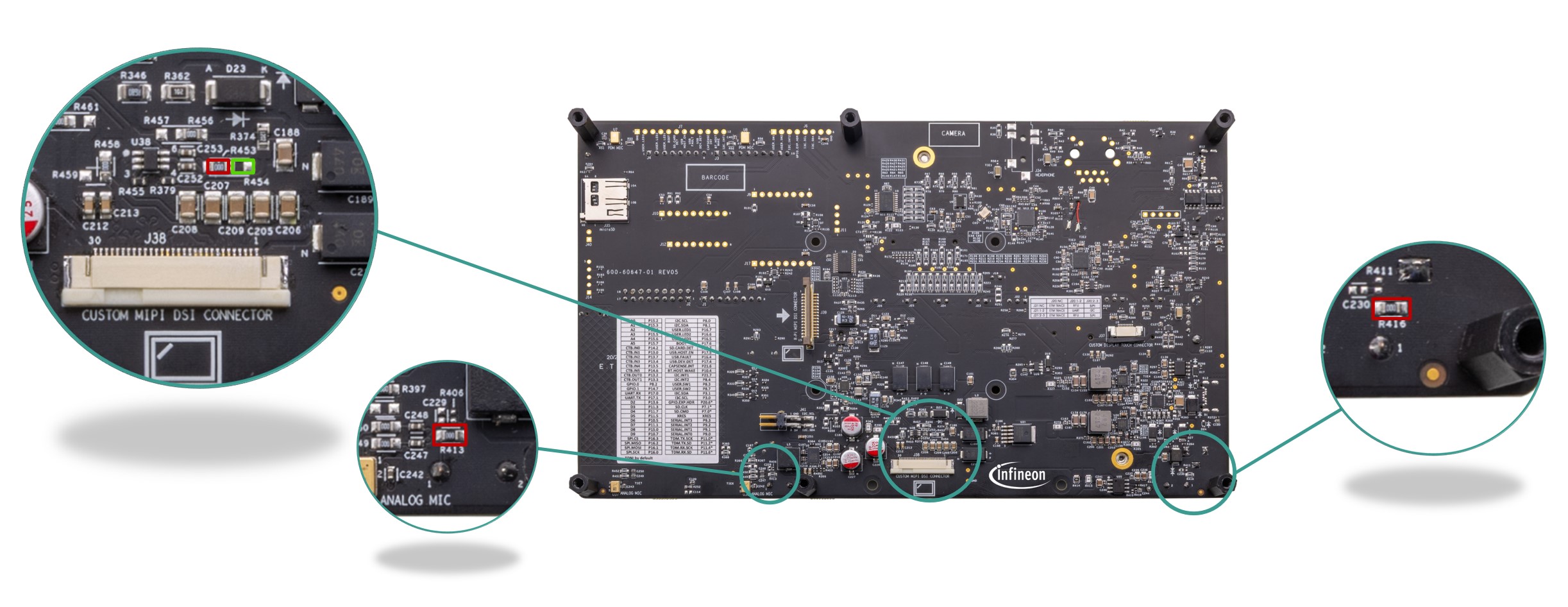

Baseboard top view with SOM connected

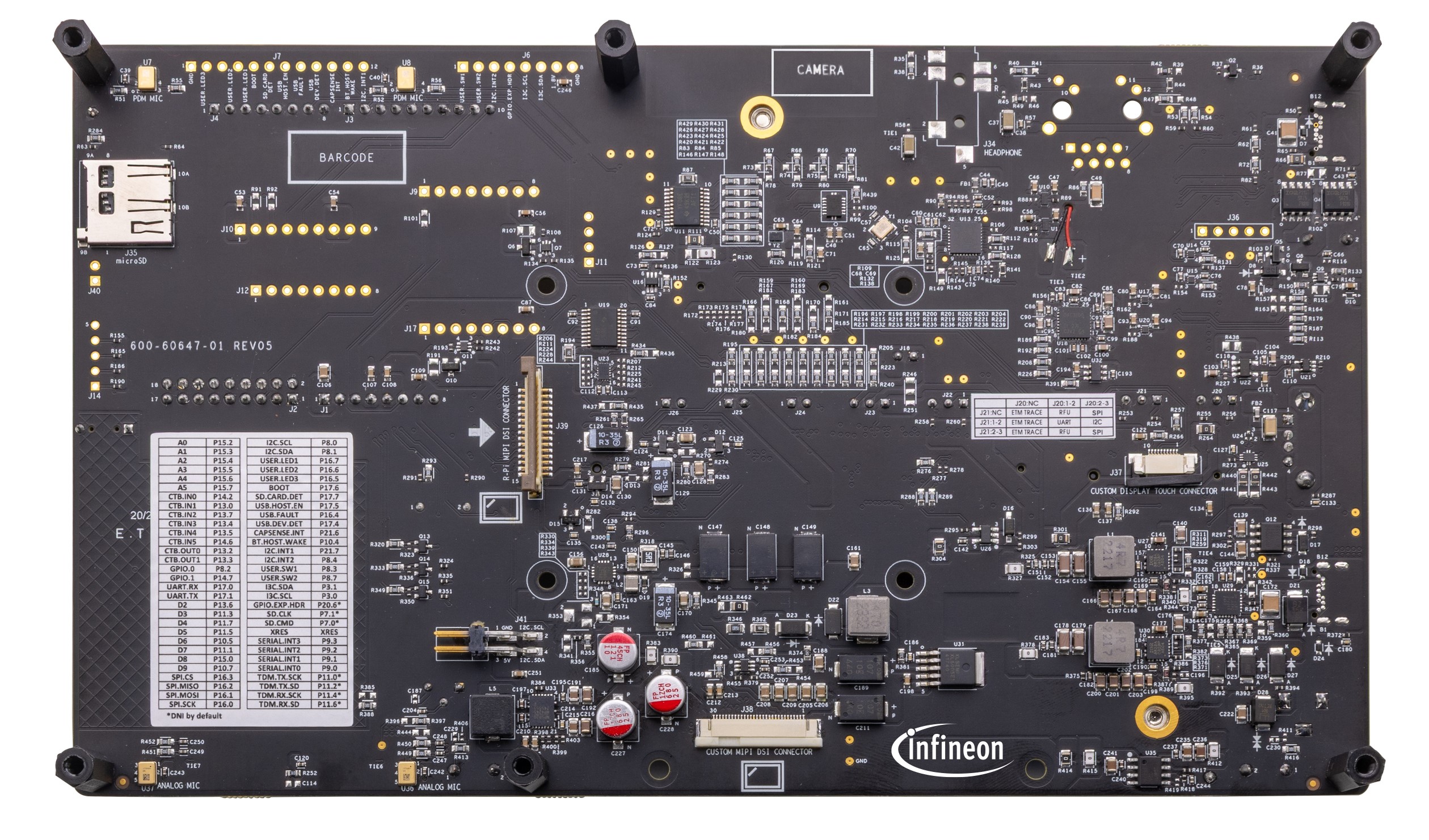

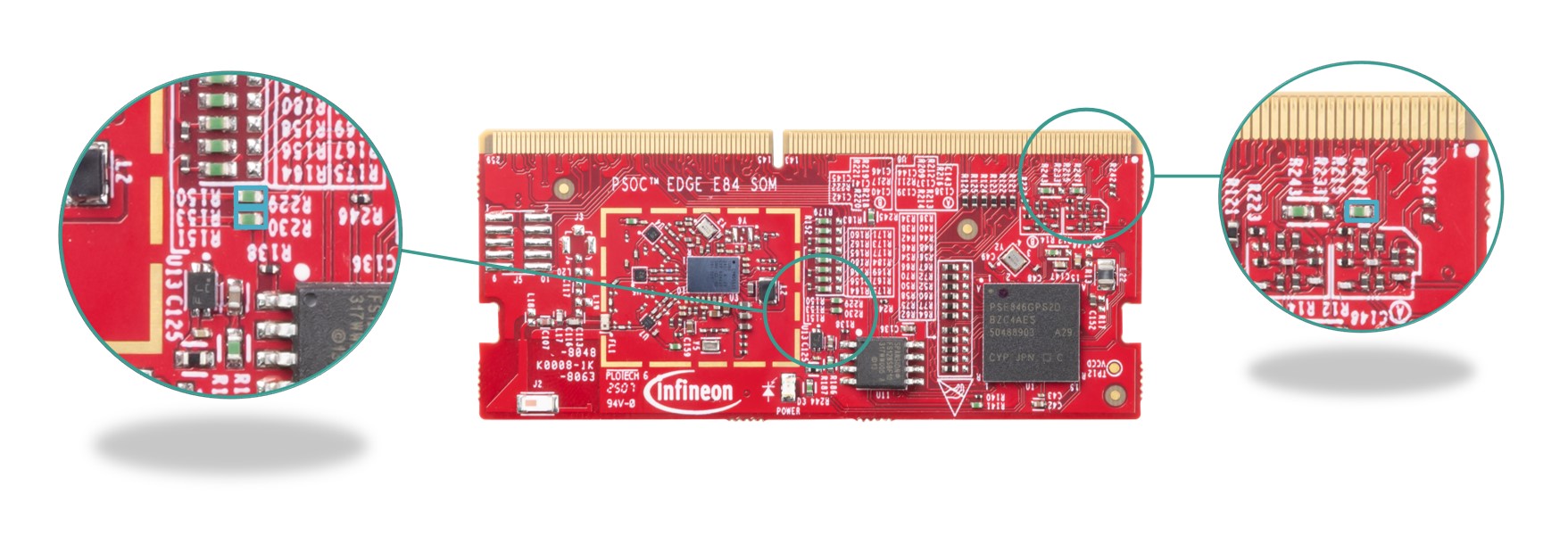

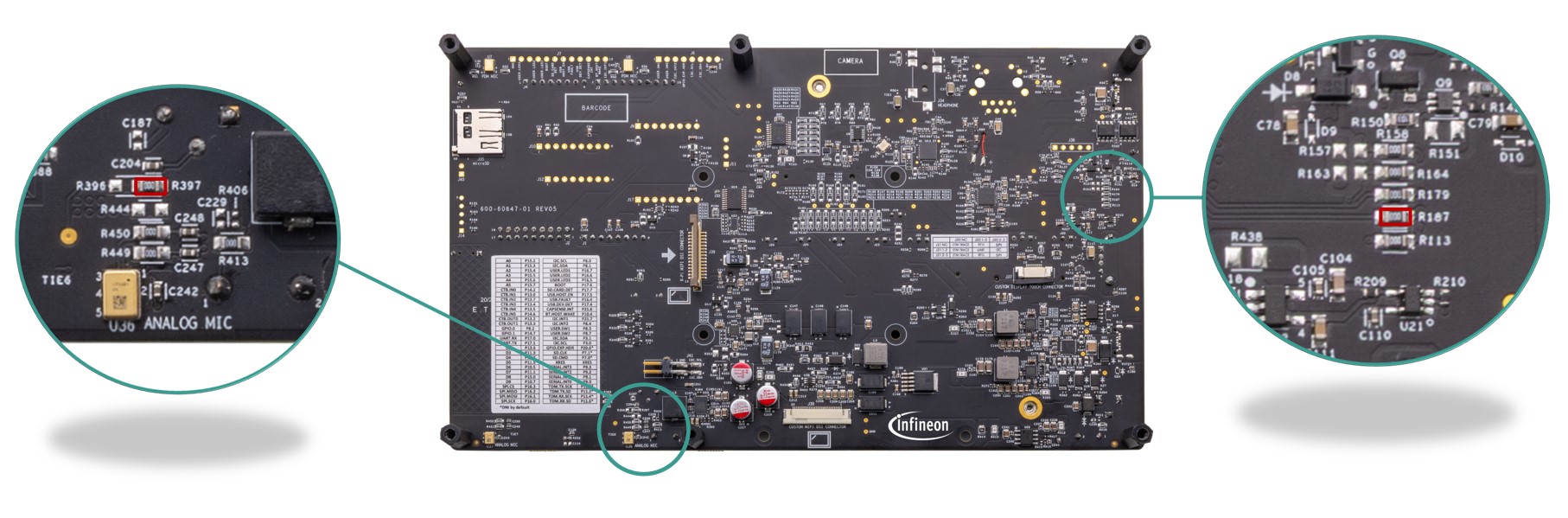

Figure 7.

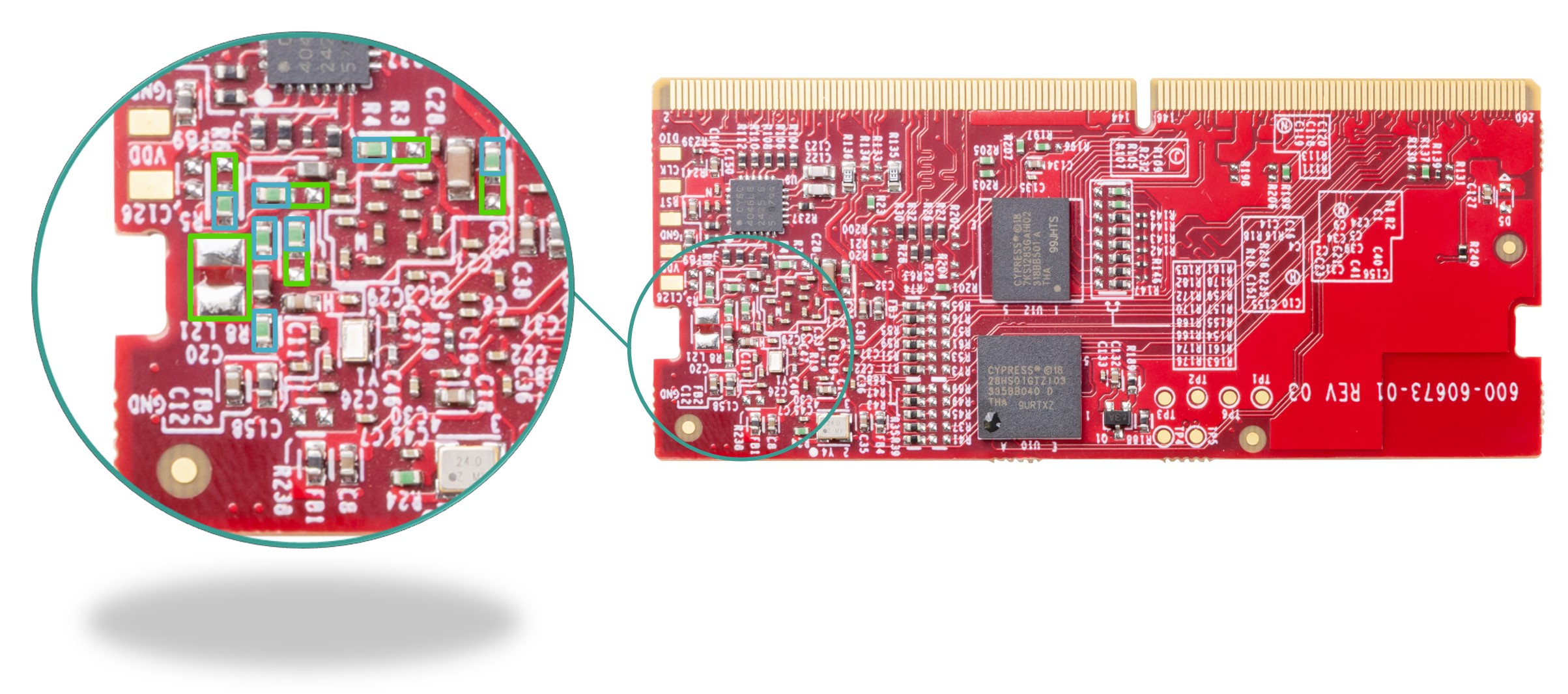

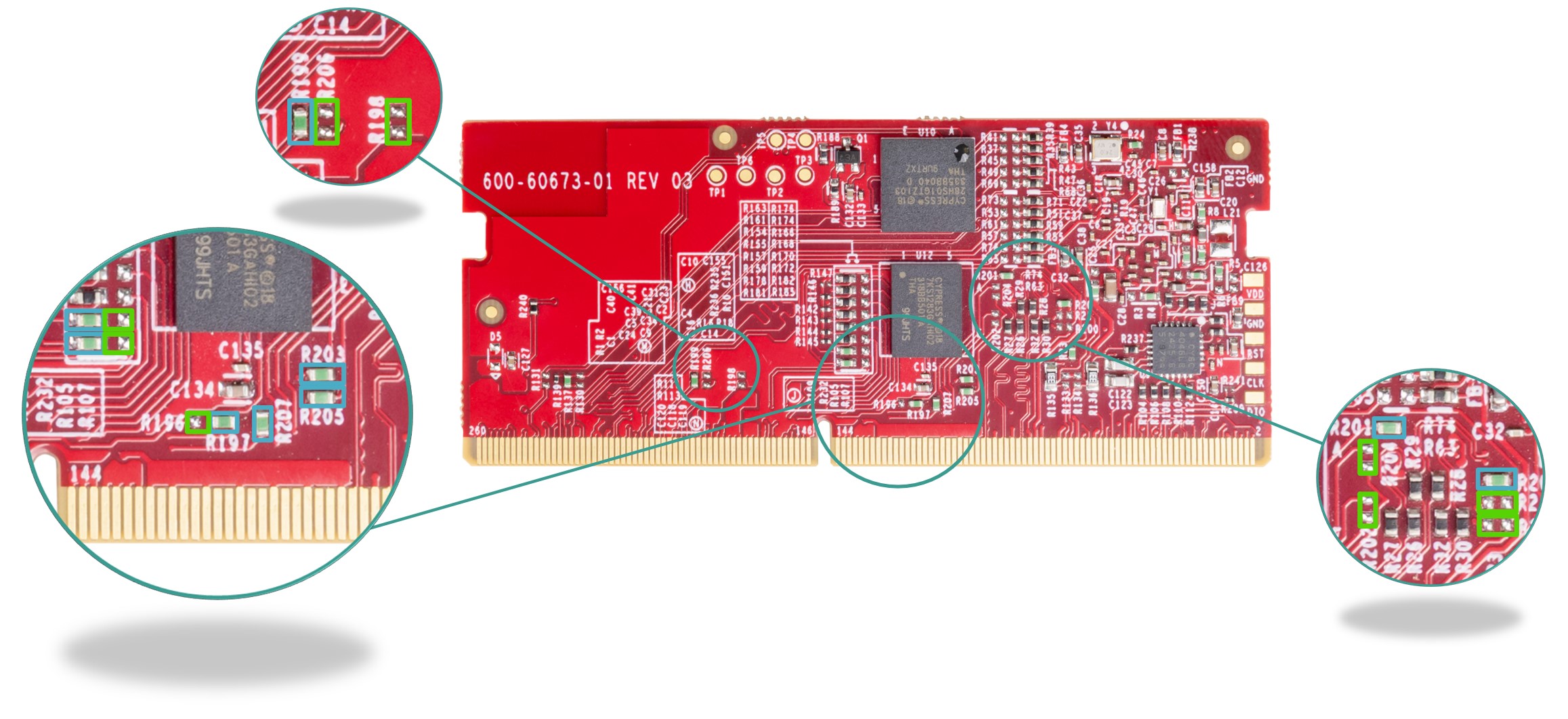

Baseboard bottom view

Figure 8.

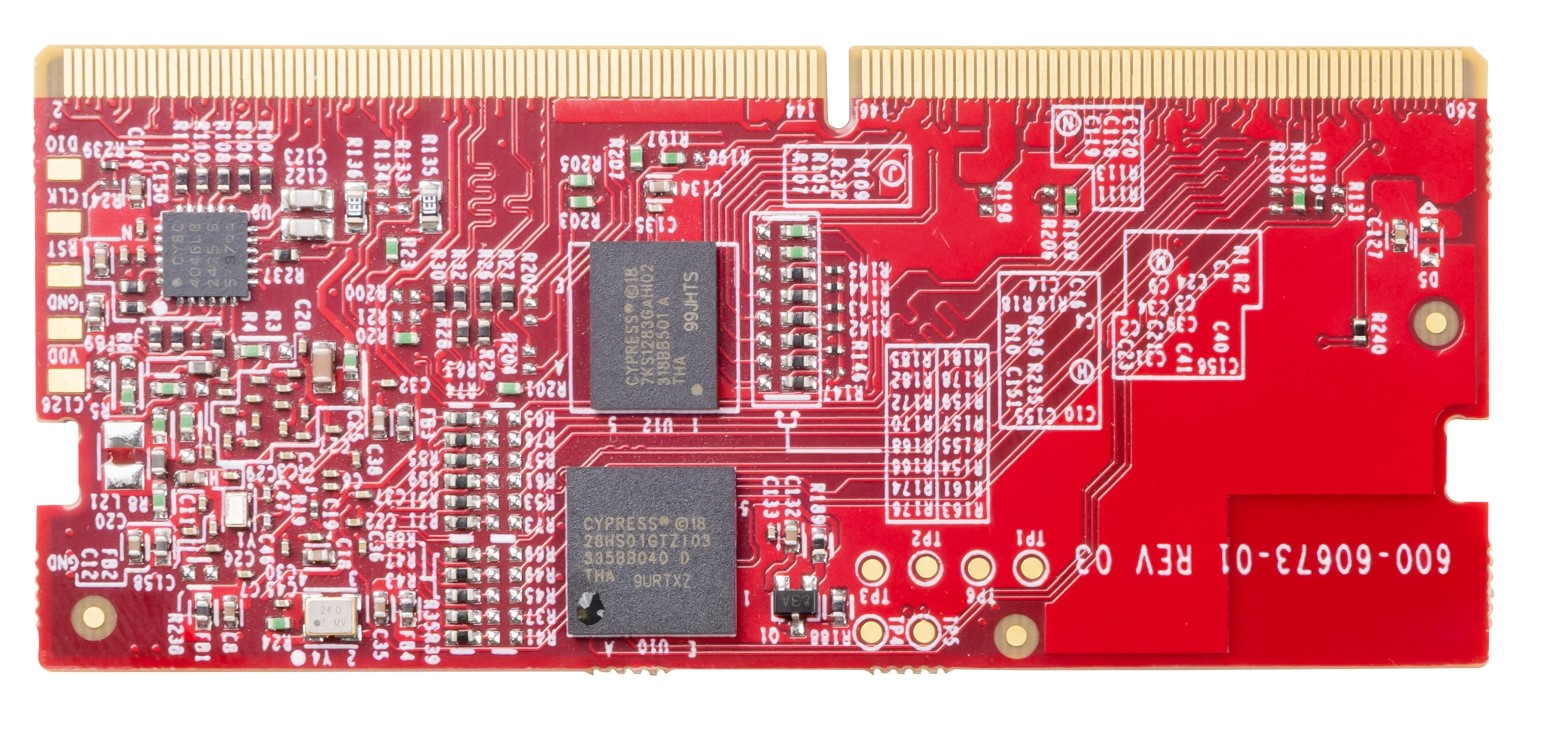

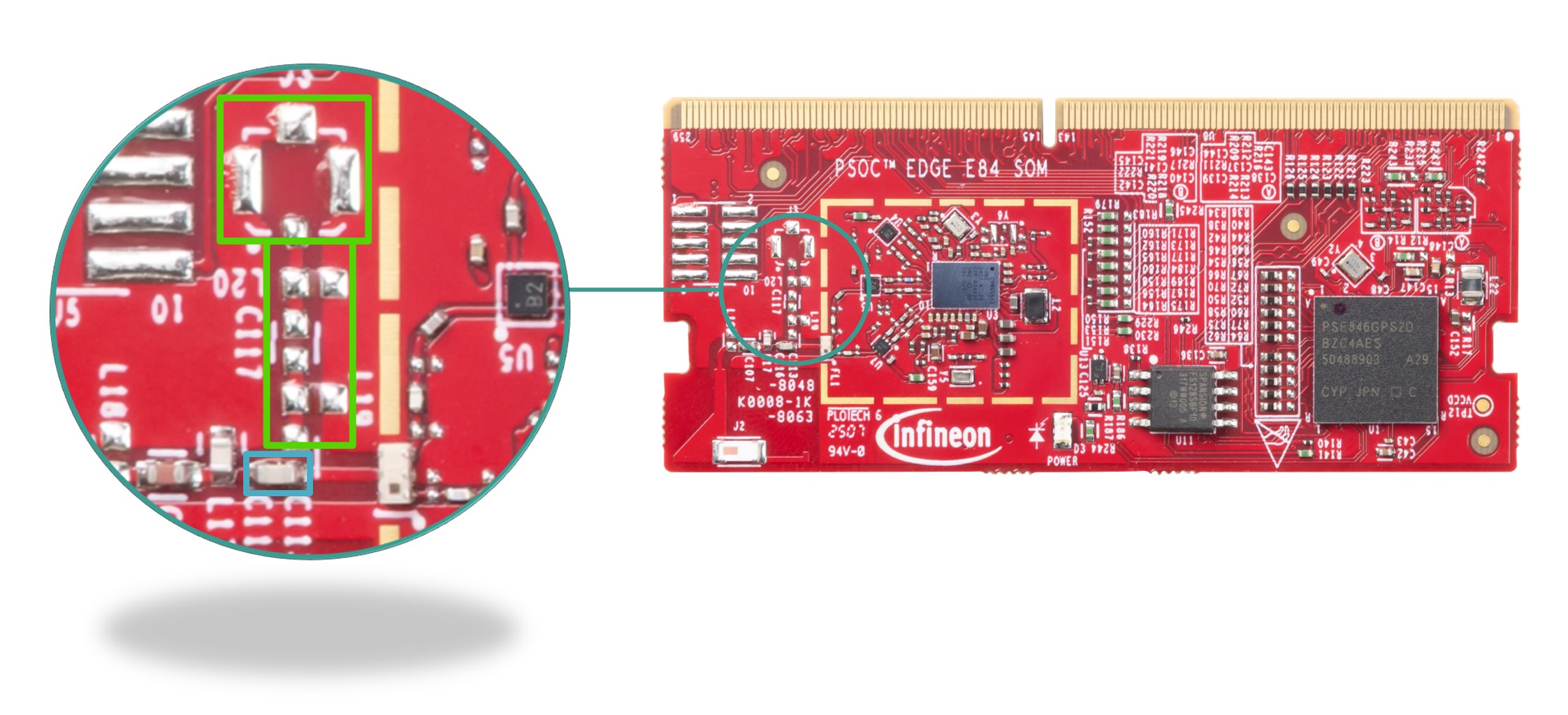

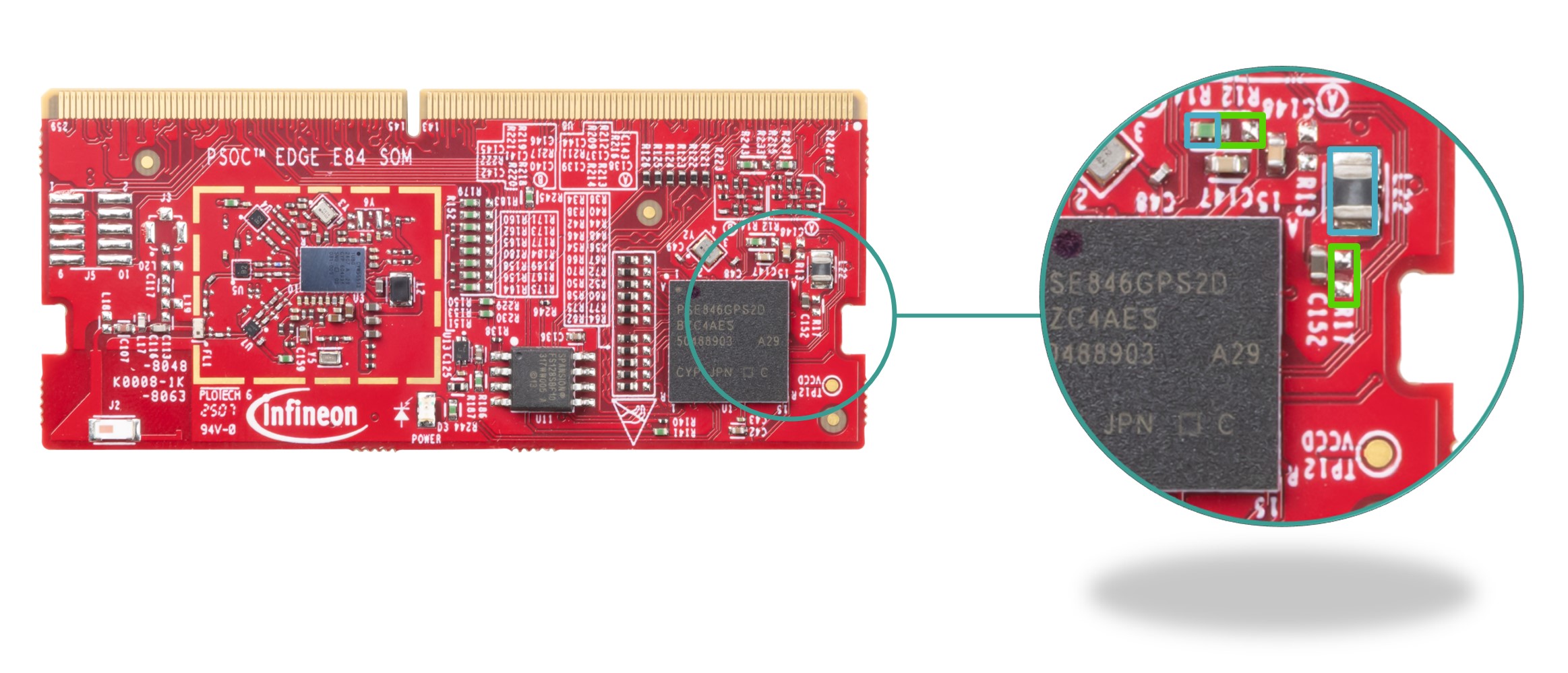

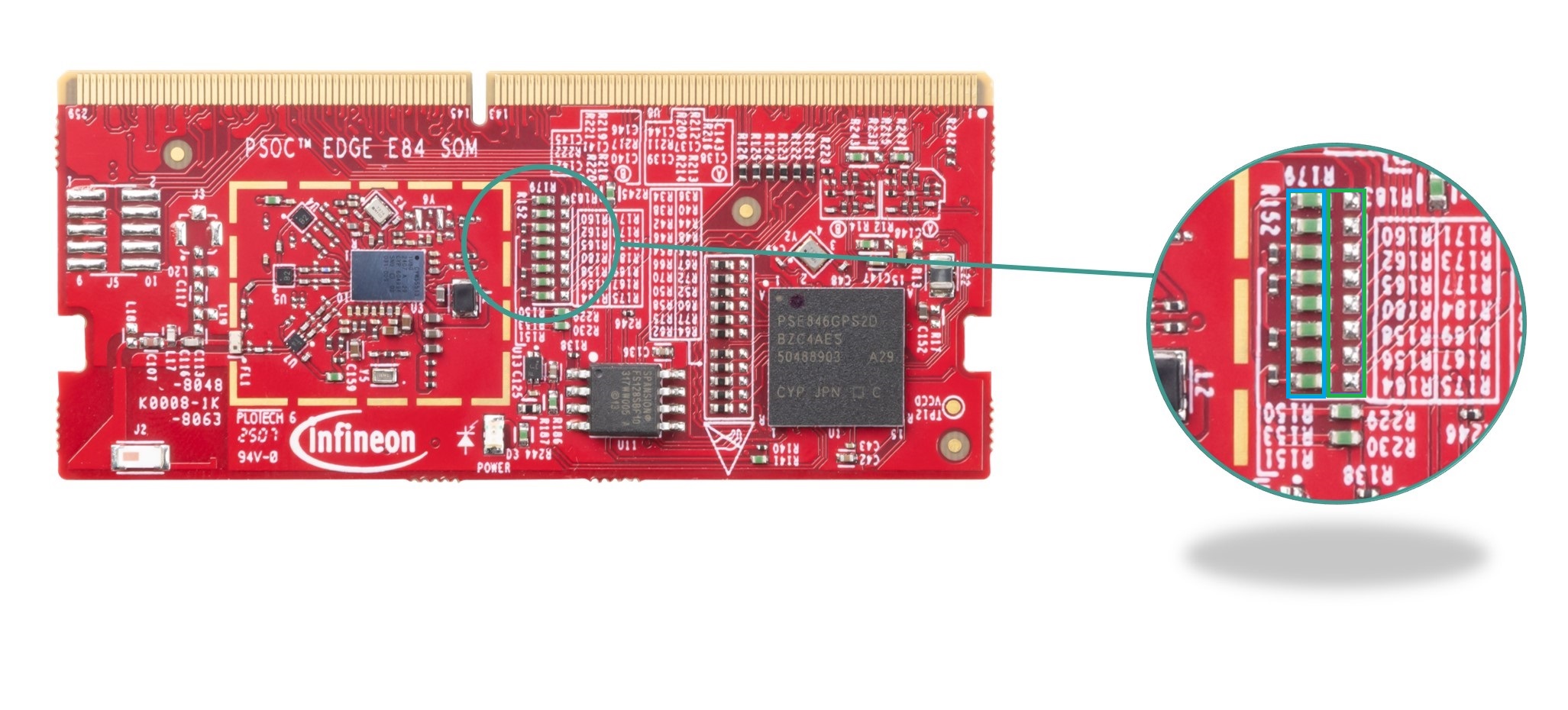

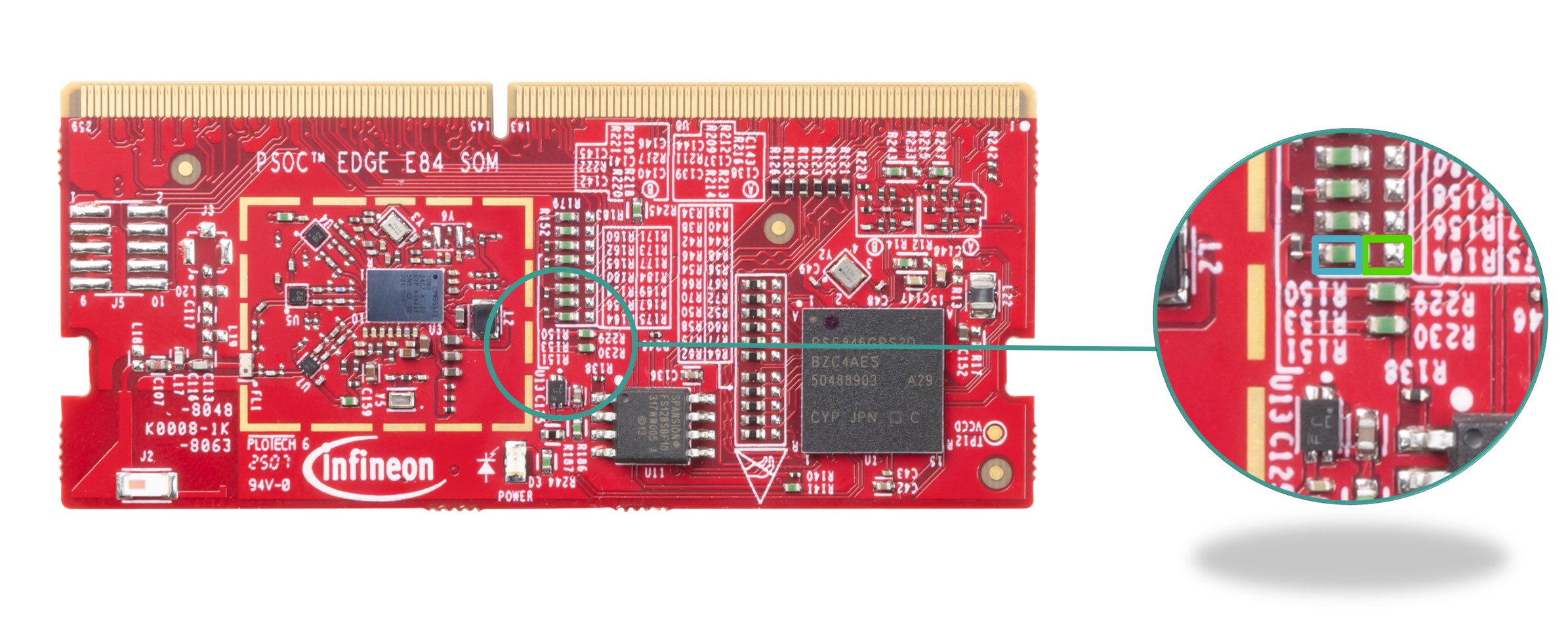

PSOC™ Edge E84 SOM (top view)

Figure 9.

PSOC™ Edge E84 SOM (bottom view)

lists the kit peripherals.

SI. No. | Peripheral | Description |

|---|---|---|

Power LED (D1) | Amber LED that indicates the status of the power supplied to board. | |

KitProg3 Program/Debug USB Type-C connector (J8) | Use the USB cable provided along with the EVK to connect the board to a PC to power(5 V, maximum 3 A) the board and program/debug using the KitProg3 onboard programmer and debugger. | |

PSOC™ 5LP based KitProg3 programmer and debugger (CY8C5868LTI-LP039, U2) | The PSOC™ 5LP MCU (CY8C5868LTI-LP039) serving as KitProg3, is a multifunctional system, which includes a SWD programmer, debugger, USB-I2C bridge and USB-UART bridge. KitProg3 also supports custom applications. For more details, see the KitProg3 User Guide . | |

Reset button (SW1) | This button resets the PSOC™ Edge E84 MCU. It connects the PSOC™ Edge E84 MCU reset (XRES) pin to the ground when pressed. | |

KitProg3 status LED (D2) | Amber LED (D2) indicates the status of KitProg3. For details on the KitProg3 status, see the KitProg3 User Guide . By default, this LED should be ON which indicates CMSIS-DAP/Bulk mode. | |

PSOC™ Edge E84 MCU ETM/JTAG debug and trace header (J15) | This 20-pin header provision allows for JTAG debug and ETM trace for instruction/data tracing in PSOC™ Edge E84 MCU. | |

PSOC™ Edge E84 MCU program and debug interface header (J16) | This 10-pin standard SWD/JTAG header provision allows to interface external programmers such as MiniProg4 for programming and debugging. | |

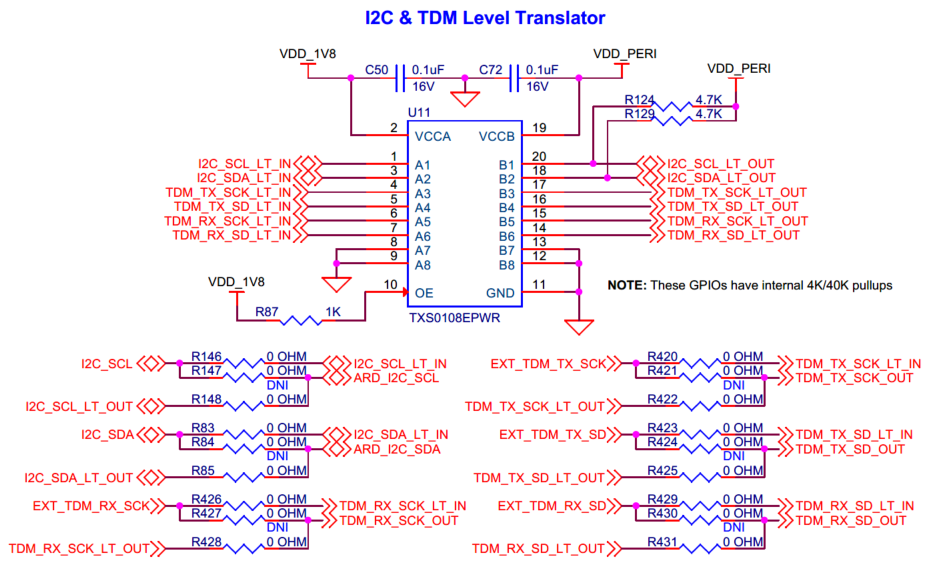

Alternative serial interface configuration headers (J20, J21) | Configuration headers for ETM trace data line 2 and trace data line 3. These lines are used to configure alternate serial interfaces like I2C, UART, SPI | |

PSOC™ Edge E84 MCU USB Host Type-A connector (J27) | A USB Type-A cable can be connected between this USB connector and the PC to use the PSOC™ Edge E84 MCU USB Host applications. | |

USB Type-C PD connector Fault LED (D6) | USB Type-C Fault detect LED | |

11 | Custom display Capacitive Touch Panel connector (J37) | Touch connector for custom display for HMI (Human Machine Interface) applications, such as wearables. |

12 | PSOC™ Edge E84 MCU USB device Type-C connector (J30) | Use this USB connector to connect to a PC for using the PSOC™ Edge E84 MCU USB device applications. This connector can be used to power the kit at higher voltage and current, it supports PD at 15 V, maximum 3 A or 5 V, maximum 3 A |

13 | External power supply VIN connector (J31) | Connects an external DC power supply input to the on-board regulators. Input Range is 7 V to 12 V for this VIN supply. |

14 | PSOC™ Edge E84 MCU user buttons (SW2, SW4) | Provides an input to PSOC™ Edge E84 MCU. Note that the button connects the PSOC™ Edge E84 MCU pin to ground when pressed by default. Therefore, configure the MCU pin as a digital input with resistive pull-up for detecting the button press. These buttons also provide a wake-up source from low-power modes of the device. |

M.2 (B-key) memory interface connector (J29) | M.2 B-Key socket to interface M.2 compatible external flash and PSRAM interfaces to PSOC™ Edge E84 MCU. | |

Processor SoM 260-pin SODIMM connector (J28) | SODIMM connector header for connecting MCU SoM module | |

128-Mbit Octal-SPI HYPERRAM™ (U12) | 128 Mb HYPERRAM™ device is a high-speed CMOS, self-refresh DRAM, The HYPERRAM™ device provides an xSPI (Octal) slave interface to the host system. The xSPI (Octal) interface has an 8-bit (1 byte) wide DDR data bus and use only word-wide (16-bit data) address boundaries. | |

CYW55513 Tri-band (Wi-Fi/Bluetooth®) Combo Radio (U3) | Onboard AIROC™ Wi-Fi and Bluetooth® combo for connectivity applications, supports Bluetooth® 5.4 and Wi-Fi 6/6E | |

R-Pi compatible MIPI-DSI display connector (J39) | Connector header for R-Pi compatible displays. | |

1-Gbit Octal-SPI NOR Flash (U10) | 1-Gbit high-speed CMOS, MIRRORBIT™ NOR flash devices support both the octal peripheral interface (OPI) as well as legacy connection signals. | |

MIPI-DSI custom display connector (J38) | Generic connector header for MIPI-DSI compatible displays for HMI (Human Machine Interface) applications, such as wearables. | |

128-Mbit Quad-SPI NOR Flash (U11) | 128-Mbit non-volatile memory, connects to a host system via a SPI interface. The memory is ideal for code shadowing to RAM, executing code directly, execute code in place (XIP), and storing reprogrammable data. | |

PSOC™ Edge E84 MCU (220-BGA, U1) | This kit is designed to highlight the features of the PSOC™ E84 MCU. For details on PSOC™ E84 MCU pin mapping, refer to Table 2 | |

PSOC™ 4000T CAPSENSE™ Coprocessor (U9) | PSOC™ 4000T as onboard Co-processor for CAPSENSE™ feature enablement, connected to MCU via I2C interface | |

6-axis Accelerometer and Gyroscope IMU (U5) | BMI270 is a 6-axis IMU with Accelerometer and Gyroscope combination which is interfaced to PSOC™ Edge E84 MCU over I2C serial interface. | |

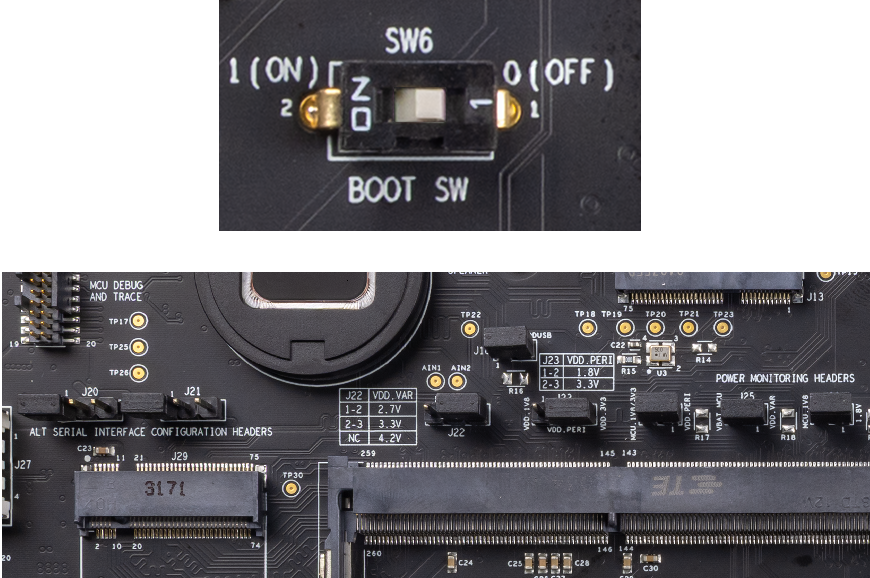

PSOC™ Edge E84 MCU Boot Select (SW6) | Based on this switch's configuration the MCU can boot from one of the following boot sources - External FLASH or Internal RRAM. | |

Linear Potentiometer (R34) | 10 KΩ potentiometer connected to PSOC™ Edge E84 MCU pin P15[1]. It can be used to simulate an analog sensor output to PSOC™ Edge E84 MCU. | |

Analog microphones (U36, U37) | Onboard analog microphones for Voice User Interface (VUI) applications like smart speakers, home automation and IoT devices. | |

User LEDs (D3, D4, D5) | Can be controlled by the PSOC™ Edge E84 MCU. The LEDs are active HIGH, so the pins must be driven to logic level 1 to turn ON the LEDs. | |

Thermistor (TH1) | This thermistor can be used for temperature compensation or as a general purpose ambient temperature sensor (MCU pin is not connected to thermistor by default. See rework section for more details) | |

CAPSENSE™ buttons and slider (CSB1, CSB2, CSS1) | The CAPSENSE™ touch-sensing slider and two buttons, all of which are capable of both self-capacitance (CSD) and mutual-capacitance (CSX) operation, allow you to evaluate Infineon’s fourth-generation CAPSENSE™ technology. The slider and buttons have a 1 mm acrylic overlay for smooth touch sensing. | |

Proximity sense connector (J19) | Connector for capacitive proximity sense. | |

Arduino UNO R3 compatible I/O headers (J2, J3, J4) | Brings out pins from PSOC™ Edge E84 MCU to interface with shields compatible with Arduino. Some of these pins are multiplexed with on-board peripherals. For a detailed information on how to rework the kit to access other functions, see Table 2 . | |

Arduino UNO R3 compatible power header (J1) | Powers the shields compatible with Arduino. It also has a provision to power the kit though the VIN input. | |

Alternative serial interface I/O header (J14) | Header for alternate serial interface I/Os | |

microSD card holder (J35) | Provides SDHC interface with microSD cards with the option to detect the presence of the card. | |

Infineon’s Shield2Go interface headers (J10, J12) | The Header provides an easy plug and play interfacing of Infineon's Shield2Go boards. Some pins of this connector is not connected to MCU by default. Check the rework section for more details. | |

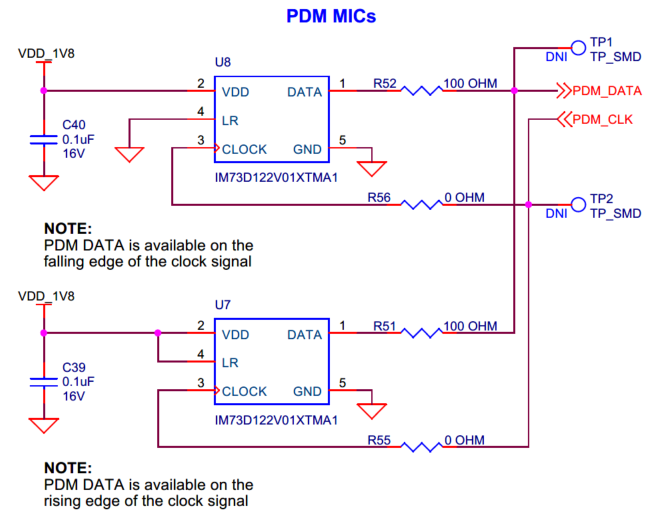

PDM microphones (U7, U8, Bottom) | Two microphones convert voice inputs to Pulse-Density Modulated (PDM) digital signals. | |

PSOC™ Edge E84 MCU expansion I/O headers (J6, J7, J40) | Provide connectivity to PSOC™ Edge E84 MCU GPI/Os. Some of these I/Os are also connected to on-board peripherals. See Table 2 for pin mapping. This is not loaded by default. | |

mikroBUS compatible headers by MikroElektronika (J9, J17) | Interfaces add-on boards compatible with mikroBUS by MikroElektronika. Some pins of this connector is not connected to MCU by default. Check the rework section for more details. | |

Extended I2S header (J11) | Provides I2S(TDM) output signals. This connector is not populated by default on the kit | |

3-axis Magnetometer (U4) | BMM350 is a 3-axis Magnetometer which is interfaced to PSOC™ Edge E84 MCU over I3C serial interface. | |

M.2 (E-key) radio interface connector (J29) | M.2 (E-key) radio interface connector (J29): M.2 E-Key socket to interface compatible AIROC™ Wi-Fi & Bluetooth® combo M.2 radio modules. | |

PSOC™ Edge E84 MCU power selection/monitoring headers (J18, J22, J23, J24, J25, J26) | Headers for configuring power domains like MCU and peripheral power domain. Also, this hardware section has power measurement jumpers, connect an ammeter to these jumpers to measure current in the respective power domains. | |

Headphone connector (J34) | Headphone Jack Stereo connector. This connector is not populated by default on the kit | |

Speaker (ACC6) | On-board 8Ω speaker with 8W output. | |

RJ45 Ethernet MagJack connector (J5) | RJ45 Ethernet connector port to connect the kit to an ethernet network. This connector is not populated by default on the kit | |

KitProg3 programming mode selection button (SW3) | This button can be used to switch between various modes of operation of KitProg3 (CMSIS-DAP/Bulk or CMSIS-DAP/HID mode). For more details, see the KitProg3 User Guide . By default, the programming mode is set to CMSIS-DAP/Bulk which allows faster programming than CMSIS-DAP/HID. |

See

Hardware functional description

for details on various hardware blocks.

Using the OOB example

The PSOC™ Edge E84 evaluation kit is by default programmed with the code example: PSOC™ E84 MCU: PSOC™ E84 OOB demo app. The following steps describe on how to use the example. For a detailed description of the project refer to the example’s

README.md

file in the GitHub repository. The

README.md

file is also in the application directory once the application is created.

Note:

At any point of time, if you overwrite the OOB example, you can restore it by programming the PSOC™ E84 MCU: PSOC™ E84 OOB demo app.

Before you start ensure that you have the following:

PC with USB Type-C port. (In case USB Type C port is absent in PC use a USB Type-A to USB Type-C connector cable which is not provided with EVK)

Attach camera module to preferred location (Image shows the recommended location on baseboard)

Before attaching the camera, ensure the PCB surface is clean and free of debris. If necessary, use a soft cloth and a cleaning solution to gently wipe the surface

Gently peel the cover away from the 3M tape

Carefully align the camera module with the preferred mounting area on the baseboard

Once the camera is aligned, gently press it onto the baseboard

Remove protective film from Camera lens

Connect the 4 pin connector of camera's USB cable to camera module

Figure 10.

Camera Module placement

Connect and power up the board

Ensure that the Boot configuration switch (SW6) is in OFF position

Ensure that jumpers are set to their default positions as below:

J22, J23: 2-3

J18, J24, J25, J26: SHORT

J20, J21: OPEN

Connect the camera module cable to USB host Type-A connector on baseboard(J27)

Connect the KitProg3 USB connector (J8) to your PC using the Type-C to Type-C USB cable

Ensure that the power LED (D1, yellow) on the base board is ON

Ensure that the power LED (D3, yellow) on the System on Module (SOM) board is ON

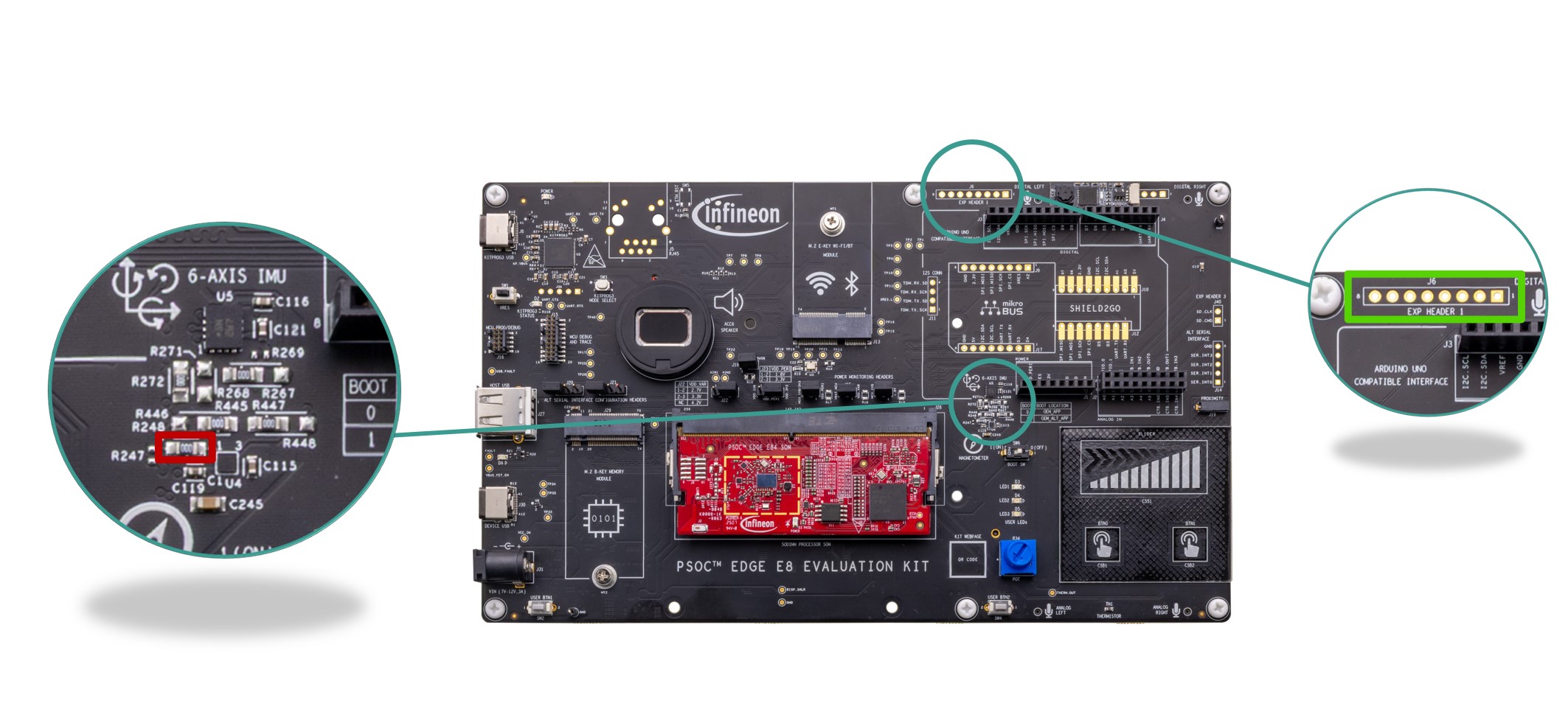

Figure 11.

Boot switch and jumper configuration

Run the pre-programmed code examples

Observe the splash screen boot-up on the 4.3 inch display

A carousal menu appears listing the demo applications pre-programmed into the kit

Select the application to be demonstrated

Follow the instructions (if any) presented by the demo app

Press the

Home

button to get back to main menu

Press the XRES button (SW1) to reboot the device to splash screen (if required)

Visit the

PSOC™ Edge E84 Evaluation Kit

webpage for latest software and other kit documentation

Figure 12.

PSOC™ Edge E84 Evaluation Kit

OOB Demo

Creating a project and program/debug using ModusToolbox™ software

The PSOC™ Edge E84 evaluation kit can be programmed and debugged using the on-board KitProg3. KitProg3 is an on-board programmer/debugger with USB-UART, USB-I2C Bridge functionality. KitProg3 supports CMSIS-DAP only and does not support mass storage. A PSOC™ 5LP device is used to implement the KitProg3 functionality. For more details on the KitProg3 functionality, see the

KitProg3 user guide

.

This following steps briefly introduces project creation, programming, and debugging using ModusToolbox™ software. For detailed instructions, see

Help >

Eclipse for ModusToolbox™

Documentation > User Guide

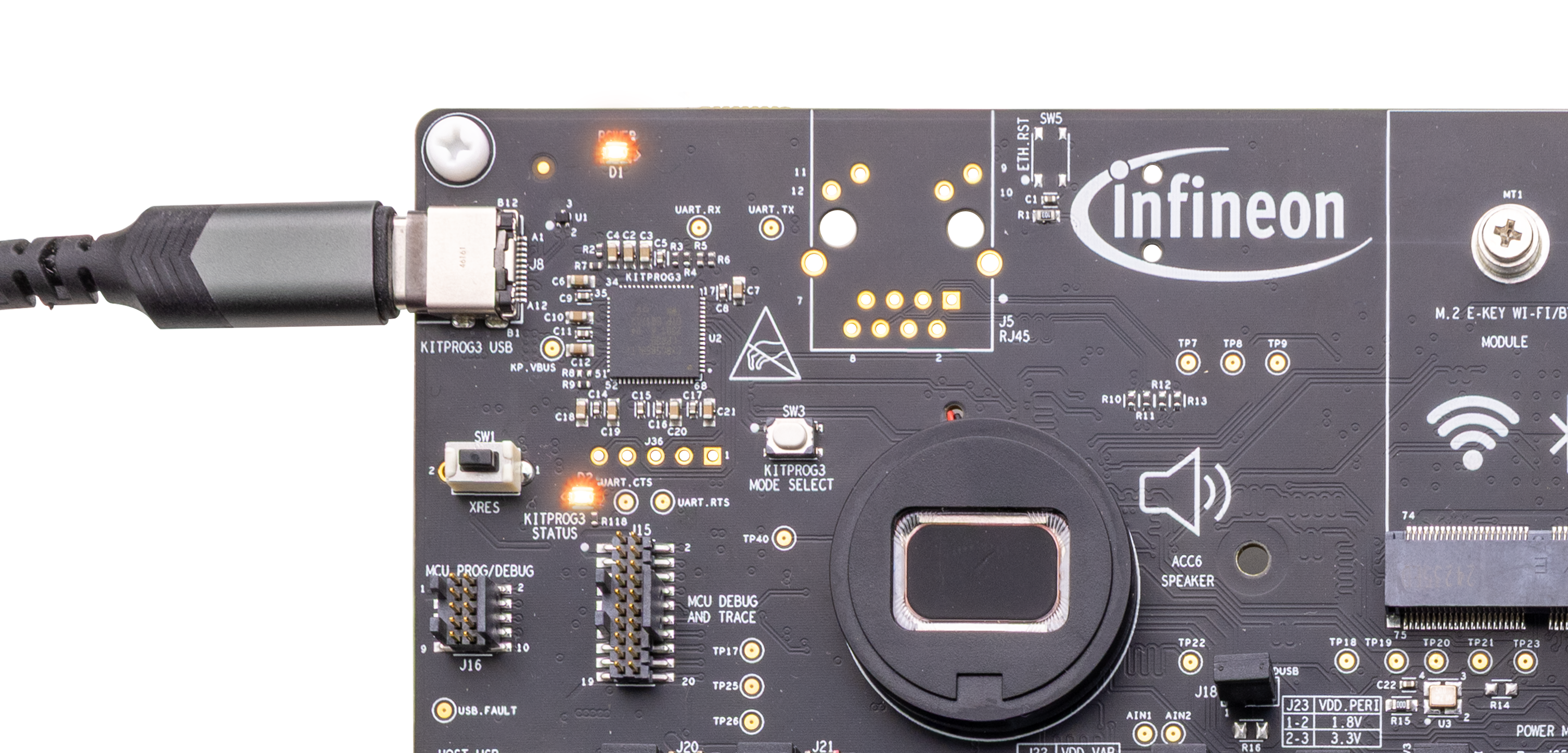

Connect the board to the PC using the provided USB cable through the KitProg3 USB connector, as shown in

Figure 13

. It enumerates as a USB Composite Device if you are connecting it to your PC for the first time

KitProg3 on this kit supports CMSIS-DAP Bulk mode (default) and CMSIS-DAP Bulk with two UARTs. The status LED (amber) is always ON in the CMSIS-DAP Bulk mode. If you do not see the desired LED status, see the

KitProg3 user guide

for details on the KitProg3 status and troubleshooting instructions

Note:

The programming can be done in either of the KitProg3 programming modes but it is recommended to program the kit in CMSIS-DAP Bulk mode.

Figure 13.

Connect USB cable to USB connector on the board

In the Eclipse IDE for ModusToolbox™ software, import the desired code example (application) into a new workspace

Click on

New Application

from

Quick Panel

Figure 14.

Create new application

Select the BSP -

KIT_PSE84_EVAL

in the “Choose Board Support Package” window and click

Next

Figure 15.

Creating a new application: Choose Board Support Package

Select the application from

Select Application

window and click

Create

Figure 16.

Creating a new application: Select Application

To build and program a PSOC™ E84 MCU application, in the Project Creator, select ui

project. In the Quick Panel, scroll to the Launches section and click the

<App_Name> Program (KitProg3_MiniProg4)

configuration as shown in

Figure 17

Figure 17.

Programming in ModusToolbox™ software

ModusToolbox™ software has an integrated debugger. To debug a PSOC™ E84 MCU application, in the Project Creator, select

project. In the Quick Panel, scroll to

Launches

section and click the

<App_Name> Debug (KitProg3_MiniProg4)

configuration as shown in

Figure 18

. For more details, see the “Program and debug” section in the

Eclipse IDE for ModusToolbox™ user guide

Figure 18.

Debugging in ModusToolbox™ software

Hardware

Schematics

Hardware functional description

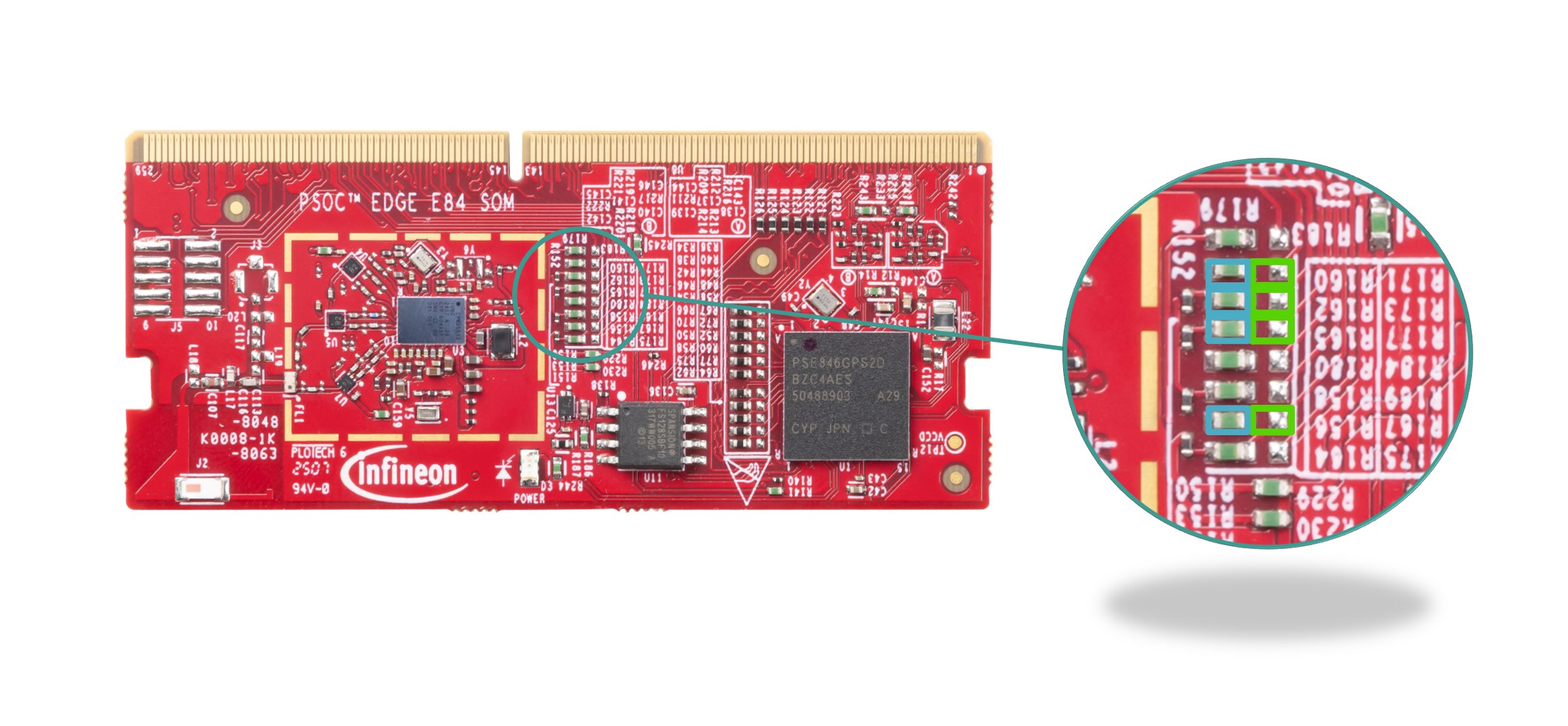

MOD_PSE84_SOM

PSOC™ Edge E84 MCU

PSOC™ Edge E84 MCU has the following features:

High-performance compute, graphics, audio, DSP, and machine learning (ML) blocks

Low-power CPU block for security, control, and communication

Low-power operation: Multiple power modes; DC-DC buck converter; dynamic voltage and frequency management

Optimizable power: independent voltage domains; selectable SRAM retention

Communications and connectivity: USB, SD host, Serial Memory Interface (SMIF), Ethernet, CAN FD, I3C, I2C, UART, SPI

Always-on power domain: Autonomous Analog with ADC, DAC, opamps, comparators, Acoustic Activity Detection (AAD)

Programmable GPIO pins: drive modes, strengths, and slew rates; over-voltage tolerant (OVT) pins for I2C compliance. Some ports have a smart I/O programmable logic array

Potential applications are:

Smart home appliance

Smart thermostat

Industrial HMI

This product line is a dual-CPU microcontroller with a neural net companion processor, DSP capability, high-performance memory expansion capability, low-power analog subsystem with high-performance analog-to-digital conversion and low-power comparators, IoT connectivity, communication channels, and programmable analog and digital blocks. It also has audio and graphics blocks.

In a multi-domain architecture, PSOC™ Edge E84 MCU supports the security, communications and control, and DSP. This enables the fine-grained power optimization and dynamic frequency and voltage scaling. The always‑on domain supports voice recognition, wake-on-touch, battery monitoring, and other sensing applications. These functions are provided at extremely low power.

Figure 19.

MCU block diagram

PSOC™ Edge E84 MCU power supply system

This product line operates with a single 1.8 V ±5% regulated supply, or from a 2.7 V to 4.8 V VBAT supply along with a 1.8 V 5% regulated supply.

The core logic can operate at different levels with a trade-off in performance and power. In addition with clock gating at peripheral and bus levels, this permits fine-grained optimization of energy usage. A buck regulator powers the core logic at three levels: 0.7 V, 0.8 V, and 0.9 V. The buck efficiency is ≥80% in the active power mode. The buck configuration is single in, single out (SISO).

System-on-Module (SoM) provides the following two modes of powering the MCU:

Power on with VBAT(3.3 V) by default

1.8 V regulated supply with rework

All MCU IOs can operate at 1.8 V logic level only. P16 and P17 can be operated at 1.8 V or 3.3 V by changing the jumper setting on the baseboard.

By default, USB IP is powered by the 3.3 V supply voltage that is connected via a jumper (for power measurement) on the baseboard.

Ferrite bead FB1-FB4 is included to reduce the switching noise between the digital and analog power supplies within the domain.

Figure 20.

PSOC™ Edge E84 power supply system (1)

Figure 21.

PSOC™ Edge E84 power supply system (2)

PSOC™ Edge E84 MCU I/Os

PSOC™ Edge E84 SOM will bring out all the High speed and Low speed IOs to the baseboard through 260-pin Edge connector, some are directly connected to on-board peripherals and some are routed and exposed on header.

ECO , WCO and EXT clock and SWD pins are dedicated in the board. Few IOs are multiplexed in the SOM for the alternate functionality. See

PSOC™ Edge E84 kit rework

section for using alternate functions.

Figure 22.

MCU GPIO

HSIO (SMIF0, SMIF1, MIPI DSI, and USB) pins along with the clock and SWD are dedicated from the MCU and connected directly to the peripherals.

Figure 23.

MCU HSIO

Clock architecture for PSOC™ Edge E84

PSOC™ Edge E84 SOM board includes 32.768 KHz WCO(

Y1

) and 17.2032 MHz ECO ( Y2 ) for the PSOC™ Edge E84 MCU device and 24 MHz ( Y4 ) oscillator input as external clock input for the USB functionality..

There will be a dedicated 24 MHz clock input for enabling the USB interface as host and device from the MCU. Dedicated External Crystal Oscillator 17.2032 MHz for the internal PLL block and WCO 32.768 KHz for the RTC block.

Figure 24.

PSOC™ Edge E84 clock sources

PSOC™ Edge E84 programming header

PSOC™Edge E84 MCU can be programmed alternatively through a 10-pin SWD ( J5 ) using Miniprog4.

By default, to program the PSOC™Edge E84 MCU, plug the SOM on the baseboard as J5 is not mounted on the SOM.

Figure 25.

MCU programming header

Memory subsystem

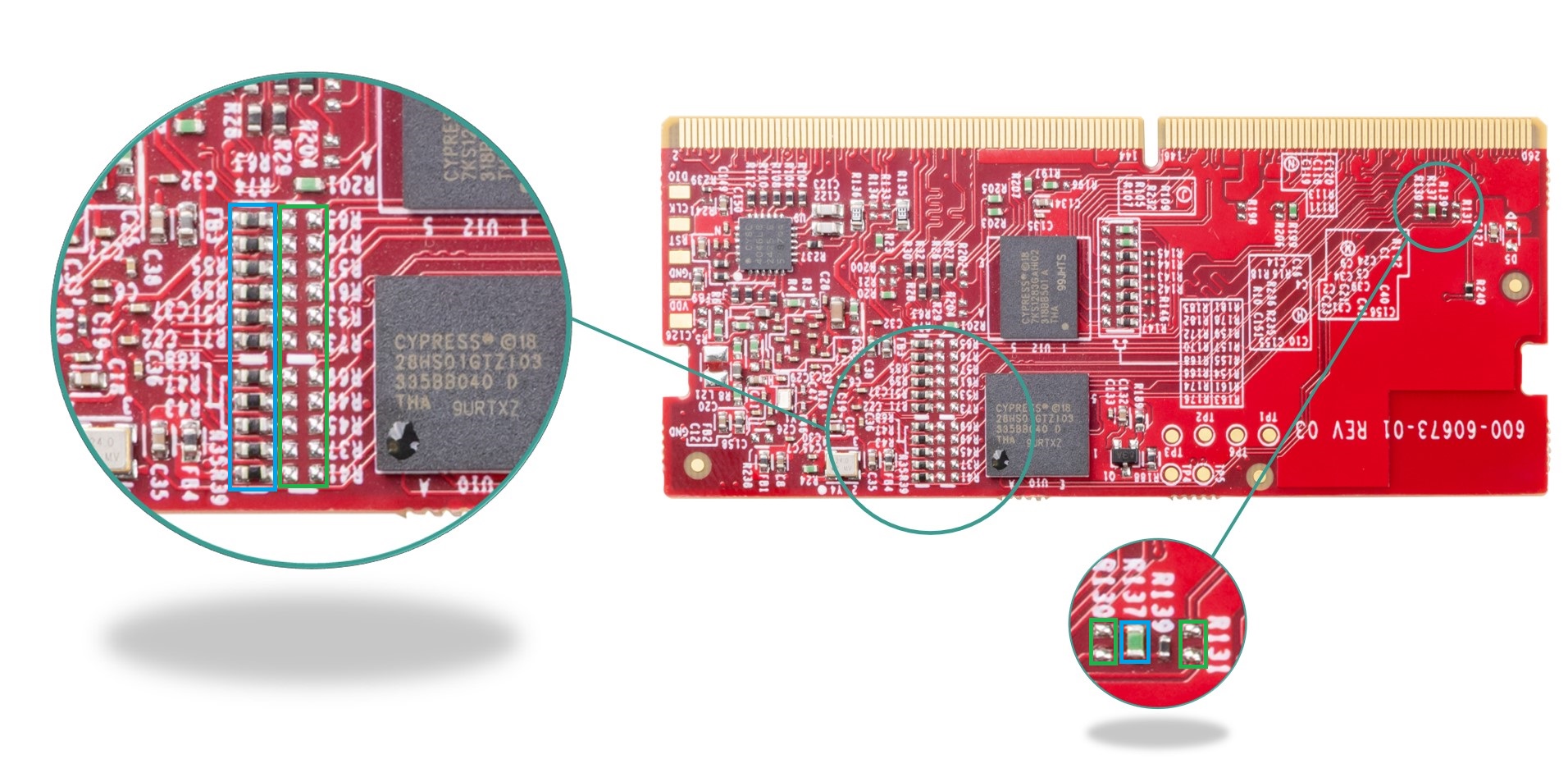

Quad-SPI flash

PSOC™ Edge E84 SOM board has an Infineon Quad SPI NOR flash memory (U11) of 128 Mb capacity (S25FS128SAGMFB100).

The NOR flash is connected to the Quad SPI interface of the PSOC™ Edge E84 MCU device. The NOR flash device supports 4-bit (Quad I/O) serial commands. By default, Smif0_Select1 is connected to this interface. IO lines are shared between the Octal and Quad flash in this board. In the Quad DDR mode, the device operates at 80 MBps with the 80 MHz clock. In the Quad SDR mode, it operates at 66 MBps with the 133 MHz clock.

Octal flash

PSOC™ Edge E84 SOM board has an Infineon SEMPER™ Octal flash memory (S28HS01GTGZBHI030) (U10) of 1 Gb capacity.

The NOR flash is connected to the Octal xSPI interface of the PSOC™ Edge E84 MCU device. The NOR flash device supports 8-bit (Octal I/O) serial commands. The device can operate up to 200 MBps in SDR mode and 400 MBps in DDR mode.

Figure 26.

Quad and Octal SPI flash

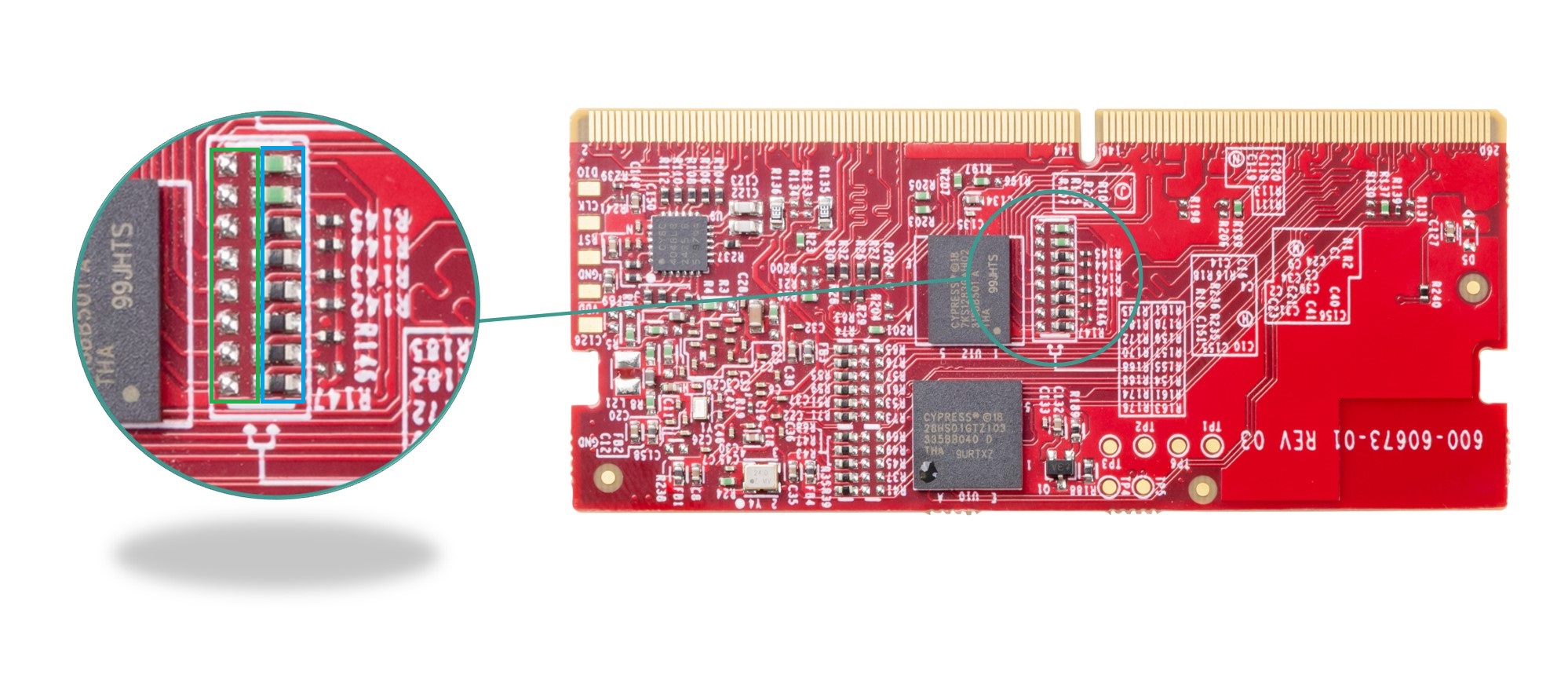

HYPERRAM™

PSOC™ Edge E84 SOM board has an Infineon HYPERRAM™ memory (S70KS1283GABHI020) (U12) of 128 Mb capacity.

The PSRAM is connected to the Octal xSPI interface of the PSOC™ Edge E84 MCU device. The PSRAM device supports 8-bit (Octal I/O) serial commands. The device can operate only in DDR mode with 400 MBps data rate.

Figure 27.

HYPERRAM™

AIROC™ CYW55513 Wi-Fi & Bluetooth® radio

AIROC™ CYW55513 Wi-Fi & Bluetooth® is an low-power, single chip device that support single-stream, tri-band, Wi-Fi 6/6E, IEEE 802.11ax compliant Wi-Fi MAC/baseband/radio, and Bluetooth®/Bluetooth® Low Energy 5.4.

PSOC™ Edge E84 device communicates to this device using a standard SDIO interface for WLAN and BT_UART for Bluetooth® operation along with the handshake signals. AIROC™ CYW55513 Wi-Fi & Bluetooth® radio supports the following:

BT_Reg_ON controls the regulator power of the Bluetooth® host

WL_Reg_ON controls the regulator power of the WLAN host

Bluetooth® host wake and WL host wake are connected to invoke the IC during the power down mode

Bluetooth® device wake and WL device wake to invoke the radio from host

Bluetooth® communication can happen with the 115200 maximum baud rate

WLAN can communicate over an SDIO interface at SDR50 or DDR50 speed

Radio PMU topology

AIROC™ CYW55513 powers on with an external VBAT supply that is 3.3 V and the IO supply voltage 1.8 V from the baseboard. All the additional power for RF switches, power amplifiers will be derived from the internal regulators.

Figure 28.

AIROC™ CYW55513 - power1

Figure 29.

AIROC™ CYW55513 - power 2

Power LED

LED D3 glows when the SOM board is powered and this will ensure that the radio and peripheral supplies are in nominal voltage.

Load switch for AIROC™ CYW55513 power sequence

U13 ensures that the AIROC™ CYW55513 IC will be powered once the VBAT_Radio supply comes first and then IO supply H1_1V8, which will satisfy the power sequence requirement of the IC.

Figure 30.

Load switch and Power LED

Radio subsystem

AIROC™ CYW55513 communicates with the host MCU through the SDIO and UART interface.

Figure 31.

Radio subsystem

Clock architecture for radio

PSOC™ Edge E84 SOM board includes 37.4 MHz ECO (

Y3

), 32.768 KHz WCO (

Y5

) for the AIROC™ CYW55513 device.

There is an option to use the LPO (

Y6

) oscillator input for the 32.768 KHz that is DNI by default.

Figure 32.

AIROC™ CYW55513 clock sources

RF matching network

PSOC™ Edge E84 SOM board includes a Pi-type matching network for the 2 GHz and 5 GHz paths of WLAN and Bluetooth®, which is connected before and after the RF switches to control the impedance to 50 Ω.

Figure 33.

RF matching network

RF front end

PSOC™ Edge E84 SOM board includes RF switches, diplexer, onboard chip antenna (default) and option to test with external antenna using UFL connectors.

Figure 34.

RF front end

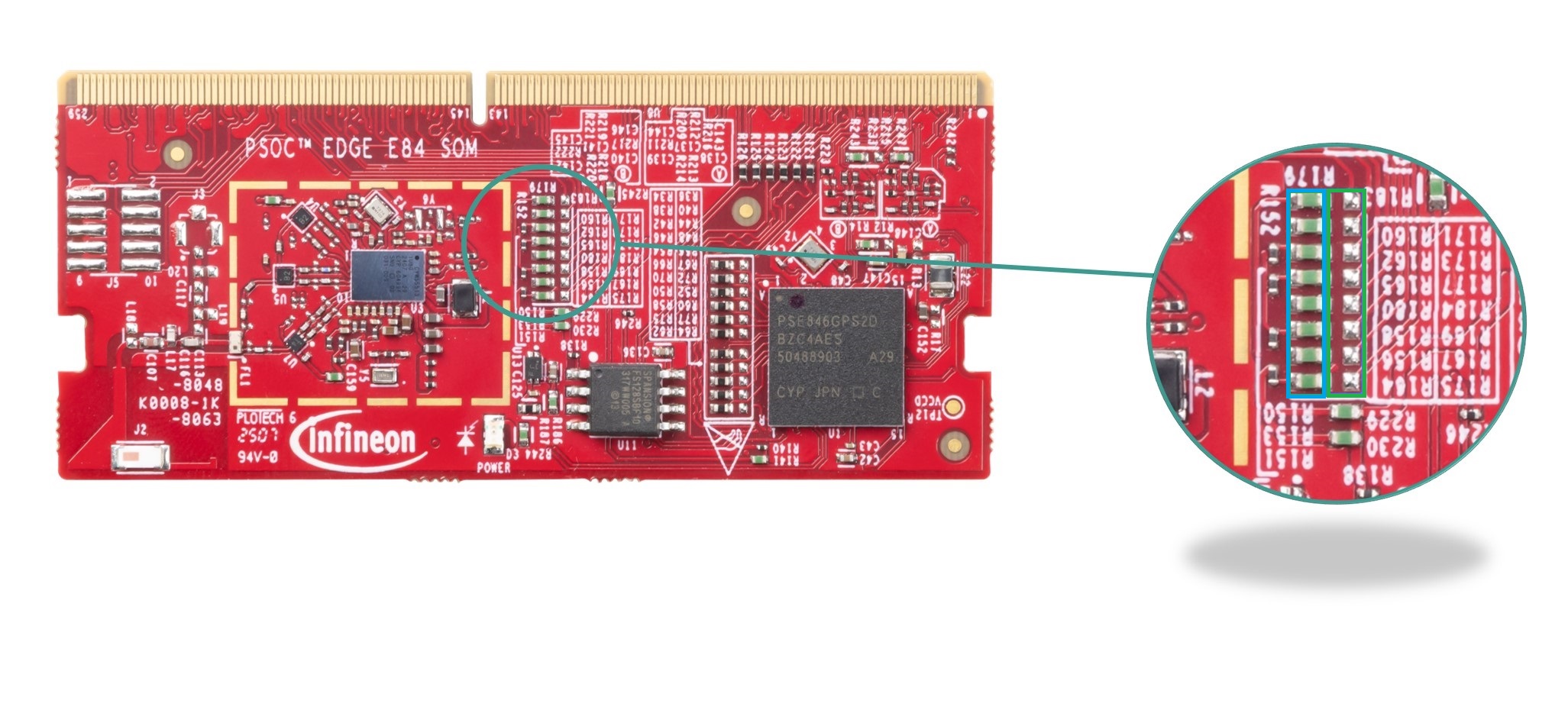

CAPSENSE™ coprocessor

The PSOC™ Edge E84 SOM board has onboard PSOC™ 4000T ( U9 ), which is used as a CAPSENSE™ coprocessor. This senses the data from the slider, buttons and the proximity sensor in mutual cap mode and will communicate to the host via an I2C interface with the default slave ID "0x0C".

You can program the CAPSENSE™ IC using the bootloader code, which will dump the program from the host MCU to CAPSENSE™ using I2C.

Figure 35.

PSOC™ 4000T device

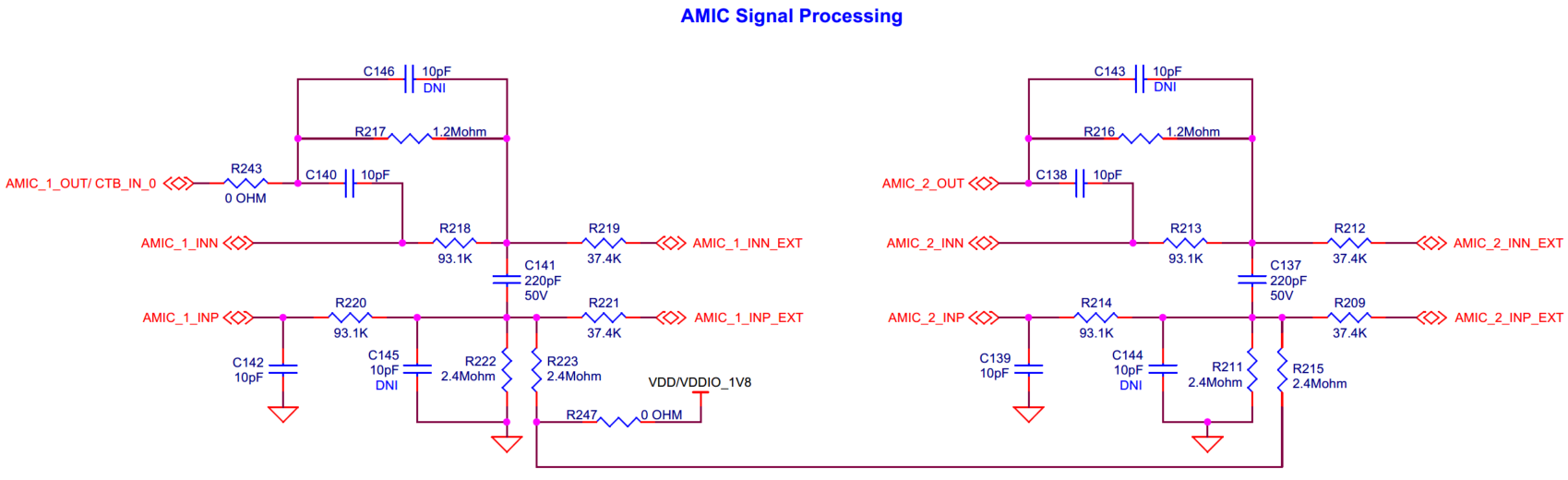

AMIC signal processing circuit

Circuit is used to tune the frequency response and the signal amplitude of AMIC, which is present on the baseboard.

Figure 36.

RC compensation circuit

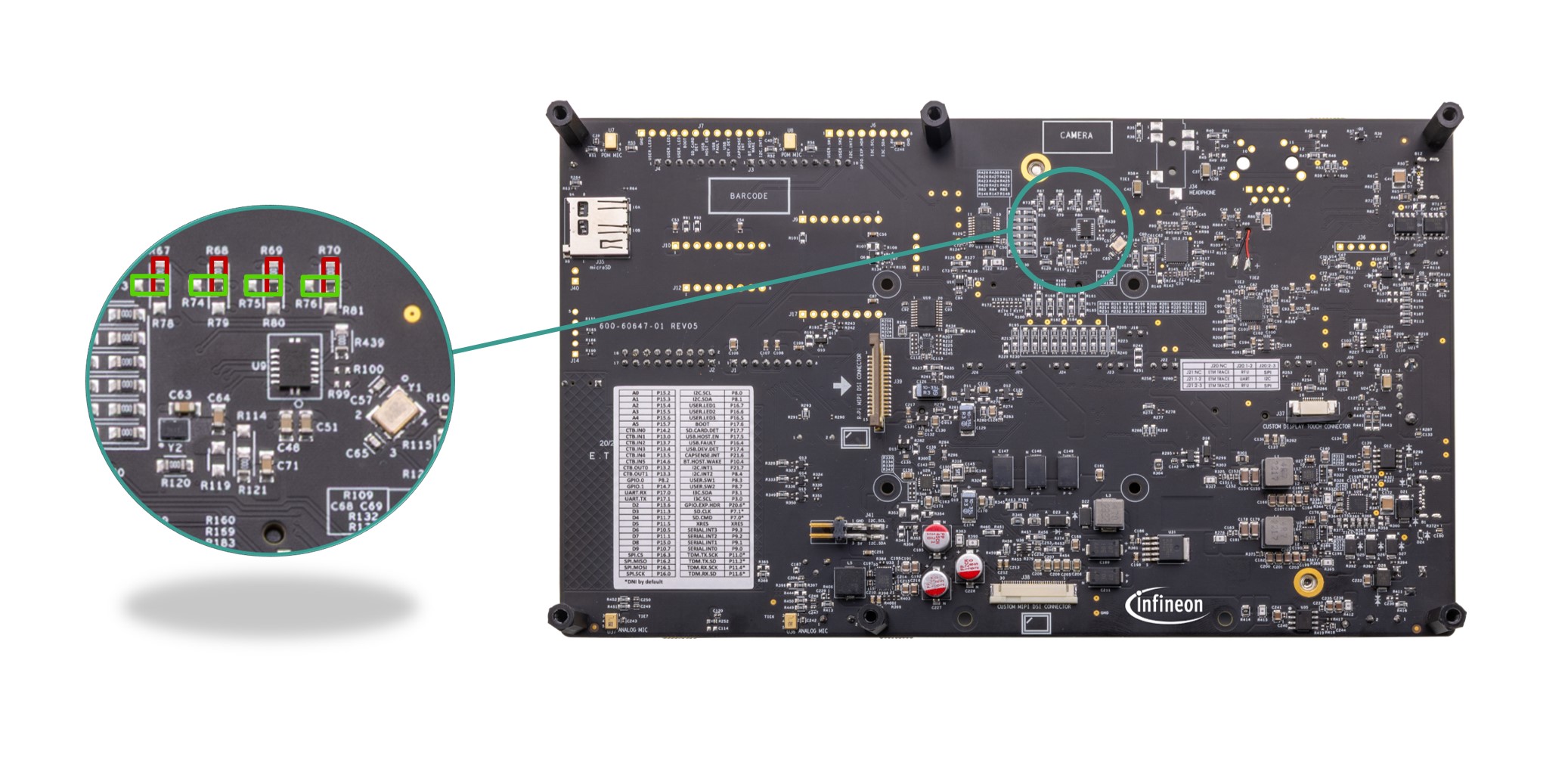

PSOC™ Edge E8 Base Board

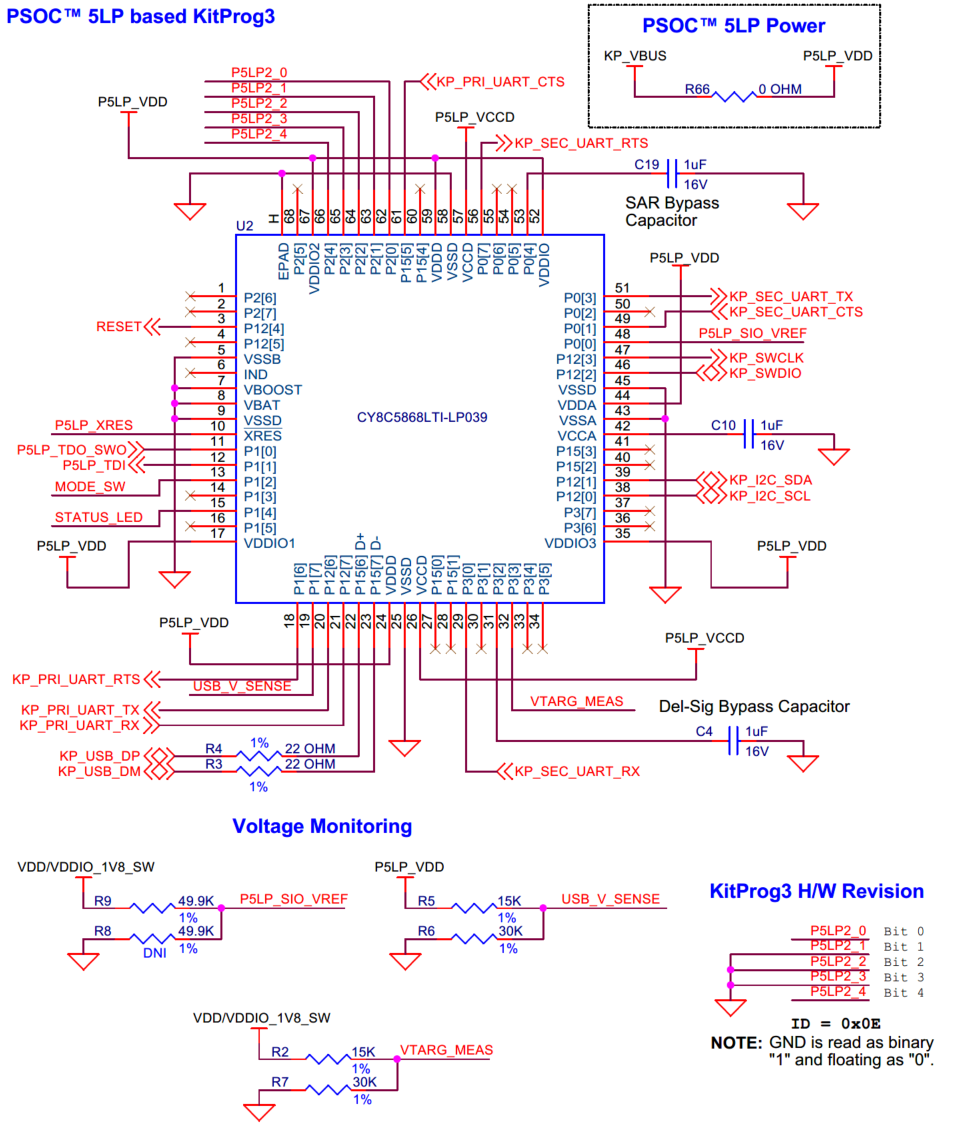

PSOC™ 5LP as onboard programmer/debugger

PSOC™ 5LP-based KitProg3

PSOC™ 5LP-based KitProg3 to program and debug the PSOC™ Edge E84 MCU.

An onboard PSOC™ 5LP (CY8C5868LTI-LP039,

U2

) device is used as KitProg3 to program and debug the PSOC™ Edge E84 MCU. The PSOC™ 5LP device connects to the USB port of a PC through a USB connector and to the SWD/JTAG and other communication interfaces of the PSOC™ Edge E84 MCU. KitProg3 uses 5 pins for hardware ID definition. These I/Os can be either connected to the ground (active state) or left floating. The KitProg3 firmware reads the state of these pins with software inversion and get the specific hardware ID value which describes the unique Kit features set. Also, it features voltage monitor pins which sense the USB bus voltage, target device supply and Smart IO reference voltage which For more information, see the

PSOC™ 5LP

webpage and

Kitprog3 User Guide

Figure 37.

Schematic of PSOC™ 5LP-based KitProg3

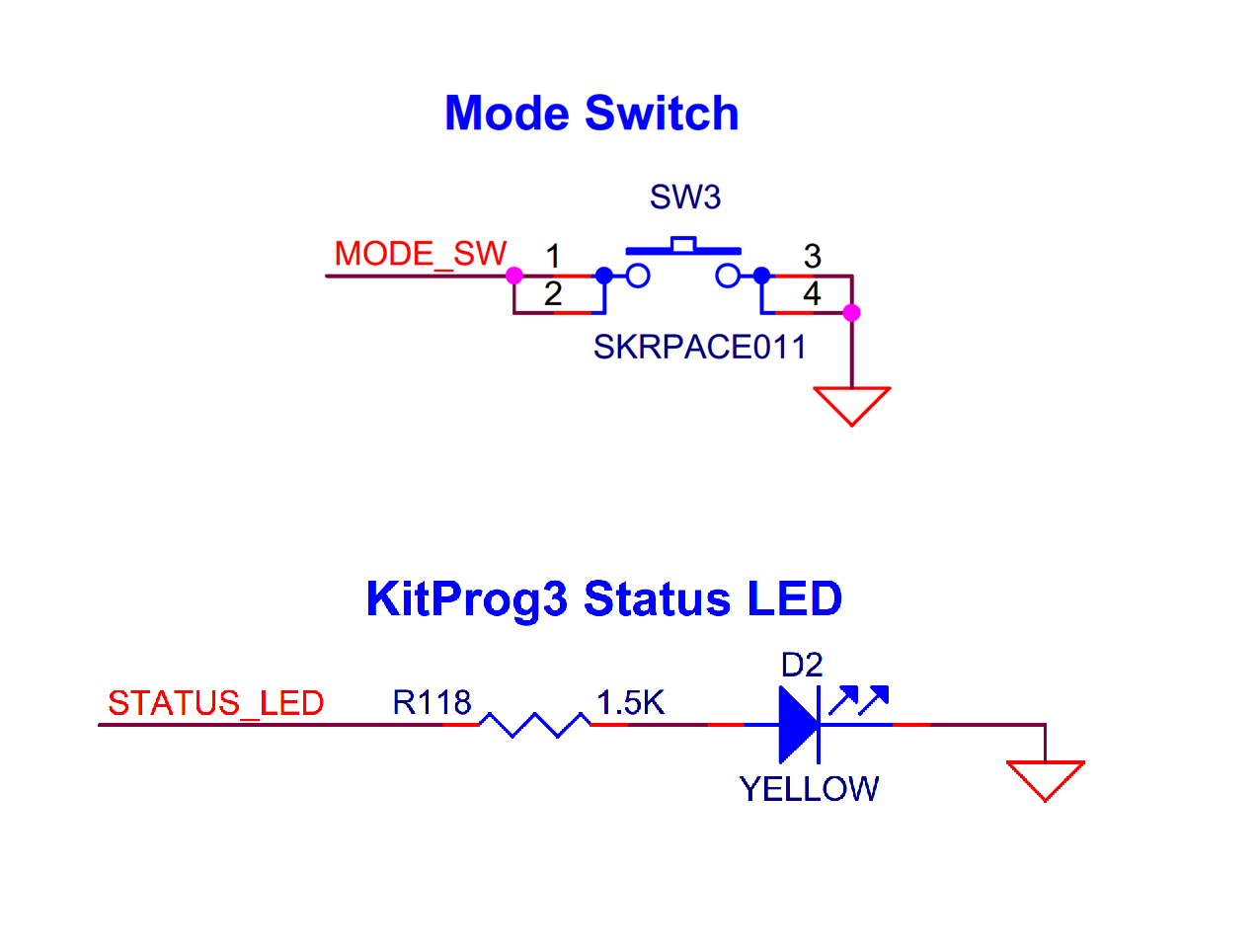

KitProg3 programming mode selection button and status LED

There is a mode selection button (

SW3

) connected to the PSOC™ 5LP device for programming mode selection. This button can be used to switch between modes (see the

Kitprog3 user guide

for details). The button works in active LOW configuration and shorted to GND when pressed.

PSOC™ 5LP has a status LED (

D2,

yellow) which indicates the programming status. See

Table 5

for a summary of the status LED states.

KitProg3 programming modes | Status LED (D2) |

|---|---|

CMSIS-DAP/Bulk mode (default) | ON |

CMSIS-DAP/HID mode | RAMPING at 1 Hz |

Figure 38.

Schematic of KitProg3 mode switch and status LED

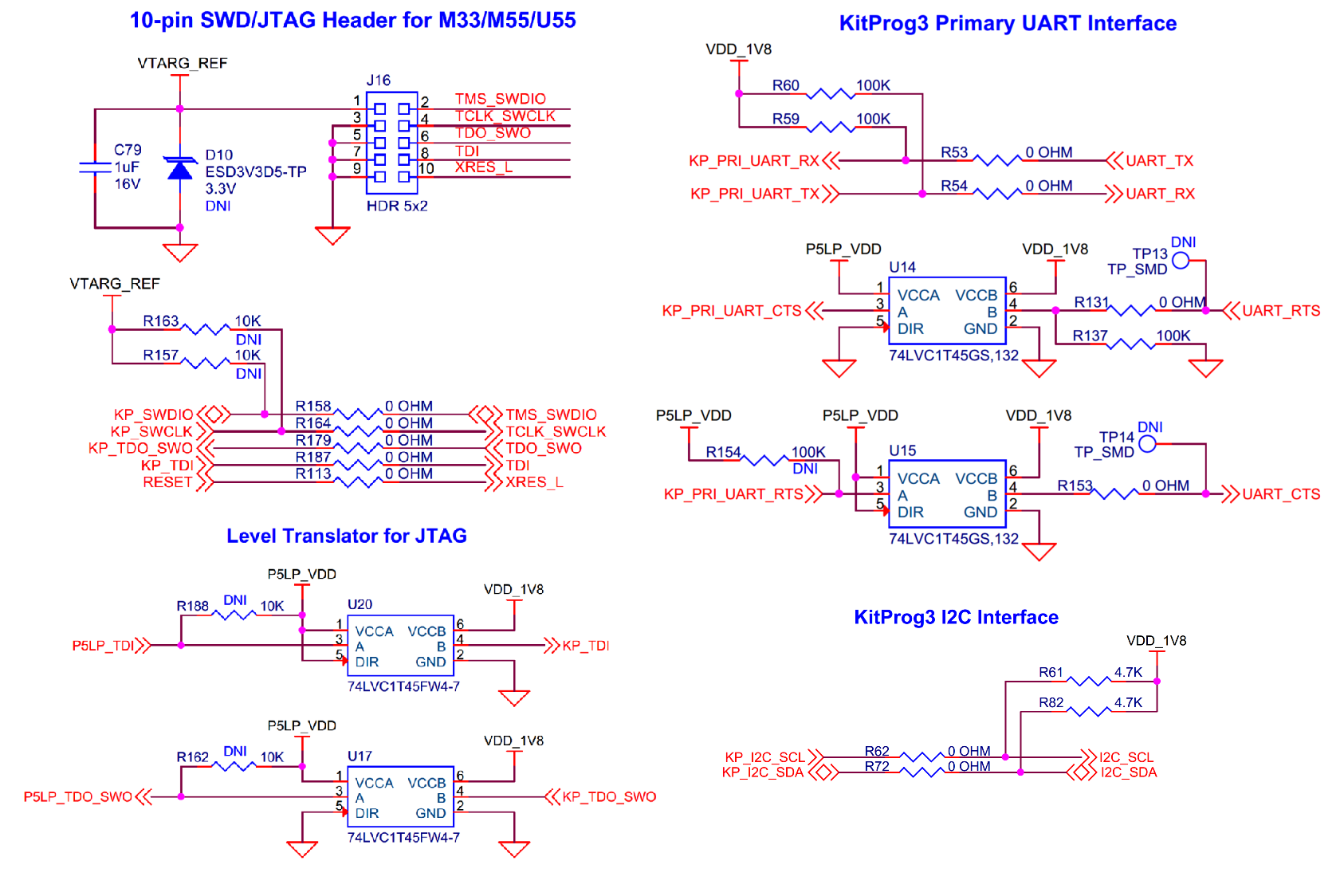

Serial interconnection between PSOC™ 5LP and PSOC™ Edge E84

In addition of use as an on board programmer/debugger using SWD/JTAG interface, the PSOC™ 5LP device also functions as an interface for the USB-UART and USB-I2C bridges, as shown in

Figure 39

. The USB-Serial pins of the PSOC™ 5LP device are hard-wired to the I2C/UART pins of the PSOC™ Edge E84 MCU. The Primary UART interface supports hardware flow control. The I2C pins are also available on the Arduino compatible I/O header, mikroBUS Click header and IFX Shield2Go header; therefore, the PSOC™ 5LP device can be used to control Arduino, mikroBUS Click and Infineon's Shield2Go shields with an I2C interface.

PSOC™ 5LP signal | PSOC™ Edge E84 I/O (signal) | Logic Level |

|---|---|---|

KP_SWCLK | P6[3] (TCLK_SWCLK) | 1.8 V |

KP_SDWIO | P6[2] (TMS_SWDIO) | 1.8 V |

KP_TDO_SWO | P6[0] (TDO_SWO) | 5 V (P5LP), 1.8 V (PSOC™ Edge E84) |

KP_TDI | P6[1] (TDI) | 5 V (P5LP), 1.8 V (PSOC™ Edge E84) |

RESET | XRES (XRES_L) | 1.8 V |

KP_I2C_SCL | P8[0] (I2C_SCL) | 1.8 V |

KP_I2C_SDA | P8[1] (I2C_SDA) | 1.8 V |

KP_PRI_UART_TX | P6[5] (UART_RX) | 1.8 V |

KP_PRI_UART_RX | P6[7] (UART_TX) | 1.8 V |

KP_PRI_UART_RTS | P6[4] (UART_CTS) | 5 V (P5LP), 1.8 V (PSOC™ Edge E84) |

KP_PRI_UART_CTS | P6[6] (UART_RTS) | 5 V (P5LP), 1.8 V (PSOC™ Edge E84) |

Figure 39.

Schematic of Serial Interconnection between PSOC™ 5LP and PSOC™ Edge E84

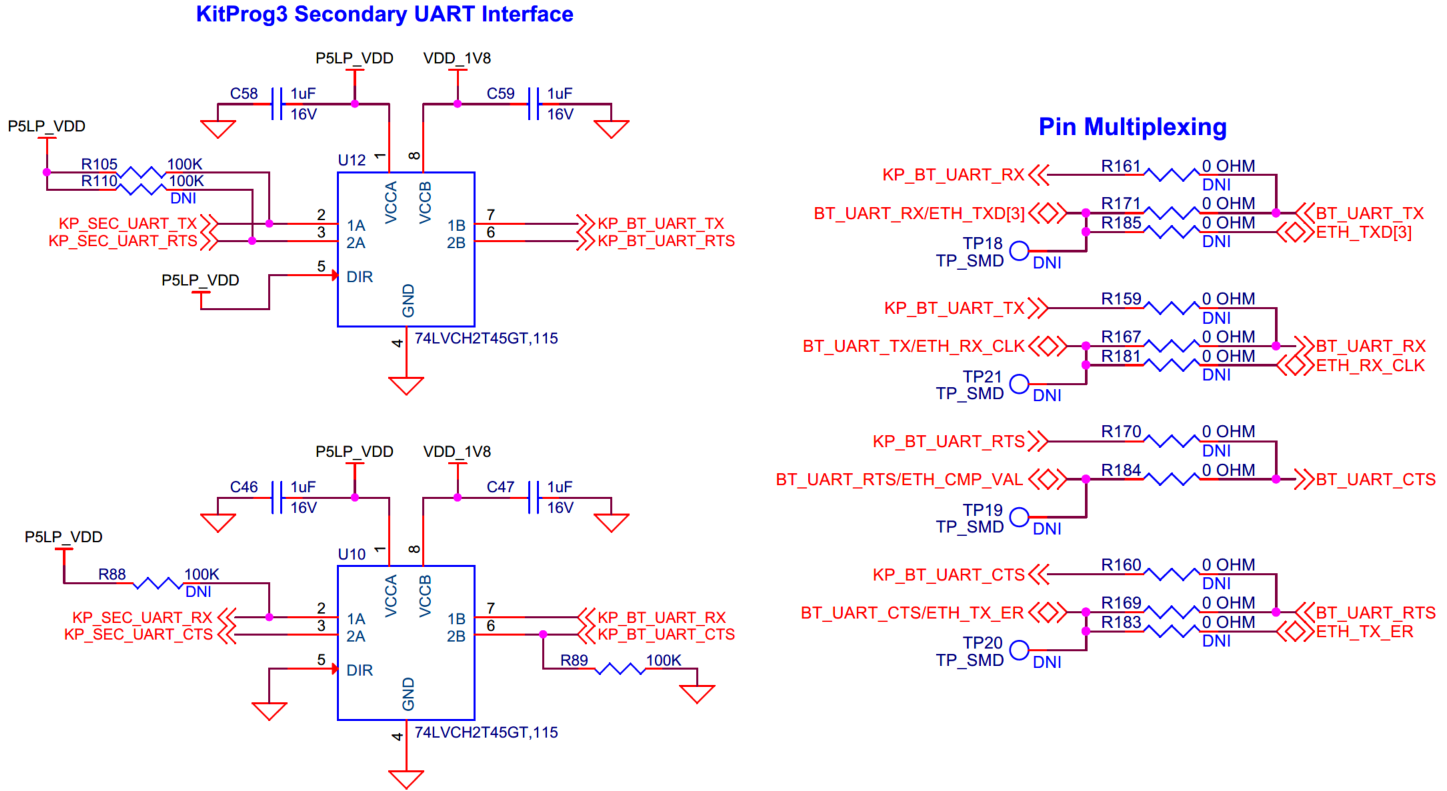

Serial interconnection between PSOC™ 5LP and radio interface

Serial interconnection between PSOC™ 5LP and onboard AIROC™ CYW55513/M.2 radio interface.

The PSOC™ 5LP device also has a secondary UART interface that can be connected to BT_UART of the on board AIROC™CYW55513 or the M.2 Radio interface connector (

J13

). Note that, it is connected to the AIROC™ CYW55513 device on SOM by default. To change it to M.2 radio, see the section

Rework for M.2 external radio interface

. The secondary UART interface supports hardware flow control.

Figure 40.

Schematic of serial interconnection between PSOC™ 5LP and radio interface

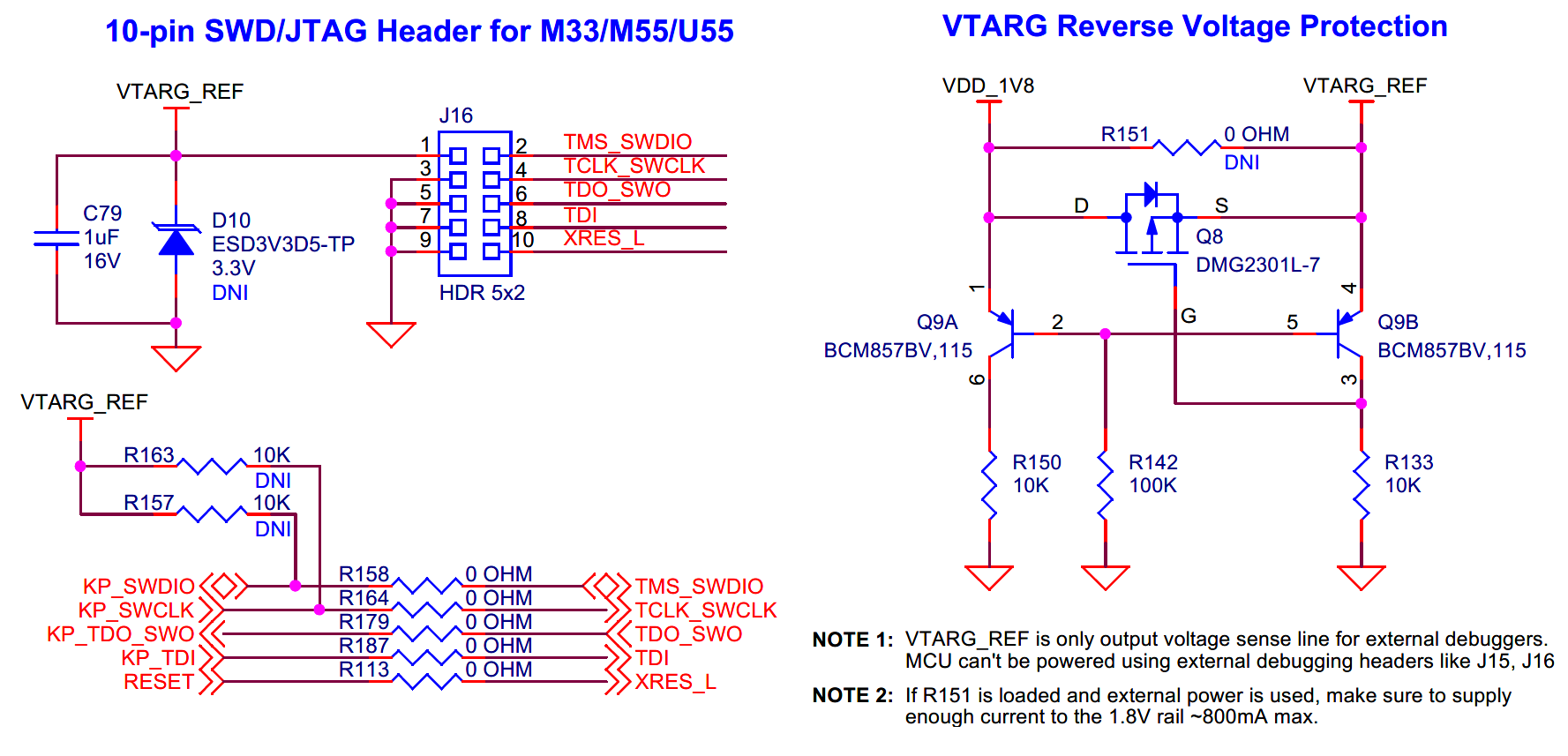

PSOC™ Edge E84 MCU external program/debug headers

10-pin SWD/JTAG header

10-pin SWD/JTAG interface for programming or debugging PSOC™ Edge E84 MCU.

PSOC™ Edge E84 MCU can be programmed/debugged alternatively through a 10-pin SWD/JTAG header (

J16

) using a MiniProg4 programmer or any third-party programmer.

Also, there is a reverse voltage protection circuit provided on the VTARG_REF power rail which means the PSOC™ Edge E84 or any other on board peripheral can not be powered from the 10-pin SWD/JTAG header (

J16

) or 20-pin ETM/JTAG header (

J15

). This is to protect the external programmer from overloading, making sure that the kit doesn’t draw any current from the external programmer through

J16

or

J15

.

Do note that the JTAG interface will not work by default through

J16

. See section

Rework for JTAG interface using external programmer/debugger

to enable the JTAG support.

Signal name | PSOC™ Edge E84 I/O | Logic level |

|---|---|---|

TCLK_SWCLK | P6[3] | 1.8 V |

TMS_SWDIO | P6[2] | 1.8 V |

TDO_SWO | P6[0] | 1.8 V |

TDI | P6[1] | 1.8 V |

XRES_L | XRES | 1.8 V |

Figure 41.

Schematic of 10-pin SWD/JTAG program/debug header

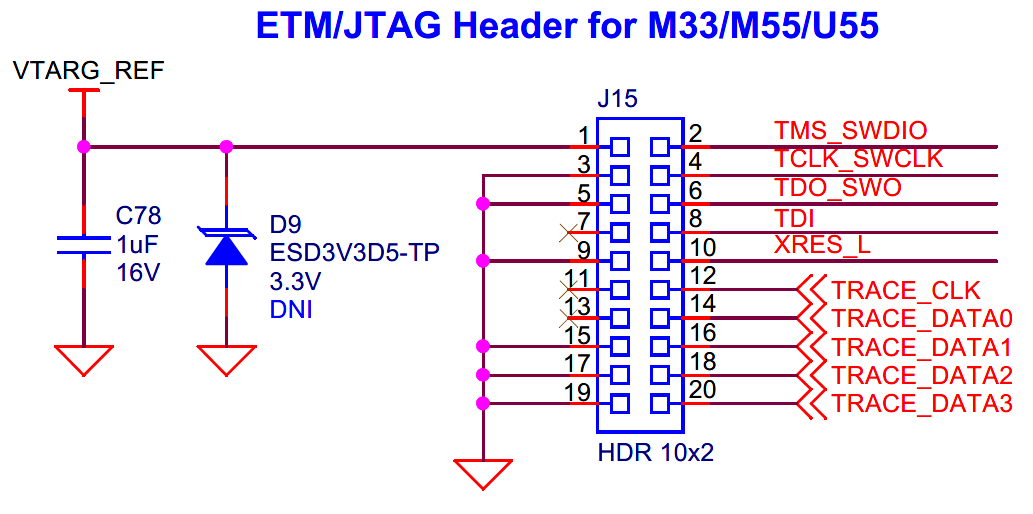

20-pin ETM/JTAG header

20-pin ETM/JTAG interface for programming or debugging PSOC™ Edge E84 MCU.

PSOC™ Edge E84 MCU can also be programmed/debugged through a 20-pin ETM TRACE or JTAG header (

J15

) using any third-party programmer.

Do note that the JTAG interface will not work by default through

J15

. See section

Rework for JTAG interface using external programmer/debugger

to enable the JTAG support. Also note that, pins TRACE_DATA2 and TRACE_DATA3 are available on J21 and J20 respectively for alternate serial interface configuration.

Signal name | PSOC™ Edge E84 I/O | Logic level |

|---|---|---|

TCLK_SWCLK | P6[3] | 1.8 V |

TMS_SWDIO | P6[2] | 1.8 V |

TDO_SWO | P6[0] | 1.8 V |

TDI | P6[1] | 1.8 V |

XRES_L | XRES | 1.8 V |

TRACE_CLK | P20[0] | 1.8 V |

TRACE_DATA0 | P20[4] | 1.8 V |

TRACE_DATA1 | P20[3] | 1.8 V |

TRACE_DATA2 | P20[2] | 1.8 V |

TRACE_DATA3 | P20[1] | 1.8 V |

Figure 42.

Schematic of 20-pin ETM/JTAG program/debug header

Power supply system

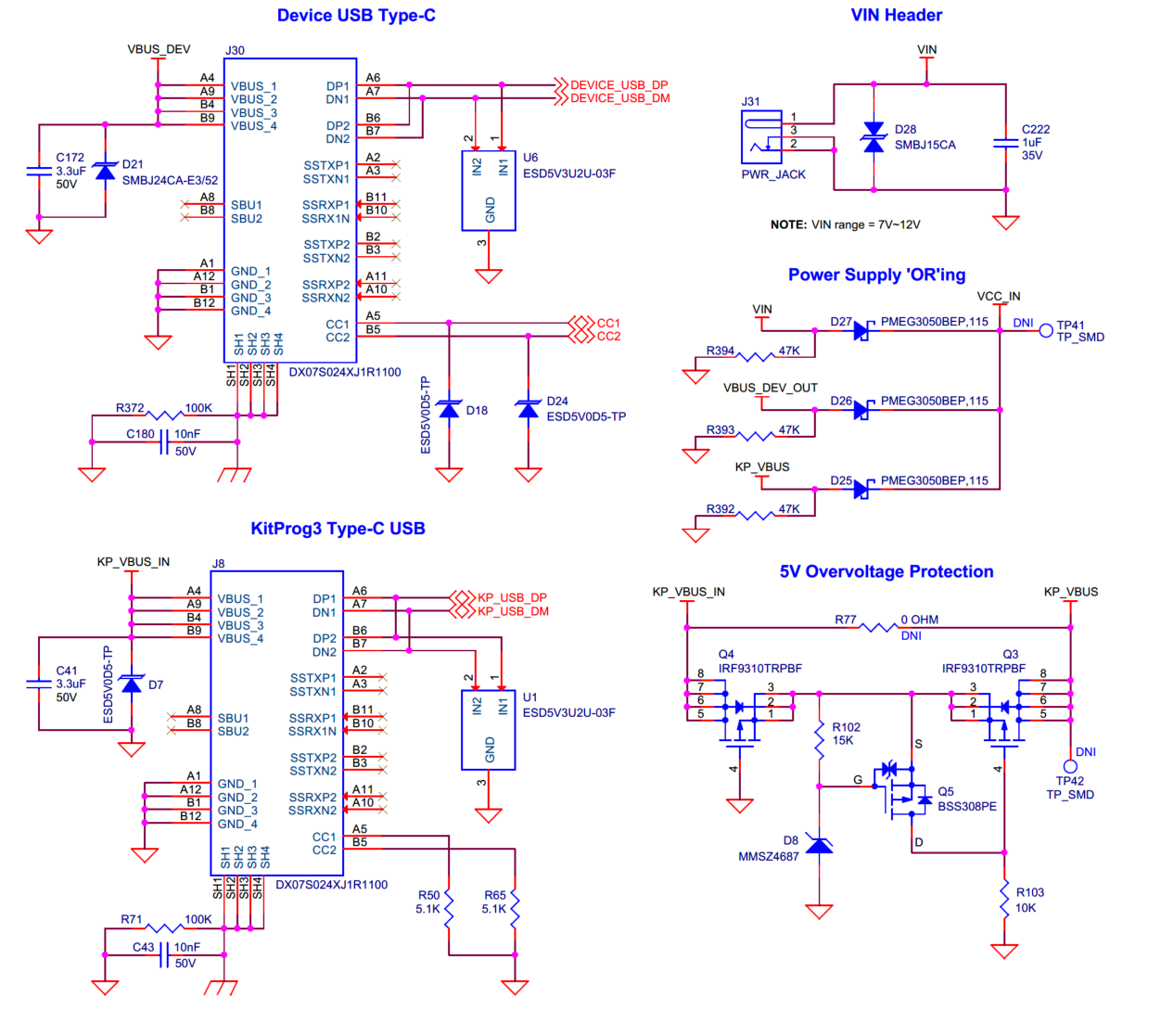

Power inputs and over-voltage protection

Power supply options for the kit and over-voltage protection circuit.

The power supply system on this board is versatile, allowing the board to be supplied from any of the following sources:

5 V/3A from the on board KitProg3 Type-C USB connector ( J8 )

5 V-15 V/3A from the Device Type-C USB connector ( J30 )

7 V-12 V/3A power from VIN header ( J31 ) or 7 V-12 V from Arduino header ( J1.1 )

The power supply system is designed to provide 1.8 V (core and I/O), 3.3 V (I/O), 2.7 V-4.2 V (VBAT) operating voltages to the PSOC™ Edge E84 MCU and 5 V for the PSOC™ 5LP based KitProg3 operation. Apart from that, 1.8 V, 3.3 V, and 5 V rails are also used to power the different on board peripherals.

The KitProg3 Type-C USB connector ( J8 ) can provide 5 V/3A and the host must have the power rating capability of 5 V/3 A. The power rail KP_VBUS_IN is connected to a 5 V over voltage protection (OVP) circuit which protects the on board PSOC™ 5LP and other components from over voltage. This OVP circuit has a cut-off range from 5.25 V (min) to 6.5 V (max) based on the component tolerance. Therefore, the maximum recommended voltage through

J8

is 5.25 V. Note that PSOC™ 5LP will only get power when powered from J8 .

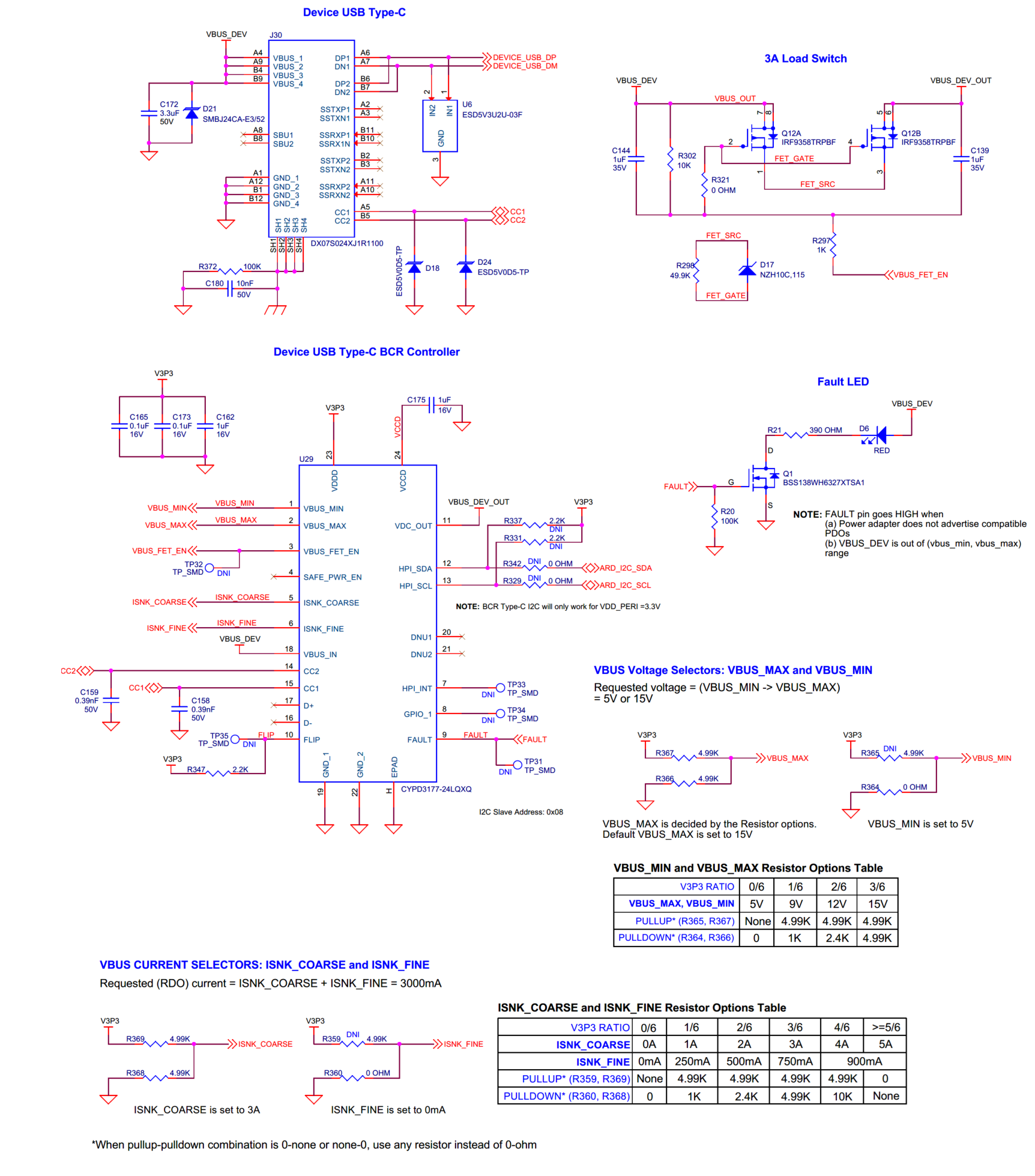

On the other hand, Device Type-C USB connector (

J30

) is configured to provide 5 V-15 V/3 A power using on board BCR controller (

U29

). Refer to section

Device Type-C USB EZ-PD™ BCR controller

for more details.

The supply rails KP_VBUS (5 V from header

J8

through OVP), VBUS_DEV_OUT (5 V-15 V from header

J30

through 3 A load switch) and VIN (7 V-12 V from header

J31

or

J1.1)

are combined into VCC_IN through ‘OR’ing diodes (

D25

-

D27

) as shown in the figure below.

Note that, it is recommended to power the board with minimum 9 V through Device Type-C USB connector (

J30

) or 7 V through VIN header (

J31

) when powering the MCU with VBAT = 4.2 V.

Also, it is highly recommended to power the board from the Device Type-C USB connector (

J30

) or VIN header (

J31

) with minimum 9 V/3 A when using any power-hungry peripherals like large display.

Figure 43.

Block diagram of power architecture

Figure 44.

Schematic of power inputs and over-voltage protection

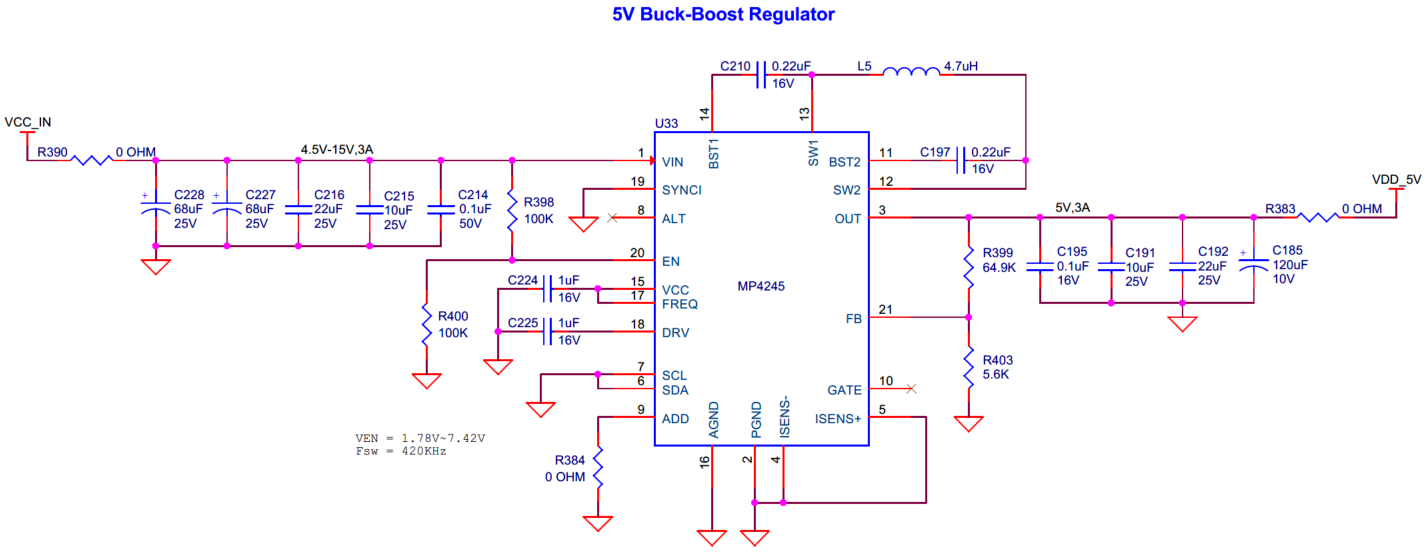

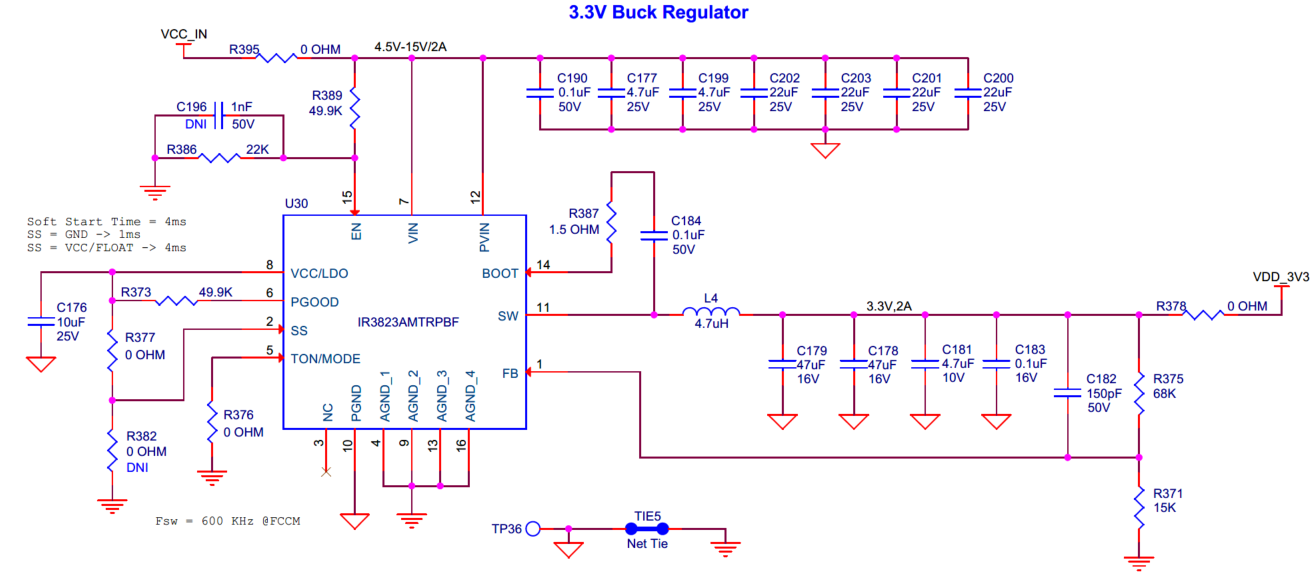

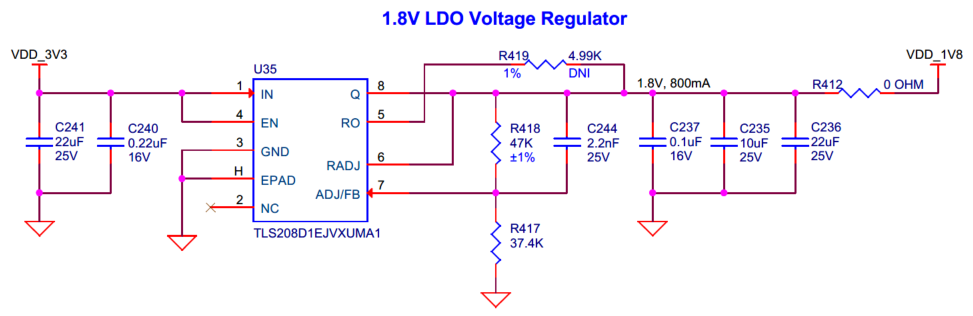

Voltage regulators

On board voltage regulators for power delivery.

There are four voltage regulators on the board:

1.8 V LDO ( U35 ): Powers the PSOC™ Edge E84 (core and I/O domains) and on-board peripherals

3.3 V Buck ( U30 ): Powers the PSOC™ Edge E84 (VDDUSB and I/O domain) and on-board peripherals

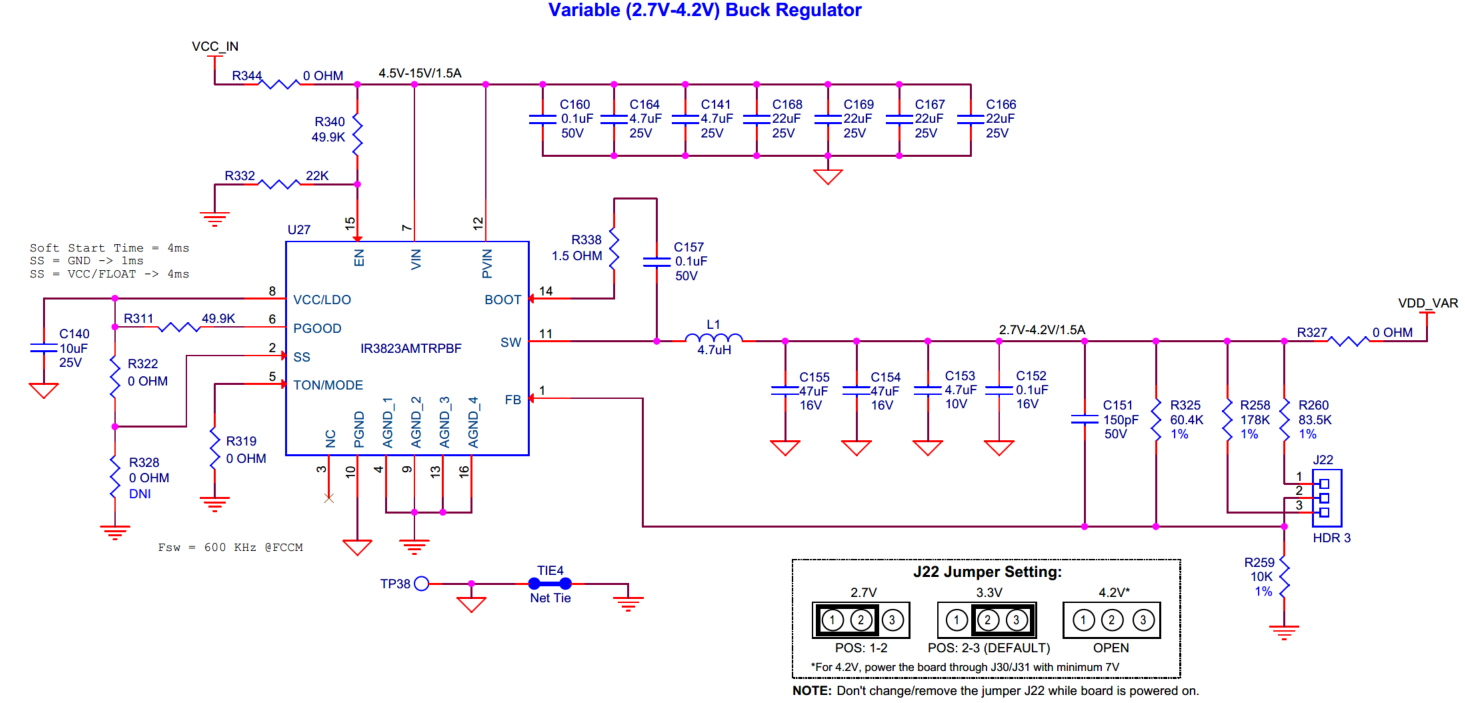

2.7 V-4.2 V Variable Buck ( U27 ): Powers the PSOC™ Edge E84 (VBAT domain) and M.2 Radio (VBAT domain, not powered by default)

5 V Buck-Boost ( U33 ): Powers the on-board peripherals

The 3.3 V Buck ( U30 ), 2.7 V-4.2 V Variable Buck ( U27 ) and 5 V Buck-Boost ( U33 ) regulators are powered from the VCC_IN rail and 1.8 V LDO ( U35 ) is powered from the output (VDD_3V3) of the 3.3 V Buck ( U30 ).

The 2.7 V-4.2 V Variable Buck regulator ( U27 ) can be configured for 3 different voltages by changing the J22 jumper location to showcase the Li-Po battery voltage range support as follows:

Jumper position | VDD_VAR |

|---|---|

1-2 | 2.7V |

2-3 (Default) | 3.3V |

OPEN | 4.2V 4 |

Note:

The header (

J22

) is not recommended to change or remove while the board is powered on.

Figure 45.

Schematic of voltage regulators

Device Type-C USB EZ-PD™ BCR controller

EZ-PD™ BCR controller for device Type-C USB power management.

The PSOC™ Edge E84 EVK features an on board CYPD3177-24LQXQ ( U29 ) EZ-PD™ Barrel Connector Replacement (BCR) controller based on the BCR product in Infineon’s USB Type-C and Power Delivery controllers. This is a highly integrated pre-programmed controller designed for power sink applications via the USB-C connector with few external components and no firmware development. The device communicates with the USB Type-C power adapter to negotiate for the proper voltage and current, as specified by on board resistors.

The controller has a red Fault LED ( D6 ) to indicate any voltage fault with the connection. If the power adapter cannot supply the power in VBUS_MIN (5 V) to VBUS_MAX (15 V) range, BCR device will turn the load switch OFF and will assert FAULT condition. Note that, the power adapter needs to have current support of 3 A for all the voltages ranging from 5 V-15 V. Else, it will trigger a fault condition.

The FAULT LED is turned ON in the following conditions:

The Device USB-C port ( J30 ) cannot provide the voltages or current requested by the system

Voltage on VBUS is 20% below the VBUS_MIN setting or 20% above the VBUS_MAX setting

Additionally, the device has an I2C slave interface which is connected to the PSOC™ Edge E84 host processor to control and monitor the EZ-PD™ BCR device. For more information, see the

EZ-PD™ BCR datasheet

.

Figure 46.

Schematic of device USB Type-C BCR controller

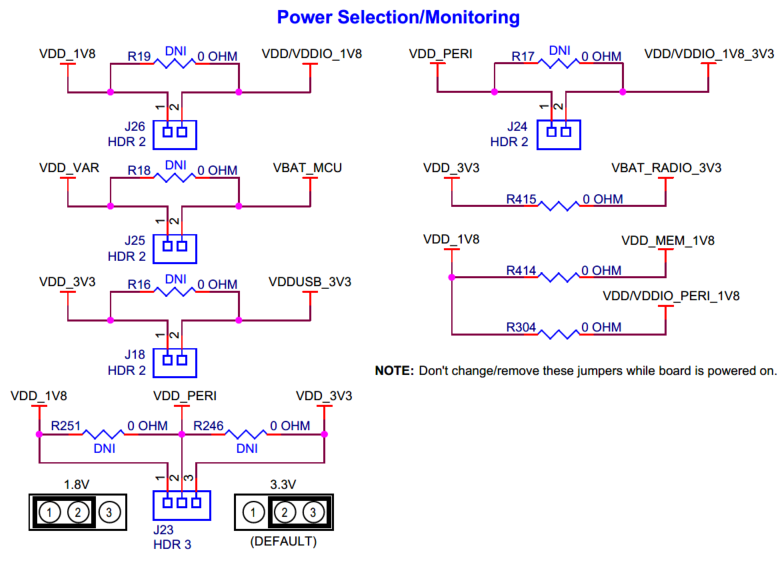

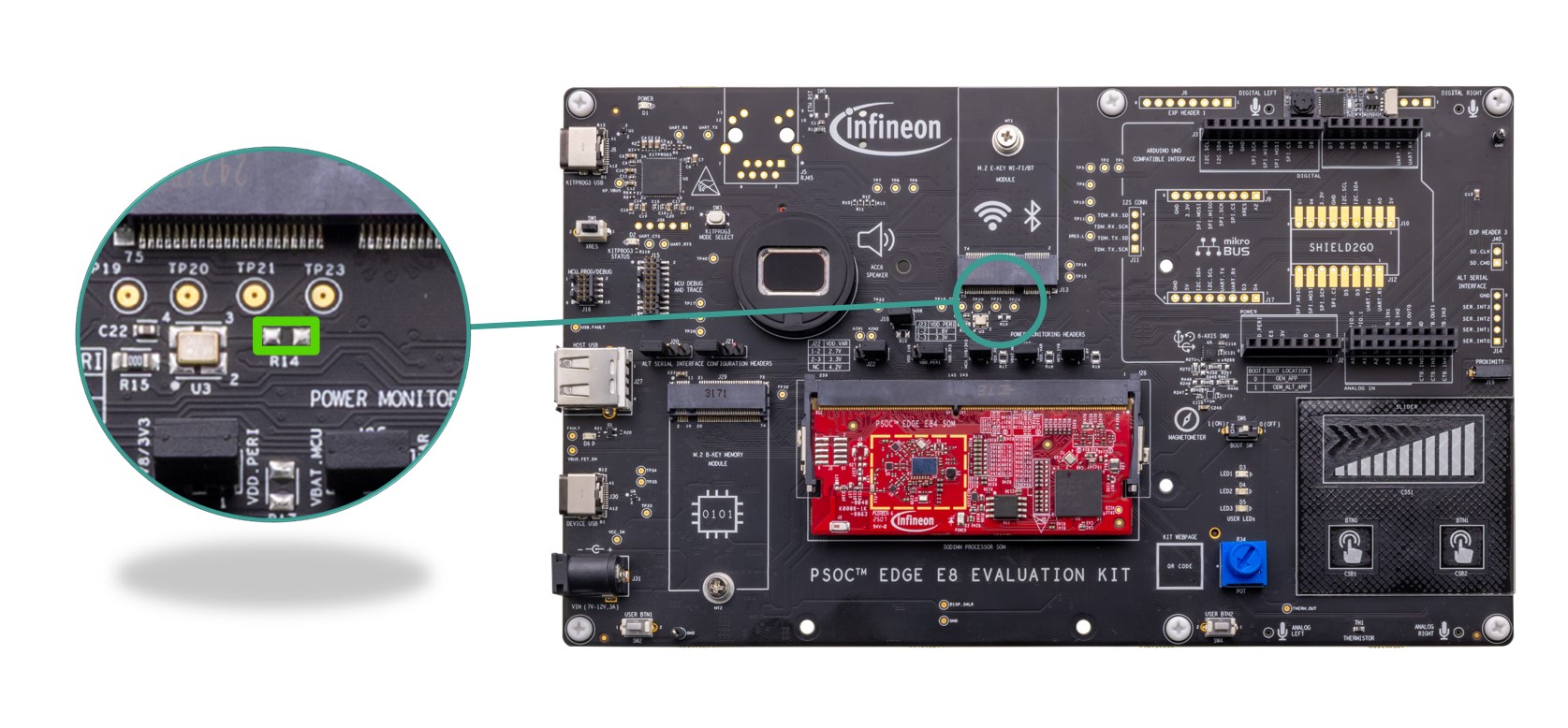

PSOC™ Edge E84 power selection and current monitoring headers

Power selection and current monitoring headers for PSOC™ Edge E84 MCU.

The PSOC™ Edge E84 MCU requires four different power domains:

VDD/VDDIO_1V8 ( J26.2 ): This is a 1.8 V power rail used to power the core and majority of I/O domains of the PSOC™ Edge E84. This domain is not used by default. Refer to the section Rework for enabling 1.8 V VDD operation of MCU to use this power domain

VDD/VDDIO_1V8_3V3 ( J24.2 ): This is a 1.8 V/3.3 V configurable (using J23 ) power rail used to power the Port 16 and Port 17 I/O domains of the PSOC™ Edge E84

VDDUSB_3V3 ( J18.2 ): This is a 3.3 V power rail used to power the VDDUSB domain of the PSOC™ Edge E84

VBAT_MCU ( J25.2 ): This is a 2.7 V/3.3 V/4.2 V configurable (using J22 ) power rail used to power the VBAT domain of the PSOC™ Edge E84. This domain is used by default

These power rails are connected through 2-pin headers ( J26 , J24 , J18 , J25 ) which can be used to enable/disable the power or current measurement of each domain of the PSOC™ Edge E84.

Apart from the MCU power, there is a VDD_PERI ( J23.2 ) power domain which is used to power some of the on board peripherals which are mainly connected to the Port 16 and Port 17 of the PSOC™ Edge E84. VDD_PERI can be configurable to 1.8 V or 3.3 V using

J23

which also configures the VDD/VDDIO_1V8_3V3 domain accordingly.

Note:

These headers (

J26

,

J24

,

J18

,

J25

,

J23

) are not recommended to change or remove while the board is powered on.

Jumper position | VDD_PERI |

|---|---|

1-2 | 1.8 V |

2-3 (Default) | 3.3 V |

There are three more power rails (VBAT_RADIO_3V3, VDD_MEM_1V8 and VDD/VDDIO_PERI_1V8) to power the other peripherals on the processor SoM (AIROC™ CYW55513 radio, memory sub-system and CAPSENSE™ co-processor) which are connected to their respective regulator outputs on the EVK through 0-ohm resistors (

R415

,

R414

and

R304

respectively). These resistors can be removed for current measurement of the respective domains by probing a with a current meter. Refer to the section 3.5 for the power monitoring setup details. Also note that, there is leakage path that need to be reworked (refer section Rework for PSOC™ Edge E84 MCU low power current measurement ) before power monitoring.

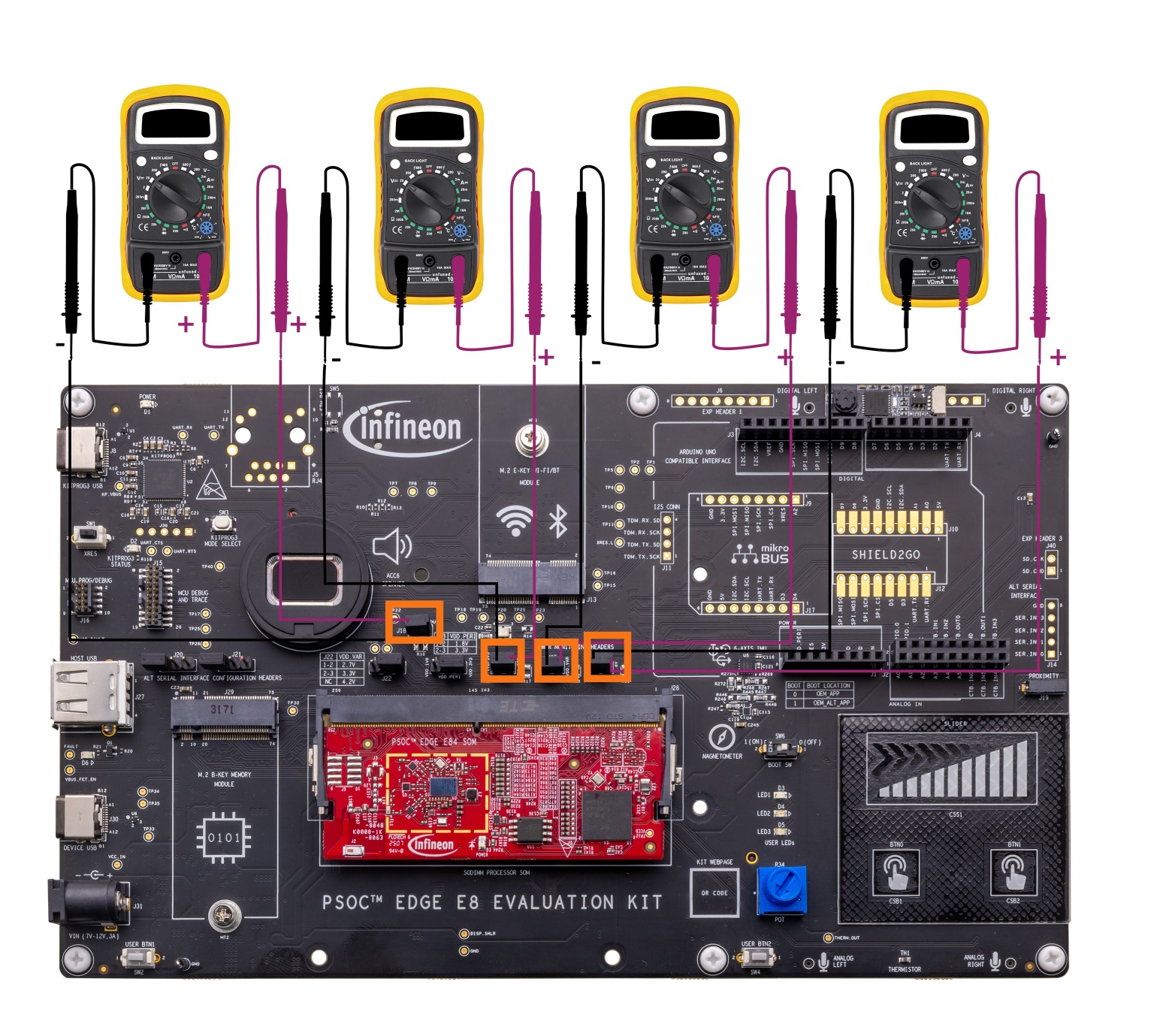

Figure 47.

Schematic of PSOC™ Edge E84 power selection and current monitoring headers

Ammeters can be connected across these jumpers

J18

(VDDUSB_3V3),

J24

(VDD/VDDIO_1V8_3V3),

J25

(VBAT_MCU),

J26

(VDD/VDDIO_1V8) to measure the current consumed by the PSOC™ Edge E84 MCU device. Remove the jumpers, connect the ammeters as shown and power the kit.

Figure 48.

Ammeter connection details for current measurement

Note:

Make sure to do the rework mentioned in the section

Rework for PSOC™ Edge E84 MCU low power current measurement

before performing current measurement.

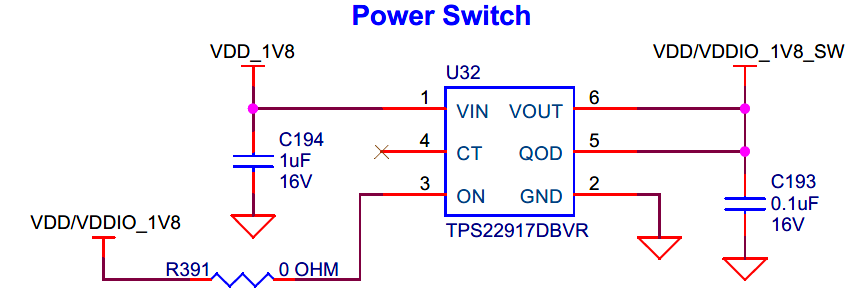

Power switch

Power switch for VTARG sense through on board KitProg3 to reduce current leakage on the power rail.

A power switch (

U32

) is provided to supply power for the VTARG_MEAS and P5LP_SIO_VREF resistor divider networks for the on board PSOC™ 5LP. The circuit is used to reduce the current leakage on the VDD/VDDIO_1V8 power domain.

Figure 49.

Schematic of power switch

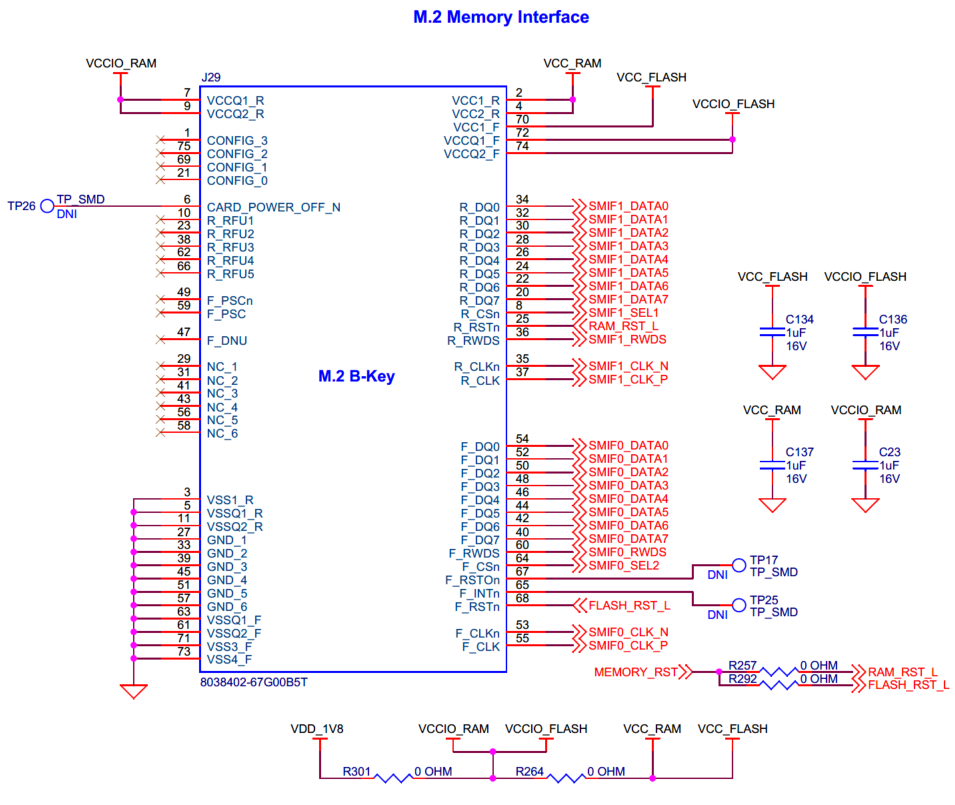

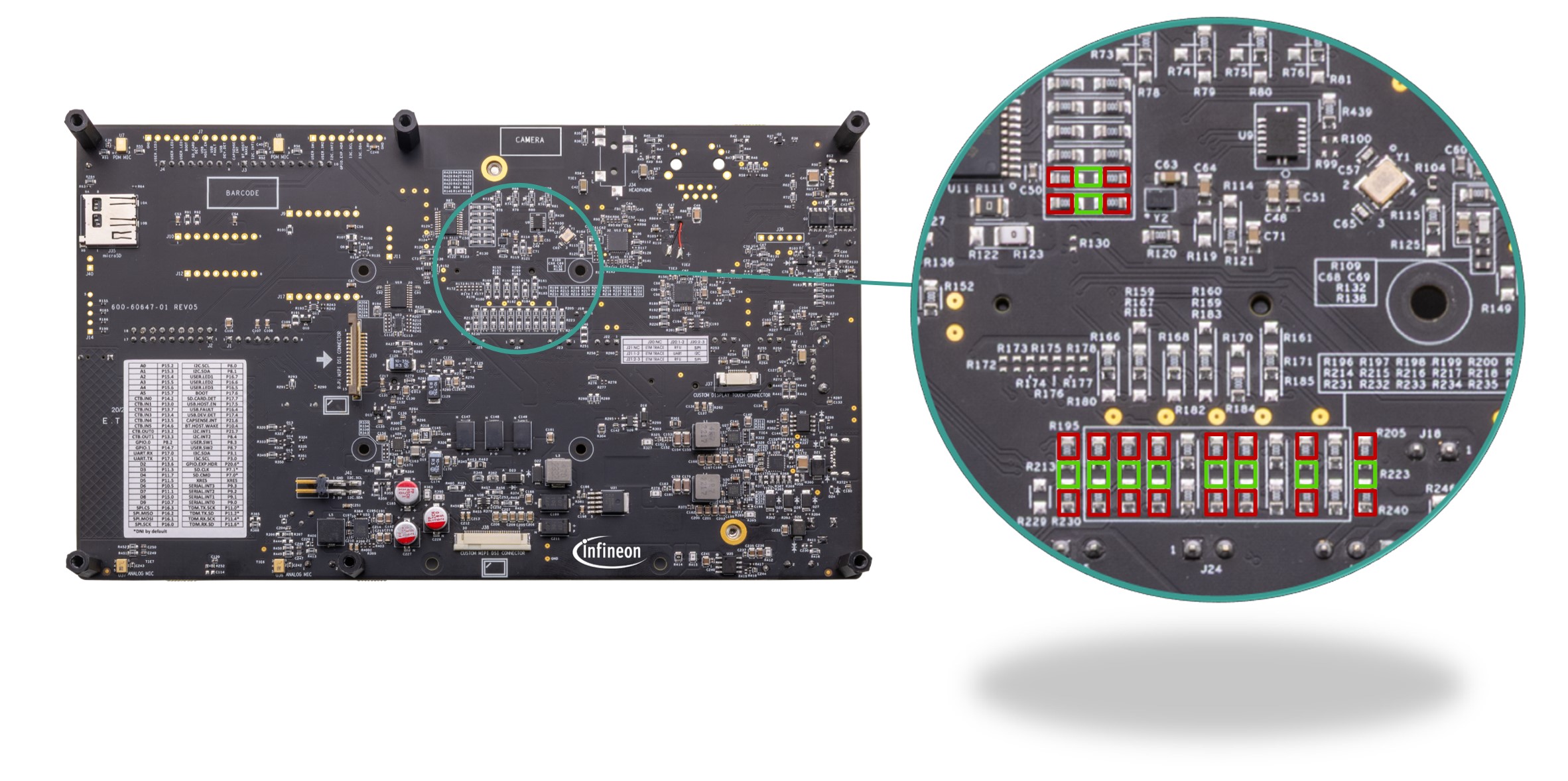

M.2 (B-Key) external memory interface

M.2 B-key memory interface for connecting external memory module.

The M.2 B-key external memory interface (

J29

) adds memory connectivity to PSOC™ Edge E84 MCU as required. The M.2 B-key memory module can be interfaced to the PSOC™ Edge E84 EVK. The external M.2 memory module comprises of a FLASH and a RAM device which are connected to the PSOC™ Edge E84 MCU using individual SMIF interface. FLASH device is connected to SMIF0 channel and RAM is connected to SMIF1 channel of the PSOC™ Edge E84 MCU. The supply for the module is provided from the 1.8 V (VDD_1V8) rail.

Note that this M.2 B-key external memory interface is not connected to the PSOC™ Edge E84 MCU by default. See

Rework for M.2 external memory interface

section for connection.

Group | Signal name | M.2 (E-Key) connector pin |

|---|---|---|

FLASH interface | SMIF0_CLK_P | 55 |

SMIF0_CLK_N | 53 | |

SMIF0_DATA0 | 54 | |

SMIF0_DATA1 | 52 | |

SMIF0_DATA2 | 50 | |

SMIF0_DATA3 | 48 | |

SMIF0_DATA4 | 46 | |

SMIF0_DATA5 | 44 | |

SMIF0_DATA6 | 42 | |

SMIF0_DATA7 | 40 | |

SMIF0_RWDS | 60 | |

SMIF0_SEL2 | 64 | |

FLASH_RST_L | 68 | |

RAM interface | SMIF1_CLK_P | 37 |

SMIF1_CLK_N | 35 | |

SMIF1_DATA0 | 34 | |

SMIF1_DATA1 | 32 | |

SMIF1_DATA2 | 30 | |

SMIF1_DATA3 | 28 | |

SMIF1_DATA4 | 26 | |

SMIF1_DATA5 | 24 | |

SMIF1_DATA6 | 22 | |

SMIF1_DATA7 | 20 | |

SMIF1_RWDS | 36 | |

SMIF1_SEL1 | 8 | |

RAM_RST_L | 25 |

Figure 50.

Schematic of M.2 (B-Key) memory interface

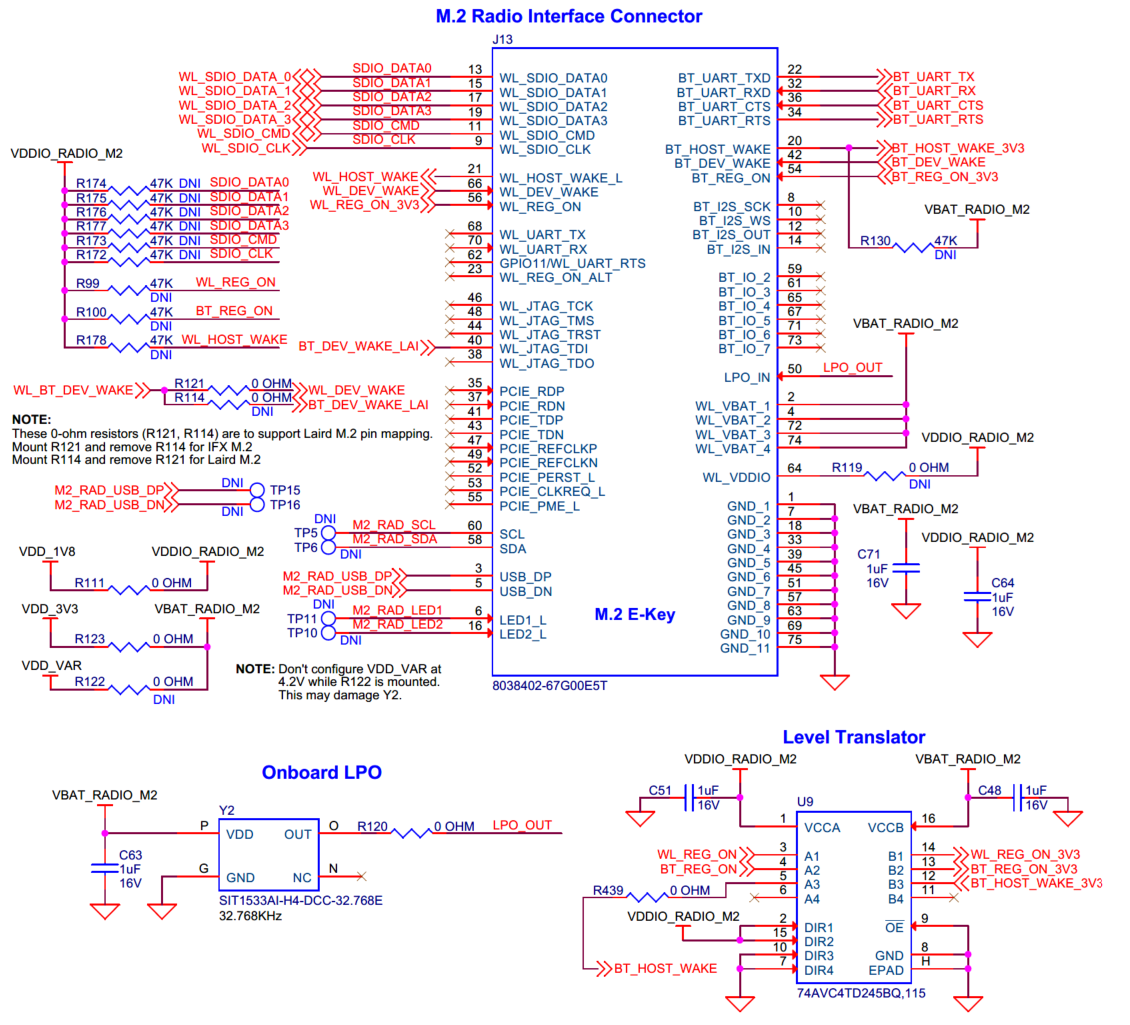

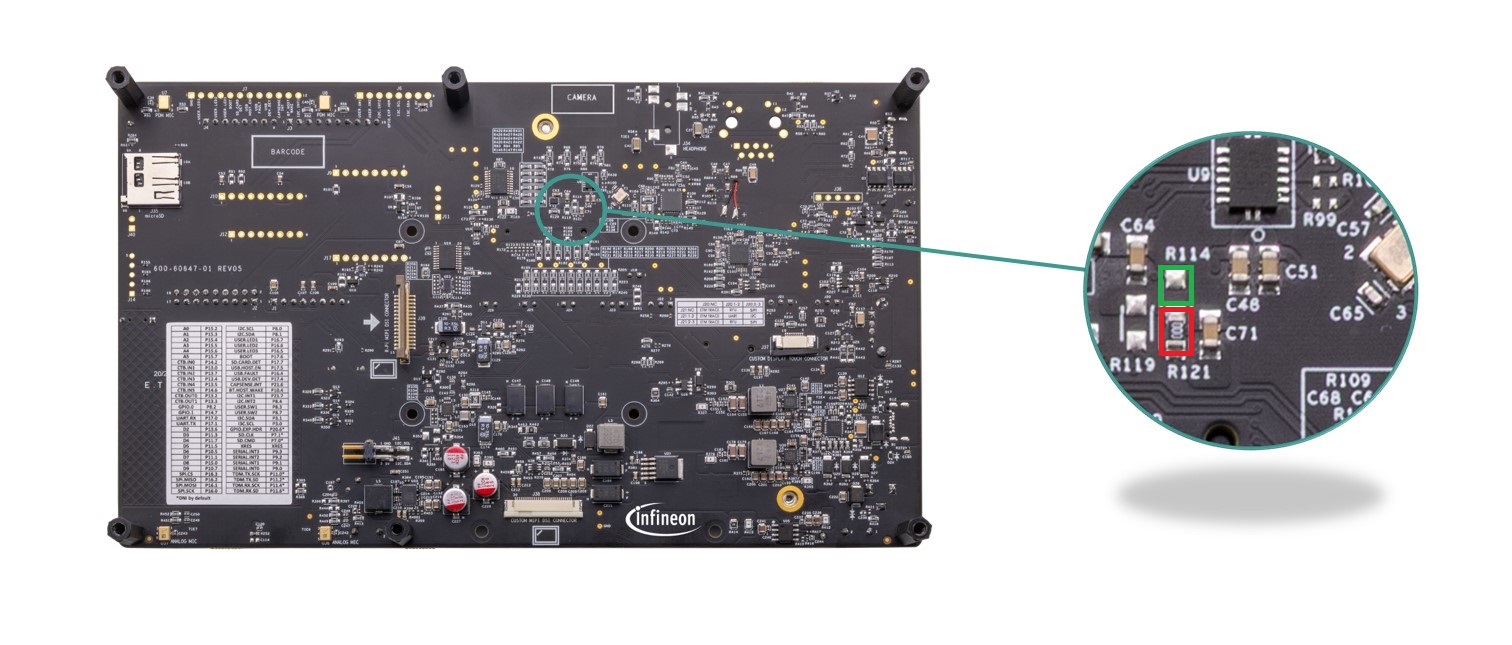

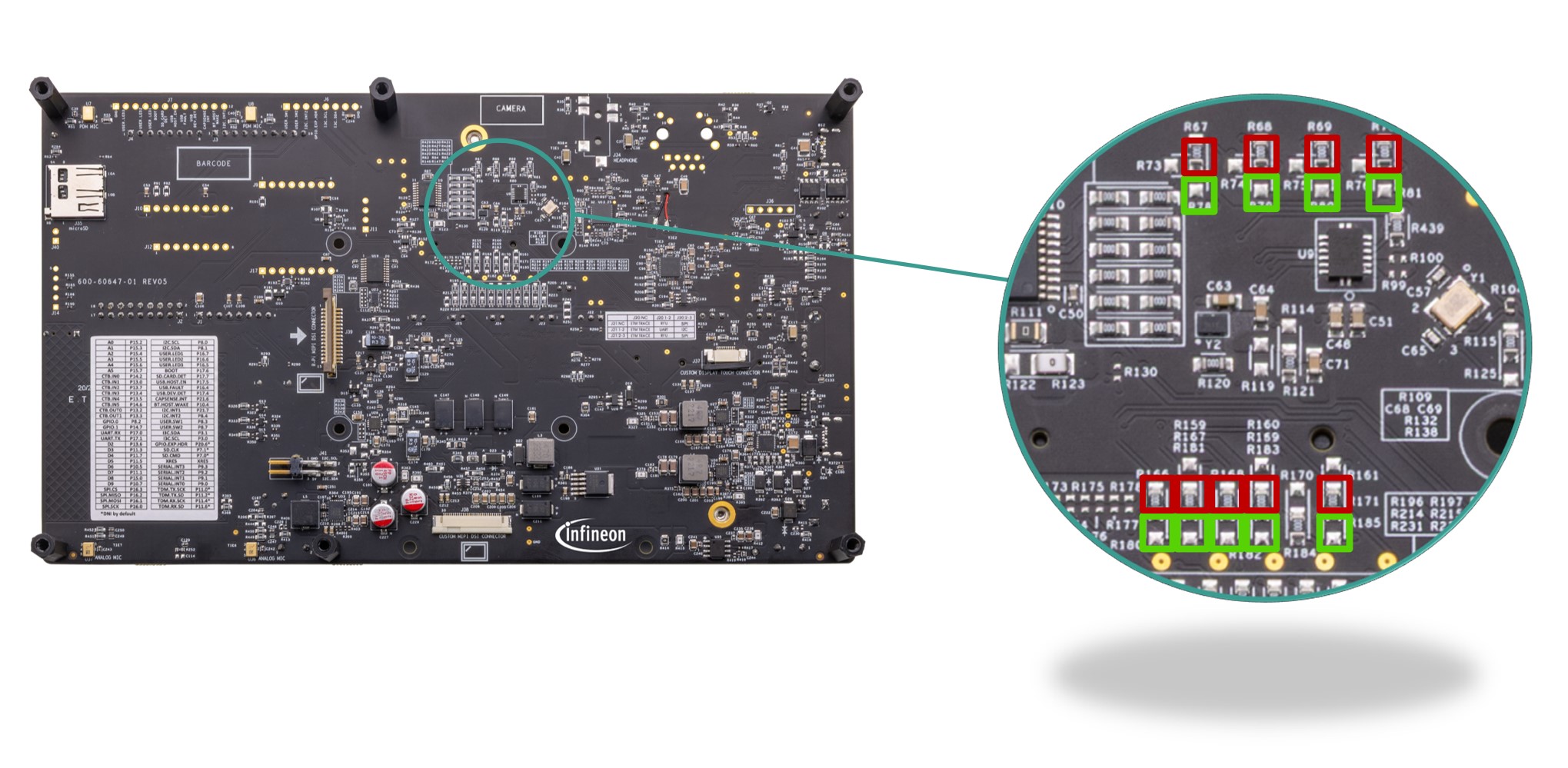

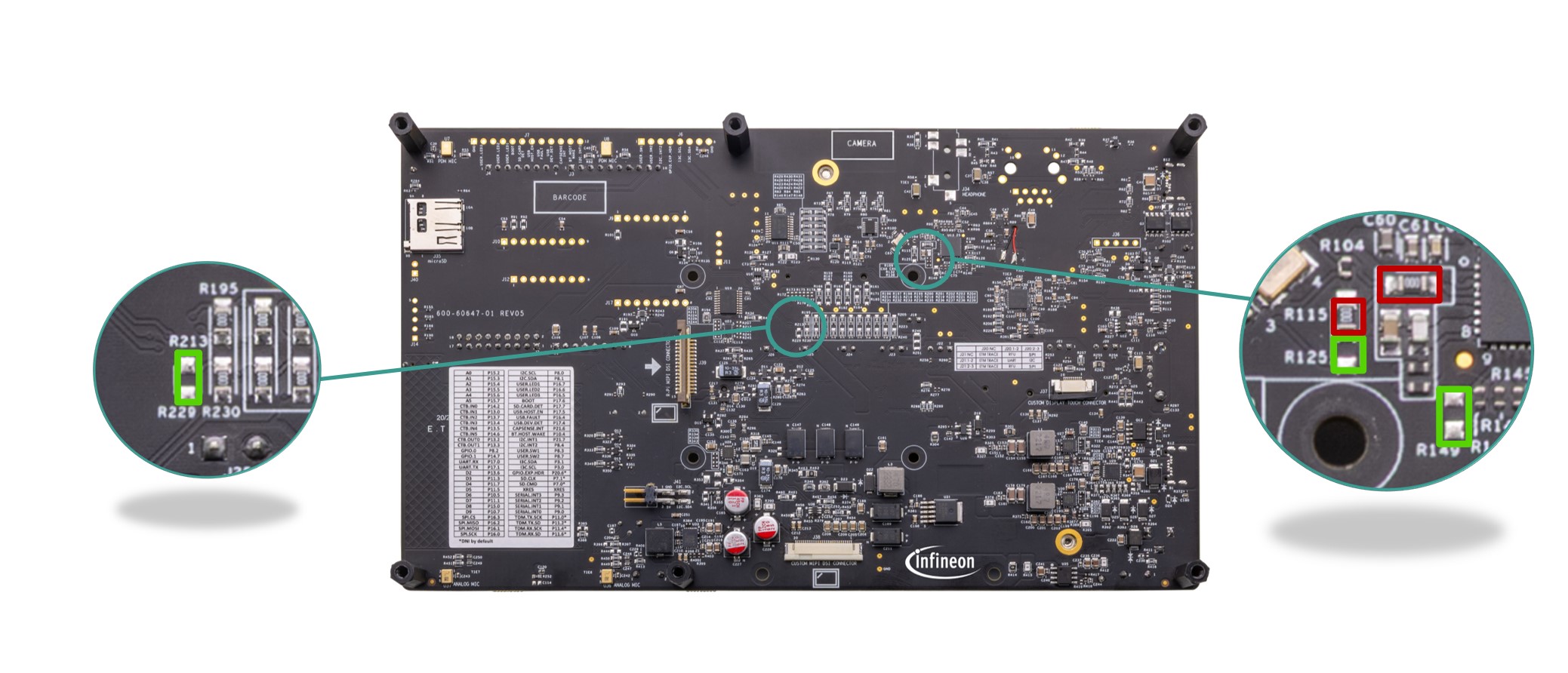

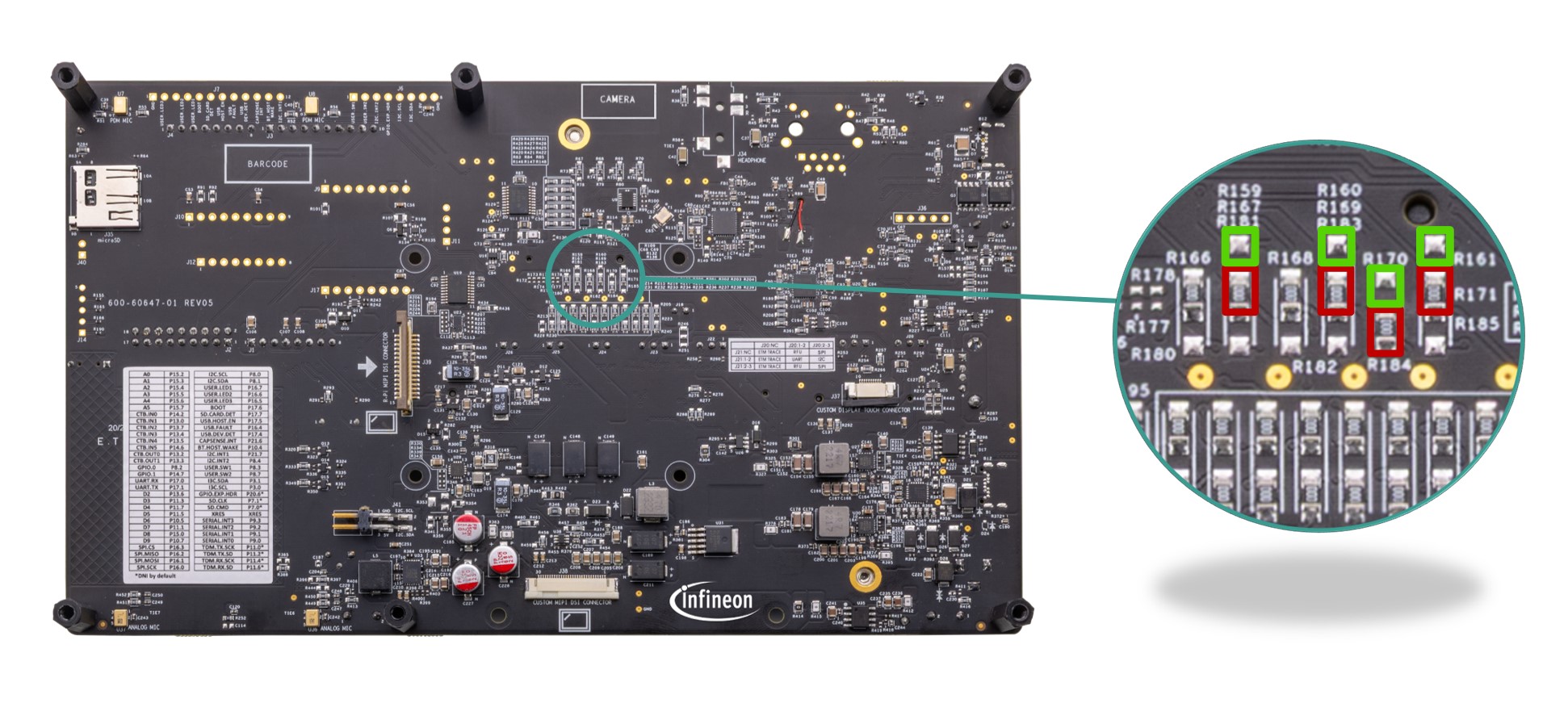

M.2 (E-Key) external radio interface

M.2 E-key radio interface for connecting external M.2 radio module.

The M.2 E-key external radio interface (

J13

) adds radio connectivity to PSOC™ Edge E84 MCU as required. Any

M.2 E-key radio module

, compatible with Infineon M.2 connector pin mapping, can be interfaced to the PSOC™ Edge E84 EVK. The WLAN interface to the PSOC™ Edge E84 MCU is SDIO and the Bluetooth® interface is UART. M.2 E-key interface also supports USB interface for the WLAN radio.

The VBAT supply (VBAT_RADIO_M2) for the module is provided from the 3.3 V (VDD_3V3) or 2.7 V-4.2 V variable power rail (VDD_VAR). VDDIO_RADIO_M2 is connected to 3.3 V (VDD_3V3) by default. It can be changed to VDD_VAR by removing

R123

and populating

R122

. On the other hand, the I/O supply (VDDIO_RADIO_M2) is provided from the 1.8 V (VDD_1V8) rail. Refer to the appropriate M.2 radio module datasheet for valid operating voltage. Also, an on-board LPO provides 32.786KHz external clock to the radio module via the M.2 interface.

Note that, this M.2 E-key external radio interface is not connected to the PSOC™ Edge E84 MCU by default. See

Rework for M.2 external radio interface

section for connection.

Group | Signal name | M.2 (E-Key) connector pin |

|---|---|---|

WLAN interface | SDIO_CLK | 9 |

SDIO_CMD | 11 | |

SDIO_DATA0 | 13 | |

SDIO_DATA1 | 15 | |

SDIO_DATA2 | 17 | |

SDIO_DATA3 | 19 | |

WL_HOST_WAKE | 21 | |

WL_REG_ON | 56 | |

WL_DEV_WAKE | 66 | |

Bluetooth® interface | BT_UART_TXD | 22 |

BT_UART_RXD | 32 | |

BT_UART_RTS | 34 | |

BT_UART_CTS | 36 | |

BT_HOST_WAKE | 20 | |

BT_DEV_WAKE | 42 | |

BT_REG_ON | 54 | |

Clock | LPO_IN | 50 |

Power | VBAT | 2, 4, 72, 74 |

WL_VDDIO (Not connected by default) | 64 |

Note:

Some modules from Laird Connectivity like Sterling-LWB5+ does not follow the Infineon M.2 interface standard. For such modules, use the resistor setting mentioned in

Rework for M.2 external radio interface

section.

Signal name | Infineon M.2 connector pin | Laird M.2 connector pin |

|---|---|---|

WL_DEV_WAKE | 66 | 42 |

BT_DEV_WAKE | 42 | 40 |

Figure 51.

Schematic of M.2 (E-Key) External Radio Interface

CAPSENSE™ interface

Capacitive buttons, slider, and shield

Capacitive buttons, 5-segment slider, and shield for EVK user interface.

The PSOC™ Edge E84 EVK has one CAPSENSE™ 5-segment slider (

CSS1

) and two CAPSENSE™ buttons (

CSB1

,

CSB2

) which are connected to the PSOC™ 4000T CAPSENSE™ Co-processor (CY8C4046LQI-T452). The CAPSENSE™ slider and buttons support both self-cap (CSD) and mutual cap (CSX) sensing modes for this kit. Note that the CAPSENSE™ shield is connected to ground by default. But it can also be configured to active shield drive mode by removing

R388

and populating

R385

. For details on using CAPSENSE™ including design guidelines, see the

PSOC™ 4 and PSOC™ 6 MCU CAPSENSE™ design guide

.

CAPSENSE™ element | PSOC™ 4000T GPIO | CAPSENSE™ element | PSOC™ 4000T GPIO |

|---|---|---|---|

CSB0 | P2[1] | CSS2 | P0[2] |

CSB1 | P2[4] | CSS3 | P0[3] |

CS_TX1 | P2[0] | CSS4 | P0[4] |

CSS0 | P0[0] | CS_TX2 | P1[0] |

CSS1 | P0[1] | CSH | P3[0] |

Figure 52.

Schematic of capacitive buttons, slider, and shield

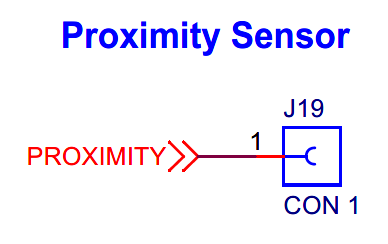

Proximity sensor interface

Proximity sensor interface for EVK.

The PSOC™ Edge E84 EVK has an onboard proximity sense connector (

J19

) which can be used for proximity sensing applications. This pin is connected to

P4[0]

pin of the PSOC™ 4000T CAPSENSE™ co-processor (CY8C4046LQI-T452).

Figure 53.

Schematic of proximity sensor interface

I/O headers

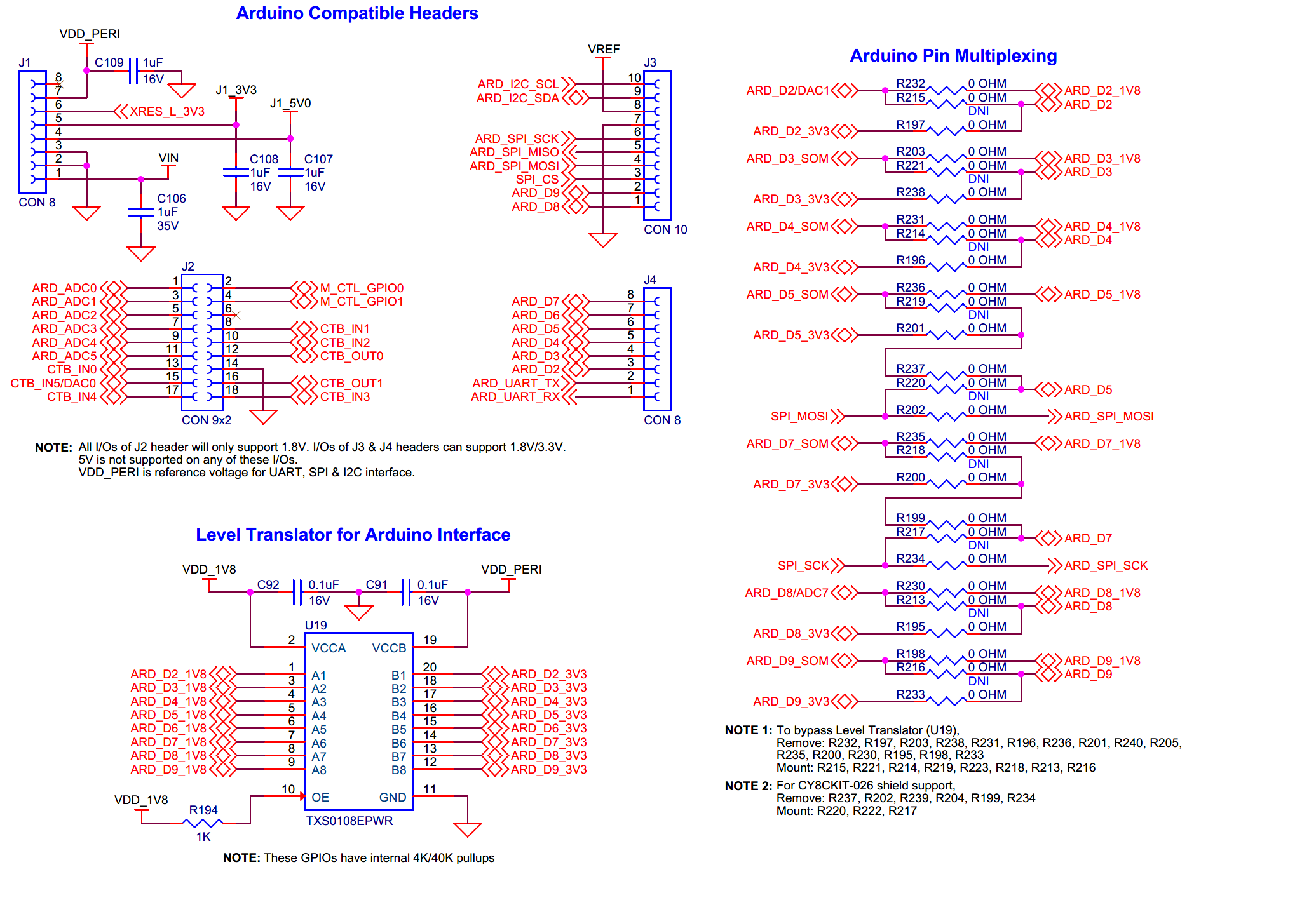

Arduino compatible headers

Arduino compatible headers for EVK.

The board has four Arduino compatible headers:

J1

,

J2

,

J3

and

J4

. You can connect Arduino compatible shields to develop applications based on the shield’s hardware. Do note that, all I/Os of

J2

header will only support 1.8 V. I/Os of

J3

and

J4

headers can support 1.8 V/3.3 V (3.3 V by default). VDD_PERI is reference voltage for UART, SPI and I2C interfaces which can be set to 1.8 V/3.3 V (3.3 V by default). 5 V is not supported on any of these I/Os and connecting a 5 V shield may permanently damage the board. The Arduino I/Os are also shared with the on board IFX Shield2Go (

J10

and

J12

) and MikroBUS Click headers (

J9

and

J17

) as well. So only one of these interfaces can be used at a time and may not work concurrently. See

Figure 3

for details on PSOC™ Edge E84 MCU pin mapping to these headers.

There are two reverse voltage protection circuits on 3.3 V (J1_3V3) and 5 V (J1_5V0) power rails connected to the Arduino power header (

J1

) as well as to mikroBUS Click headers (

J9

,

J17

) and IFX Shield2Go header (

J10

) to protect the on board peripherals and regulators from reverse voltage. The I/Os

ARD_D2

to

ARD_D9

,

ARD_I2C_SCL

and

ARD_I2C_SDA

are connected to the Arduino headers through level translators (

U19

,

U11

) using which the logic level of these I/Os can be configured to 1.8 V/3.3 V (by changing VDD_PERI from

J23

). But there is also a provision to bypass the level translators by changing the multiplexing resistors as mentioned in the

Rework for bypassing Arduino interface level translator

section. This provision is provided in case the level translators (

U19

,

U11

) fail to work at higher speeds and hence can be bypassed. Note that if the level translators are bypassed, the logic voltage of the I/Os will be as same as the MCU logic level which is 1.8 V.

The list of supported Infineon's Arduino-compatible shields are as follows:

Shield | Features not supported (if any) | Rework |

|---|---|---|

CY8CKIT-026 CAN and LIN Shield | - | Yes 5 |

CY8CKIT-028-EPD E-INK Display Shield | PDM, EPD display, IMU interrupt (optional) | No |

CY8CKIT-028-TFT TFT Display Shield | PDM, TFT display | No |

CY8CKIT-028-SENSE IoT Sense Expansion Kit | PDM, Codec, Pressure sensor interrupt (optional) | No |

CY15FRAMKIT-001 Serial F-RAM Development Kit | Write protect of FRAMs (optional) | No |

CY15FRAMKIT-002 F-RAM Development Kit | - | No |

CY8CKIT-032 PSOC™ 4 AFE Shield | LED1 control, Mechanical BTN1 read | No |

XENSIV™ Sensor Shield | PDM, IMU interrupt (optional) | No |

Figure 54.

Schematic of Arduino-compatible headers

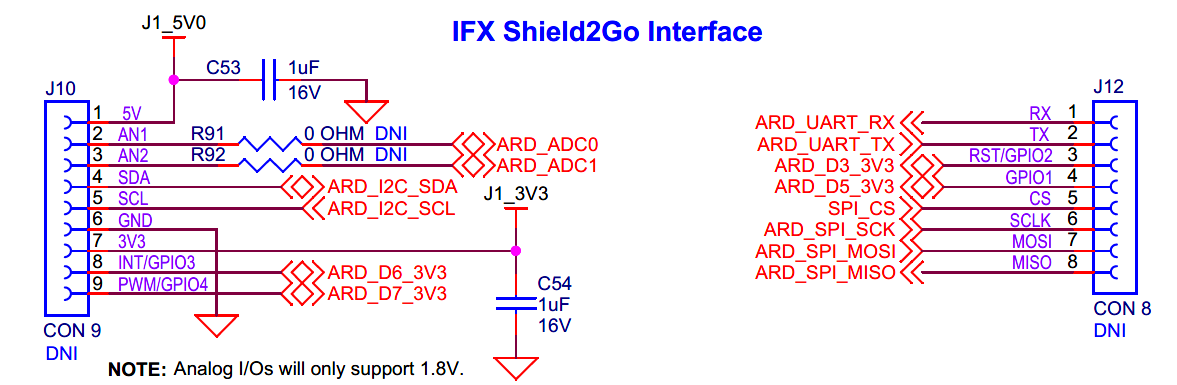

Infineon's Shield2Go interface

Infineon’s Shield2Go interface for EVK.

The board has two headers compatible with Infineon’s Shield2Go interface (

J10

and

J12

) to support different add-on boards compatible with Infineon’s Shield2Go interface. These headers (

J10

and

J12

) are not populated by default on the board. You can connect 1.8 V/3.3 V (based on

J23

position, 3.3 V by default) Shield2go boards to develop applications. But it doesn’t support 5 V shields, so connecting a 5 V add-on board may permanently damage the board. Note that the analog I/Os (ARD_ADC0, ARD_ADC1) will only support 1.8 V and are not connected by default. Populate

R91

,

R92

to connect the analog I/Os to the header. See

Figure 3

for details on PSOC™ Edge E84 MCU pin mapping to these headers.

Note:

Recommended part MPN:

J10

→ PPPC091LFBN-RC,

J12

→ PPPC081LFBN-RC

Shield | Supply voltage | |

|---|---|---|

1 | XENSIV™ TLI4971 current sensor | 3.1 V - 3.5 V (3.3 V typical) |

2 | XENSIV™ DPS310/DPS368 pressure sensors | 1.7 V - 3.6 V (3.3 V typical) |

3 | XENSIV™ IM69D130 MEMS microphone | 3.3 V (typical), 1.8 V supported with rework |

4 | XENSIV™ BGTLTR11AIP 60 GHz radar | To be discussed |

5 | XENSIV™ TLE493D/TLI493D 3D magnetic sensor | 2.8 V - 3.5 V (3.3 V typical) |

6 | XENSIV™ TLE4966K hall effect sensor | 2.7 V - 24 V (3.3 V typical) |

7 | XENSIV™ TLE4964 hall effect sensor | 3 V - 32 V (3.3 V typical) |

8 | XENSIV™ PAS CO2 sensor | 12 V (IR Emitter), 3.3 V (Core) |

9 | S2Go Security OPTIGA™ Trust M | 3.13 V - 3.63 V (3.3 V typical) |

10 | S2Go Security OPTIGA™ E | 3.13 V - 3.63 V (3.3 V typical) |

11 | S2GO Security OPTIGA™ X | 3.13 V - 3.63 V (3.3 V typical) |

Figure 55.

Schematic of Infineon's Shield2Go interface

mikroBUS Click interface by MikroElektronika

MikroBUS Click interface for EVK.

The board has two headers compatible with mikroBUS Click interface (

J9

and

J17

) to support different add-on boards compatible with mikroBUS by MikroElektronika. These headers (

J9

and

J17

) are not populated by default on the board. You can connect 3.3 V (based on

J23

position, 3.3 V by default) mikroBUS Click add-on shields to develop applications. But it does not support 5 V shields, so connecting a 5 V add-on board may permanently damage the board. Note that the analog I/O (ARD_ADC2) will only support 1.8 V and is not connected by default. Populate

R101

to connect the analog I/O to the header. See

Figure 3

for details on PSOC™ Edge E84 MCU pin mapping to these headers.

Note:

Recommended part MPN:

J9

,

J17

→ PPPC081LFBN-RC

Figure 56.

Schematic of mikroBUS Click interface by MikroElektronika

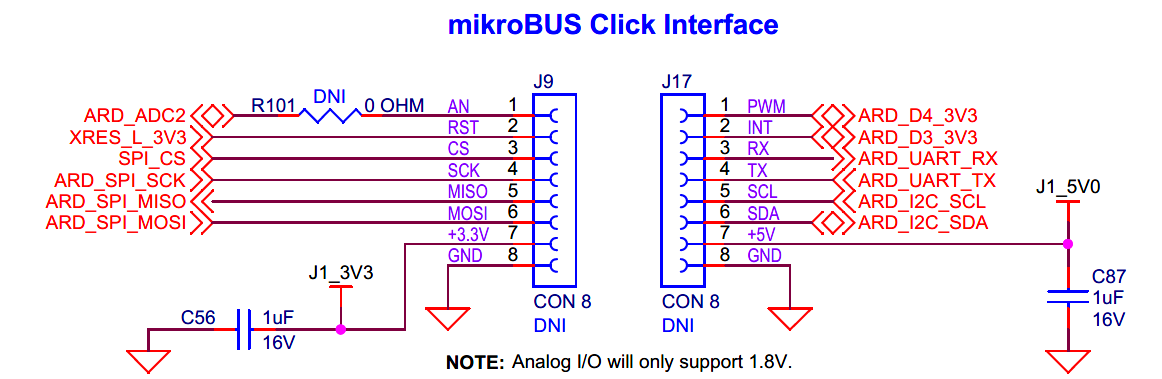

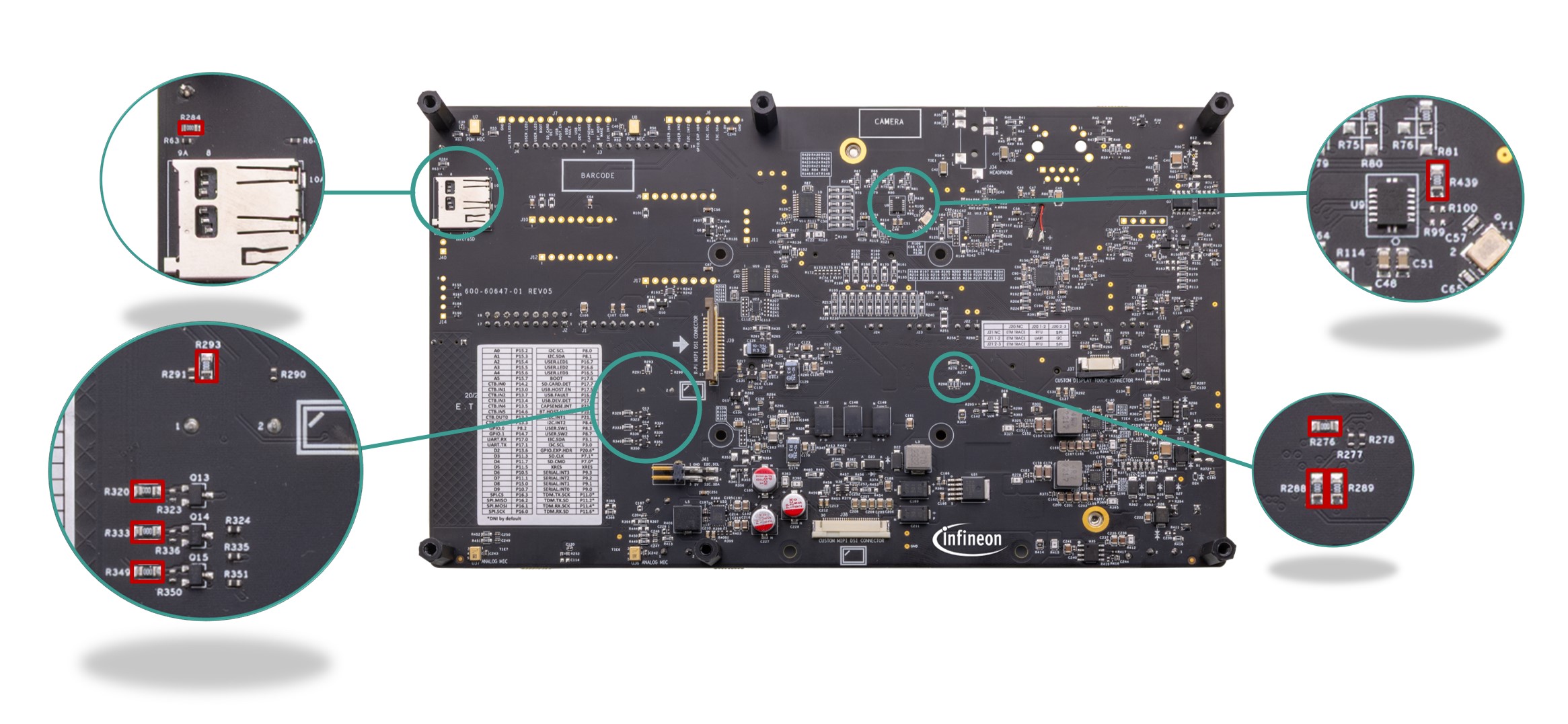

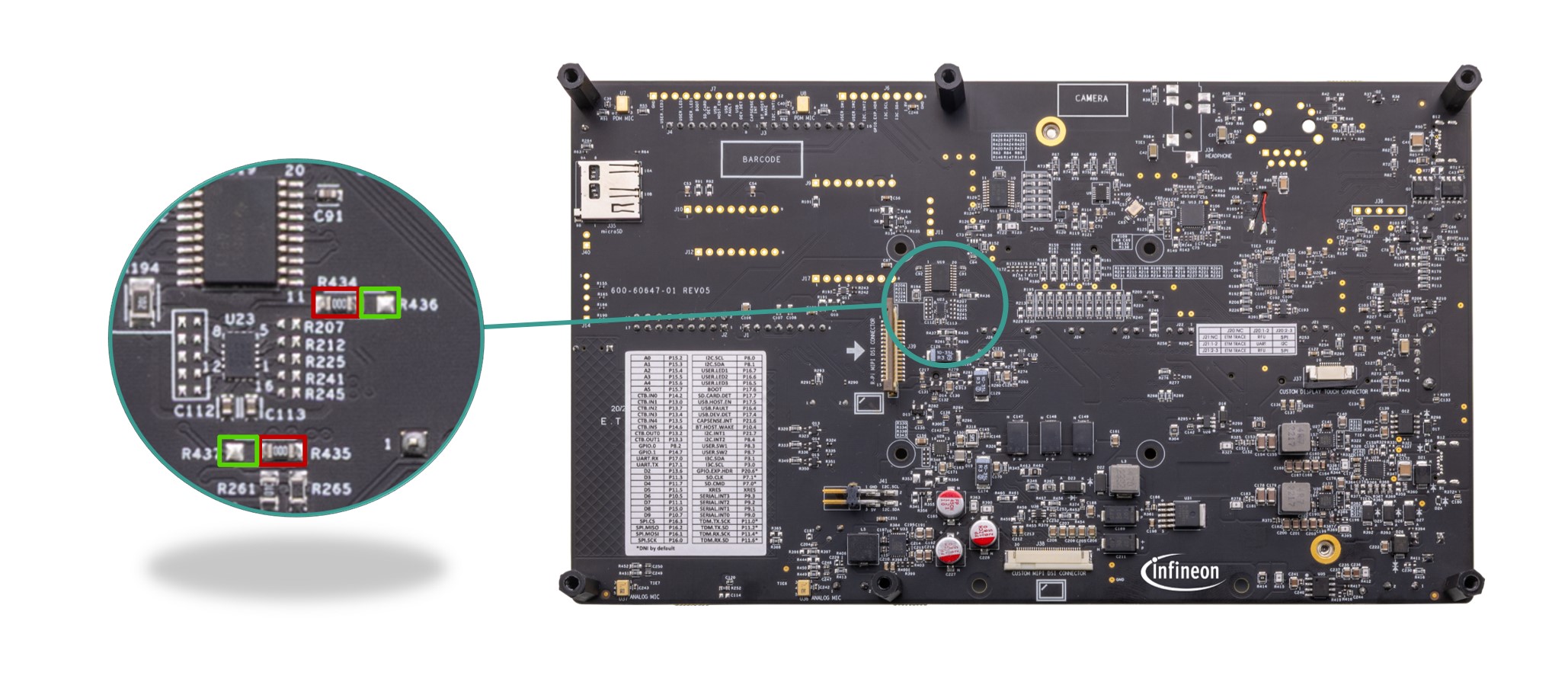

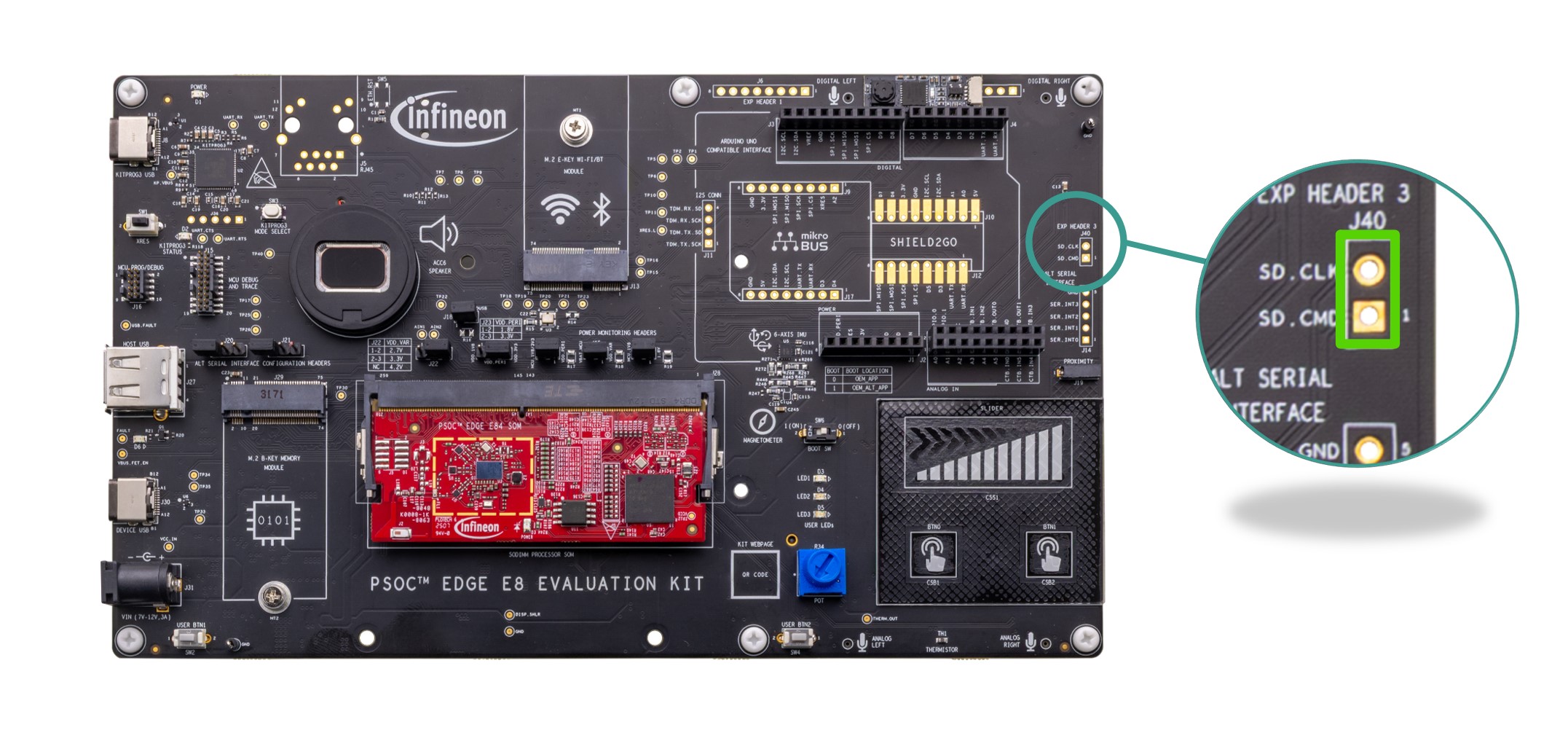

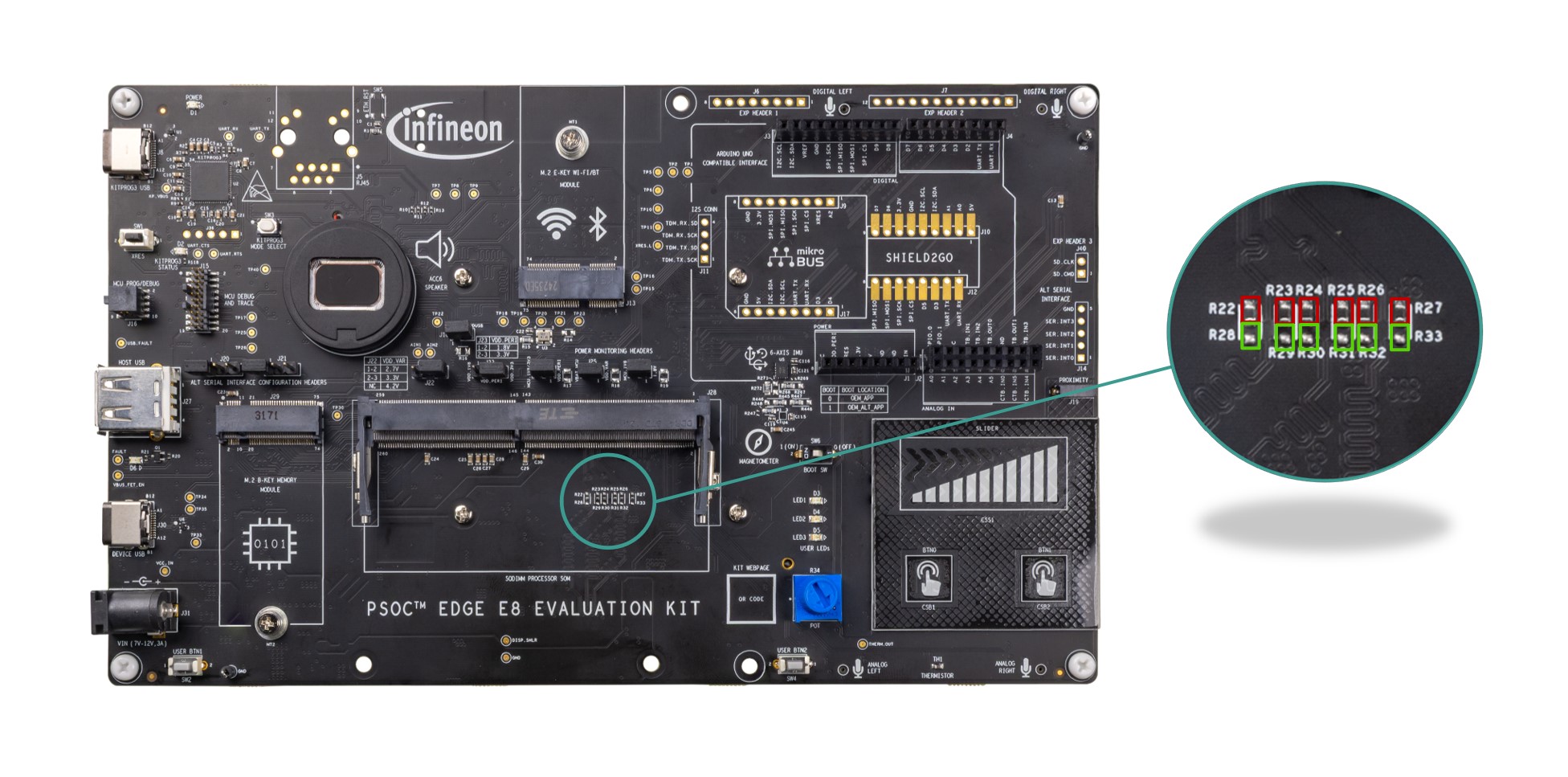

Expansion headers

Expansion headers for EVK.

There are three expansion headers (

J6

,

J7

,

J40

) which provide connectivity to PSOC™ Edge E84 MCU GPIOs that are multiplexed with on board peripheral pins. Therefore, it is recommended to disconnect these pins from the on board peripherals before using these pins as GPIOs. For detailed information on how to rework the kit to use these pins, see

Rework for expansion headers

section. Note that these expansion headers (

J6

,

J7

,

J40

) are not loaded on board by default. See

Figure 3

for details on PSOC™ Edge E84 MCU pin mapping to these headers.

Note:

Recommended part MPN:

J6 →

PPPC081LFBN-RC,

J7

→ PPPC121LFBN-RC,

J40

→ PPPC021LFBN-RC

Figure 57.

Schematic of expansion headers

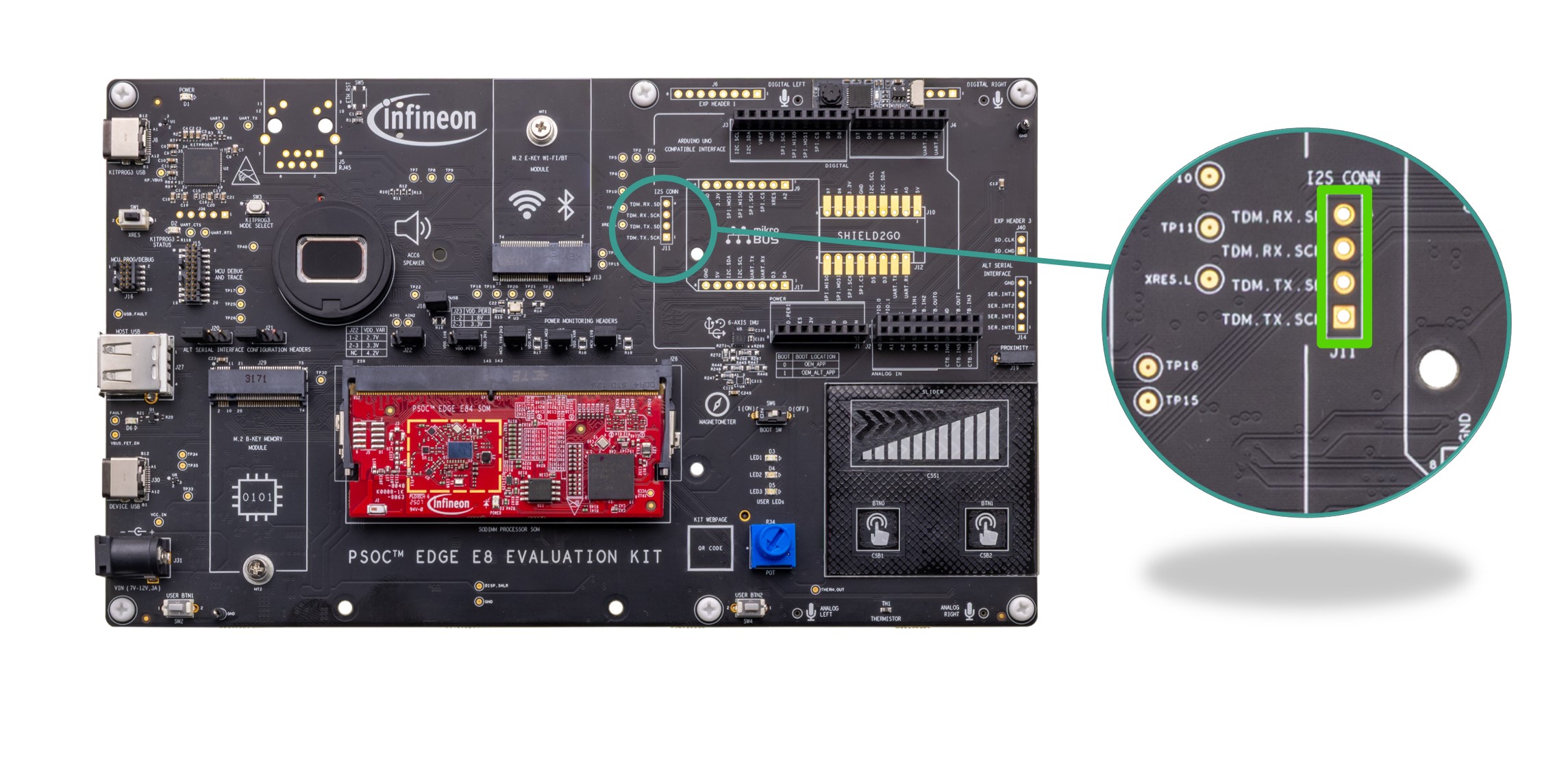

Extended I2S interface

Extended I2S interface for EVK.

There is an extended I2S header (

J11

) on the board which exposes four of the TDM[1] port I/Os which are not exposed on the Arduino compatible header. See

Figure 3

for details on PSOC™ Edge E84 MCU pin mapping to these headers. The other TDM[1] port I/Os exposed on the Arduino header (

J4

) are

ARD_D3

,

ARD_D4

,

ARD_D5

and

ARD_D7

which can be used along with these extended I2S header I/Os as an expanded I2S interface to connect to external audio shields. The extended I2S header (

J11

) is not populated on the board by default. The I/Os of this header are multiplexed with radio and Ethernet interfaces and are not connected by default. See Rework for extended I2S interface section for instruction of using this header.

Note that these I/Os are connected through an on board level translator (

U11

) which gives the provision to configure the logic level of these I/Os to 1.8 V/3.3 V by changing the VDD_PERI from

J23

. By default, the logic level is set to 3.3 V. Also, there is a provision to bypass the level translator and connect the GPIOs directly to the header.

Figure 58.

Schematic of extended I2S interface

Alternative serial interface

There is an alternative serial interface header (

J14

) on board. The alternate serial interfaces allows provisioning and downloading applications using Infineon's proprietary Device Firmware Update (DFU) protocolwith the default pre-programmed version of the extended boot. This serial interface can be configured as a SPI, UART or I2C interface based on the

J20

,

J21

jumper configurations as shown in the

Table 17

. Note that these headers (

J20

,

J21

) are also used to configure the ETM TRACE interface which is set by default. The Alternative serial interface header (

J14

) is not populated by default on the board. See

Figure 3

for details on PSOC™ Edge E84 MCU pin mapping to these headers.

Note:

Recommended part MPN:

J14 →

PPTC051LFBN-RC

J20: NC | J20: 1-2 | J20: 2-3 | |

|---|---|---|---|

J21: NC | ETM TRACE (Default) | RFU* | SPI |

J21: 1-2 | ETM TRACE | UART | I2C |

J21: 2-3 | ETM TRACE | RFU* | SPI |

*RFU - Reserved for Future Use

GPIO pins are configured by extended boot as per the selected interface, as shown in the following table.

Serial interface | Serial interface pins | GPIO | J14 Connector Pin | J14 Connector pin name |

|---|---|---|---|---|

I2C | SCL | P9.3 | J14.4 | SERIAL_INT3 |

SDA | P9.2 | J14.3 | SERIAL_INT2 | |

UART | RX | P9.3 | J14.4 | SERIAL_INT3 |

TX | P9.2 | J14.3 | SERIAL_INT2 | |

SPI | SCLK | P9.3 | J14.4 | SERIAL_INT3 |

MISO | P9.1 | J14.2 | SERIAL_INT1 | |

MOSI | P9.2 | J14.3 | SERIAL_INT2 | |

SS | P9.0 | J14.1 | SERIAL_INT0 |

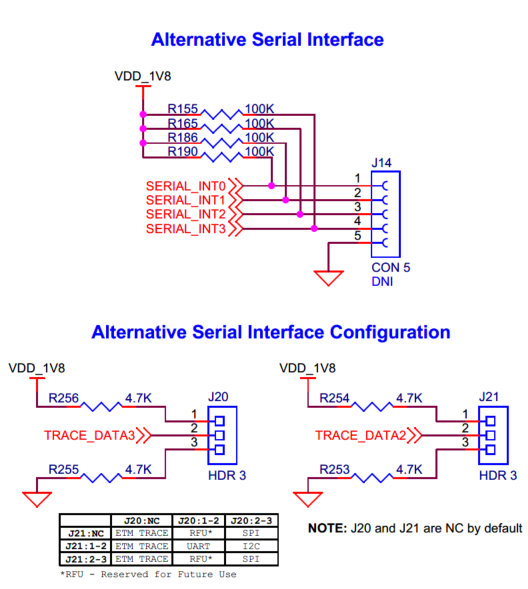

Figure 59.

Schematic of alternative serial interface

Audio subsystem

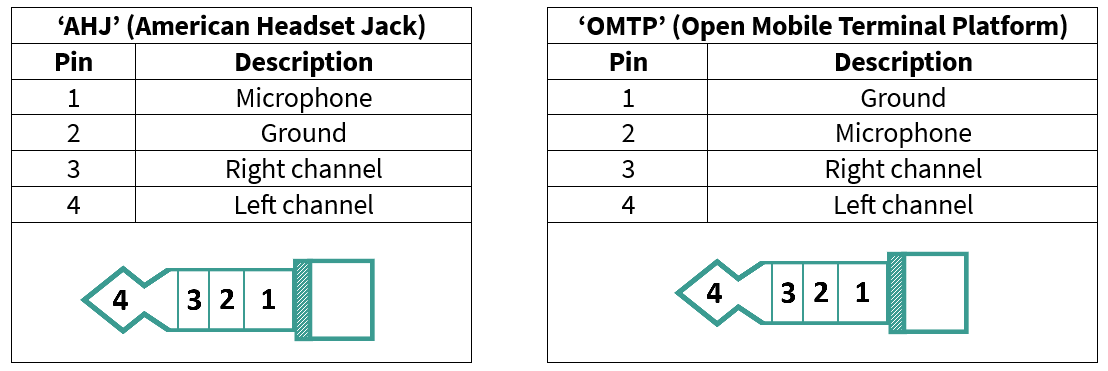

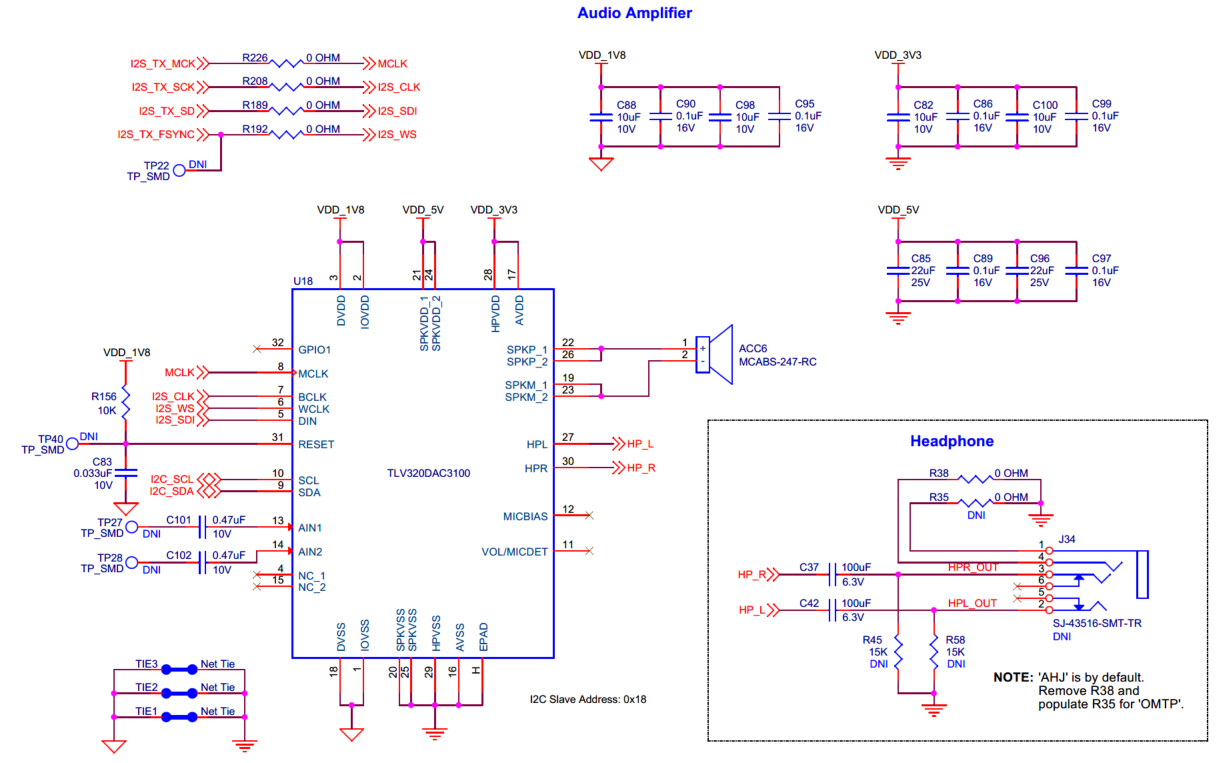

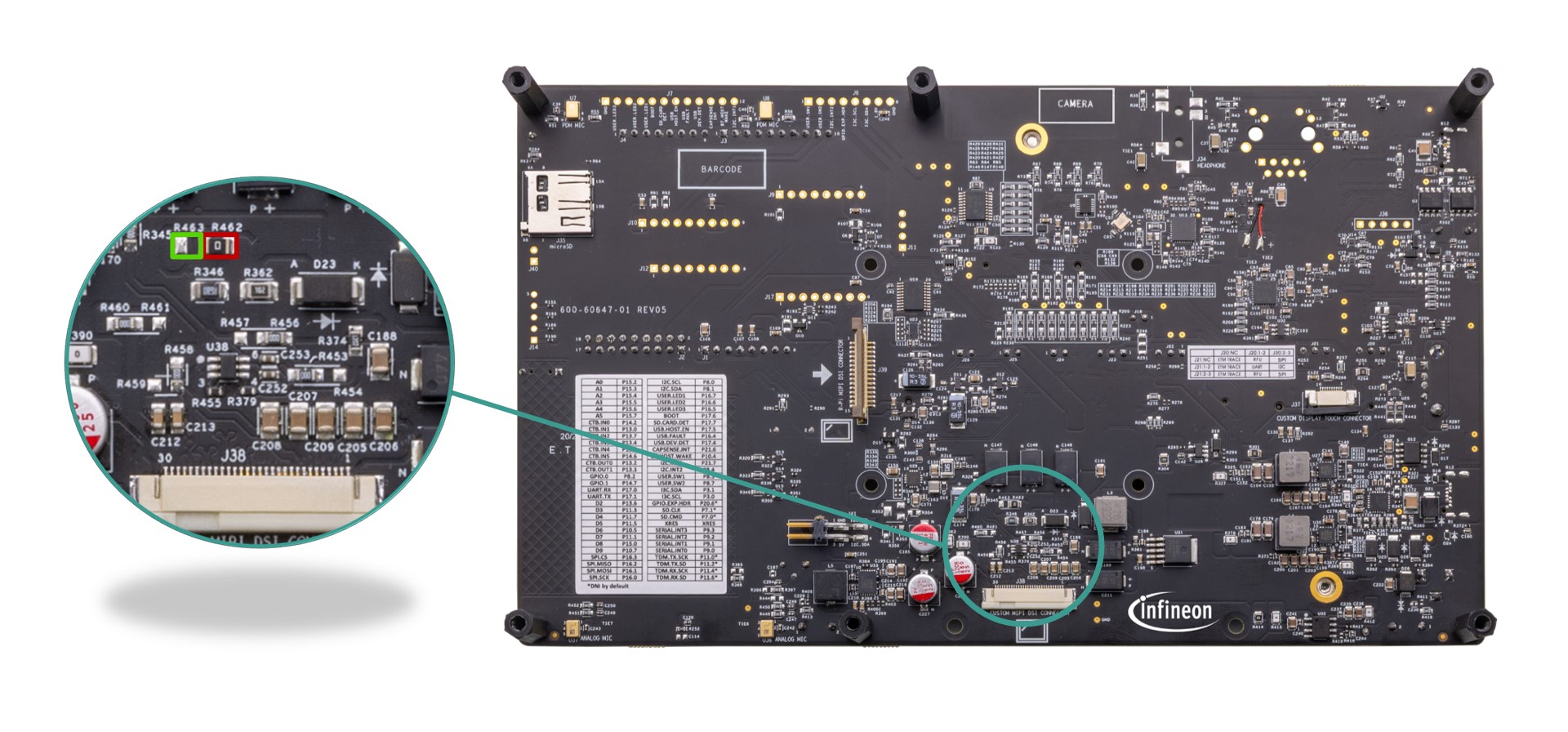

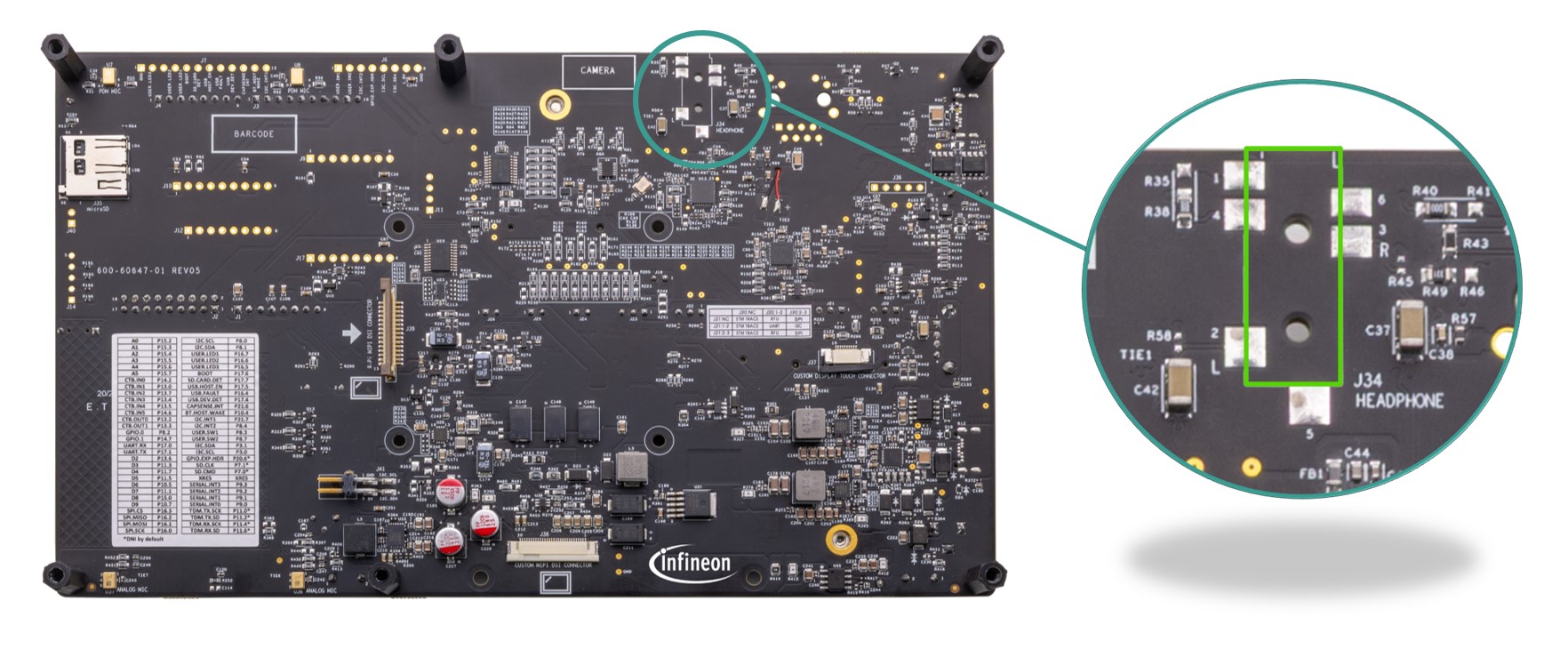

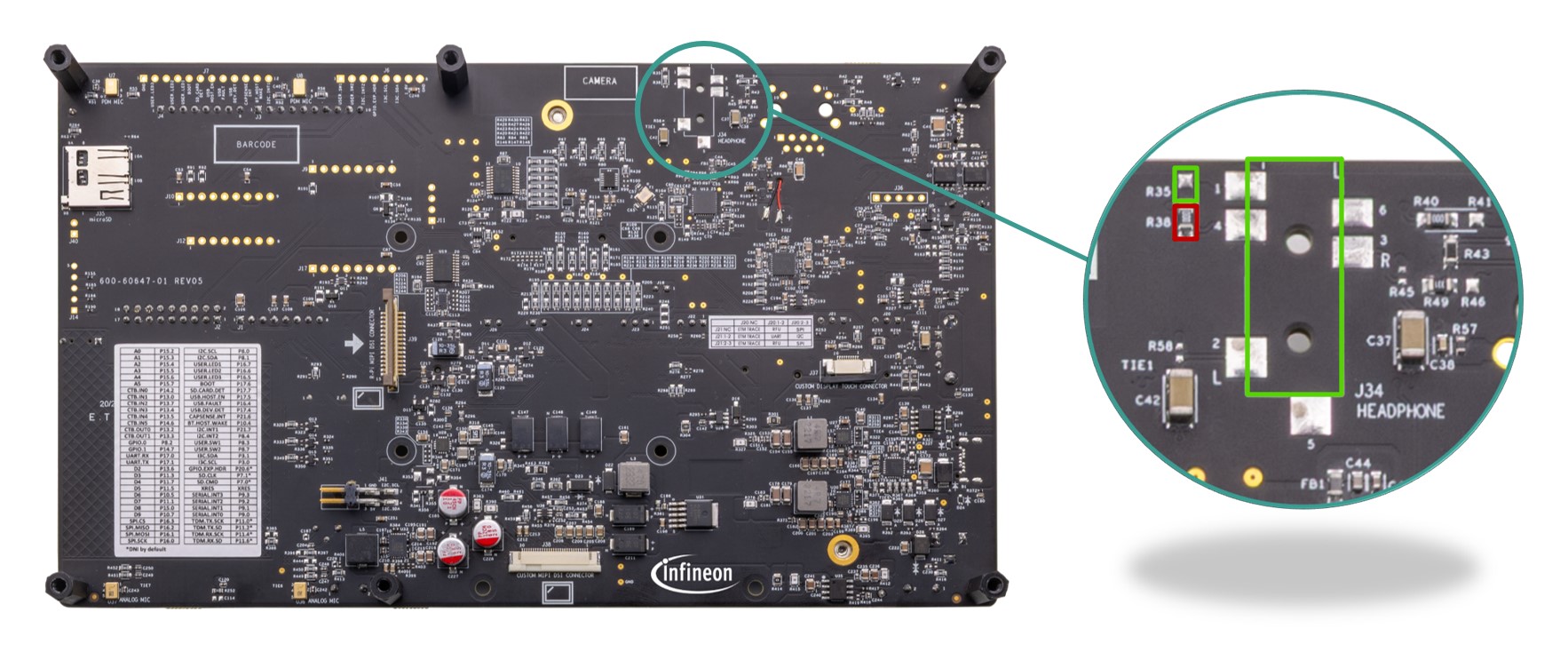

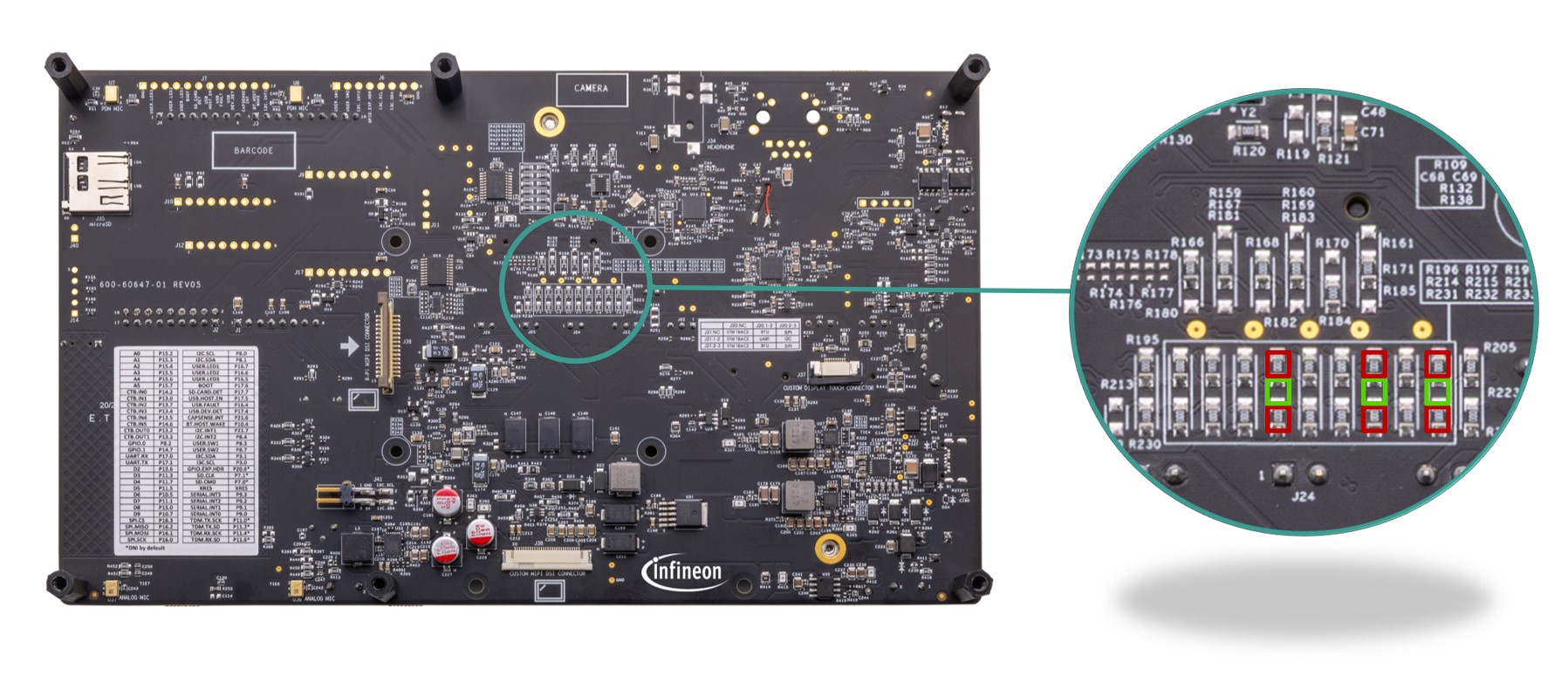

Audio amplifier

Audio class-D speaker driver and class A/B headphone driver for EVK.

The kit contains an audio amplifier (

U18

), which is a low-power, highly integrated, high-performance stereo audio DAC with 24-bit stereo playback and digital audio processing blocks which supports of 8KHz to 192KHz sampling rates. It contains a Class-D BTL mono speaker driver and a Class A/B stereo headphone driver. The amplifier is connected to a 0.8 W, 8 Ω mono speaker (

ACC6

) and also to a headphone jack (

J34

) which can deliver up to 30 mW per channel into a 16 Ω load. The headphone jack (

J34

) can be configured to either AHJ (American Headset Jack) or OMTP (Open Mobile Terminal Platform) mode and is not populated by default on the board. AHJ is supported by default. See

Rework for Headphone AHJ and OMTP Modes

section for details to change it to OMTP.

Note:

Recommended part MPN:

J34

→ SJ-43516-SMT-TR

Figure 60.

AHJ and OMTP headphone configuration

Additionally, there is a pair of analog input L/R channels (

AIN1

,

AIN2

) which can be used as input for analog audio signal. The amplifier is interfaced with PSOC™ Edge E84 MCU on the EVK via an I2S interface for audio data communication and an I2C interface which provides control and full access on the registers and the state machines. The amplifier’s DVDD, IOVDD domains are supplied from 1.8 V (VDD_1V8); AVDD, HPVDD domains are supplied from 3.3 V (VDD_3V3) and SPKVDD domain from 5 V (VDD_5V). The I2C device slave address is

0x18

.

Signal name | PSOC™ Edge E84 I/O | Logic level |

|---|---|---|

MCLK | P21[3] | 1.8 V |

I2S_CLK | P21[2] | 1.8 V |

I2S_SDI | P21[1] | 1.8 V |

I2S_WS | P12[3] | 1.8 V |

Figure 61.

Schematic of audio amplifier

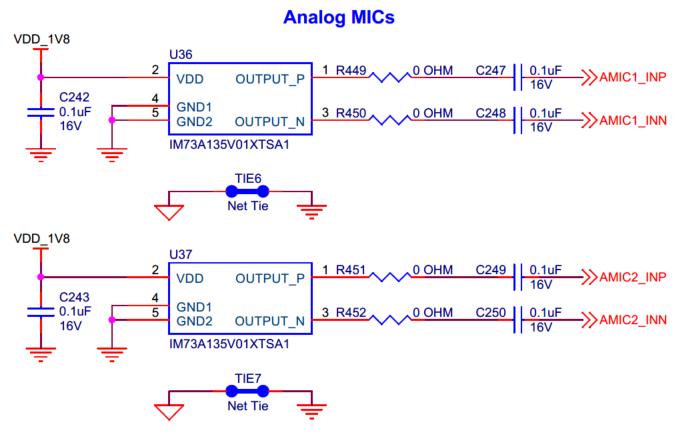

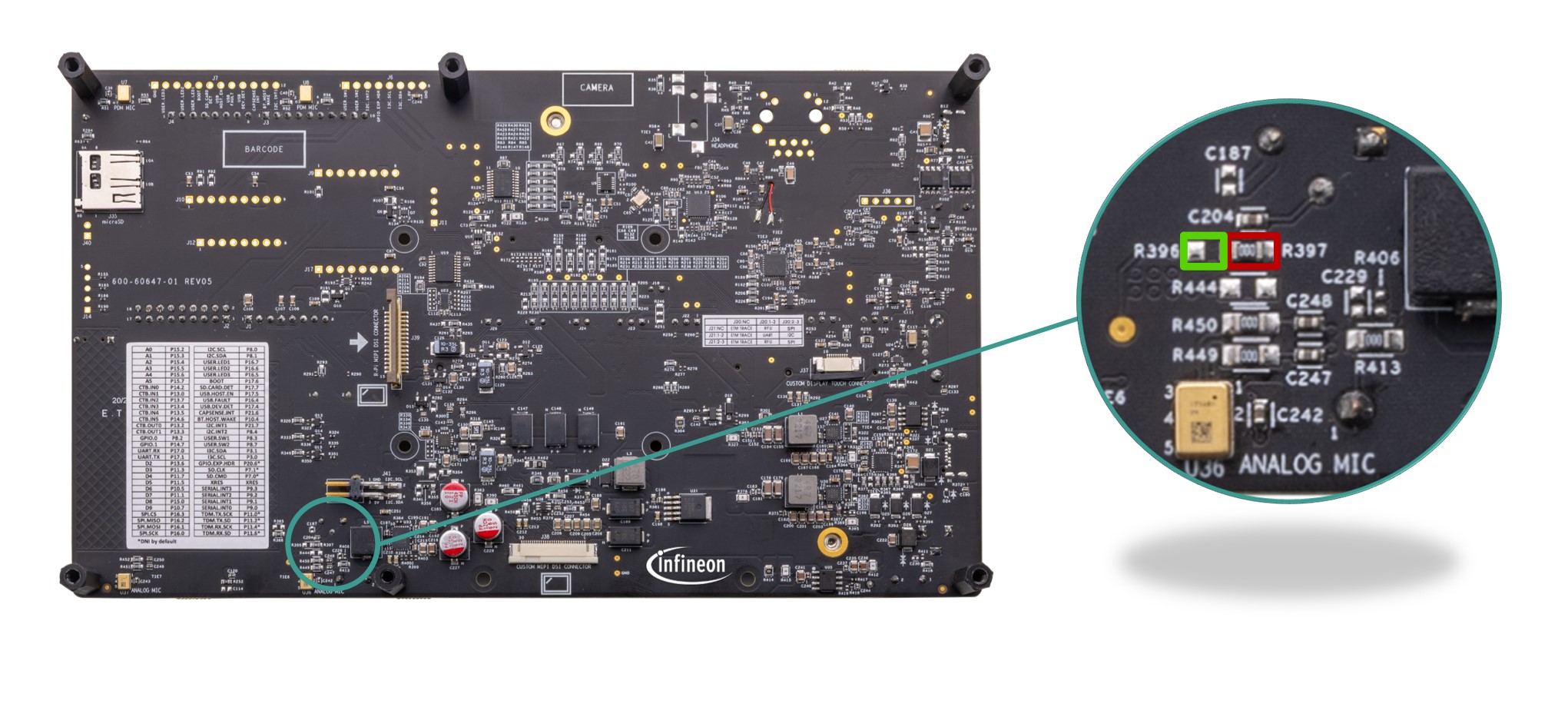

Analog microphones

Analog XENSIV™ MEMS microphones for EVK.

The PSOC™ Edge E84 EVK contains two analog XENSIV™ MEMS microphones (

U36

,

U37

) IM73A135V01XTSA1 from Infineon Technologies which are designed for high SNR (low self-noise) and low distortion (high AOP) applications.

U36

is the left channel microphone and

U37

being the right channel, placed ~42 mm apart from each other. Both microphones are supplied from 1.8 V (VDD_1V8) rail. The signal processing circuit for analog microphones is on PSOC™ Edge E84 SOM. Refer to section

AMIC signal processing circuit

for more details.

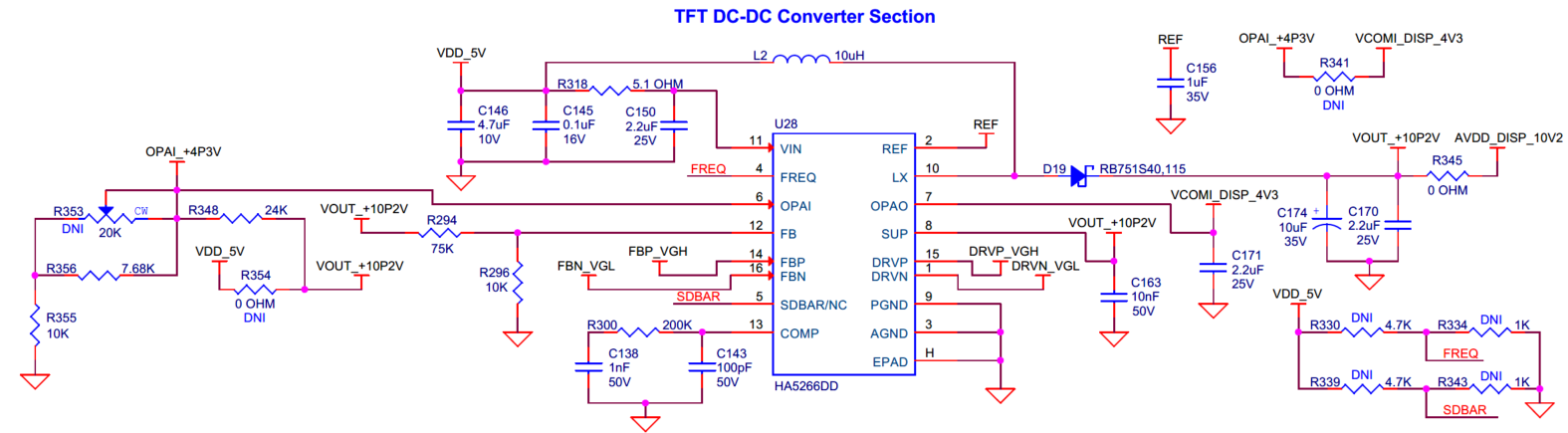

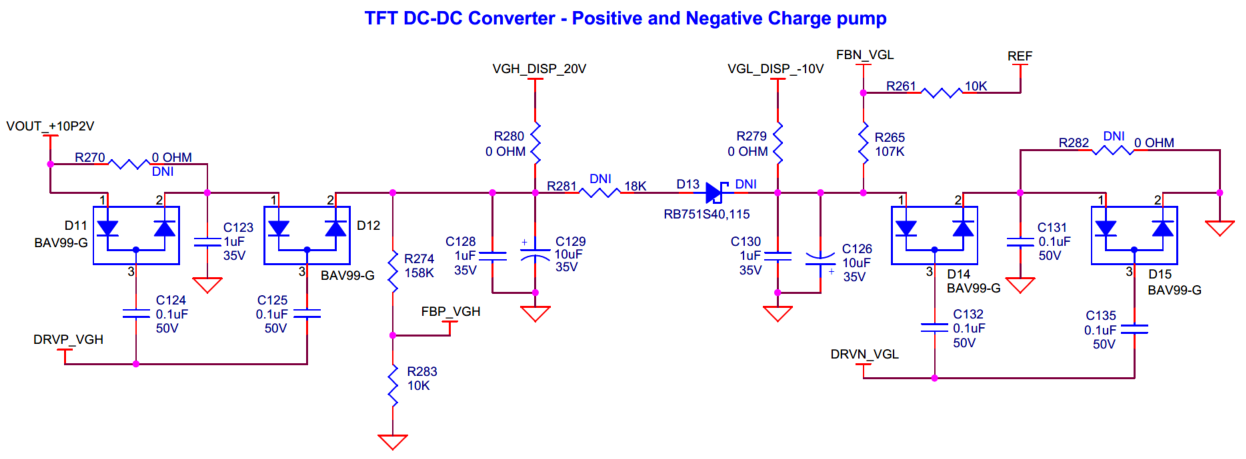

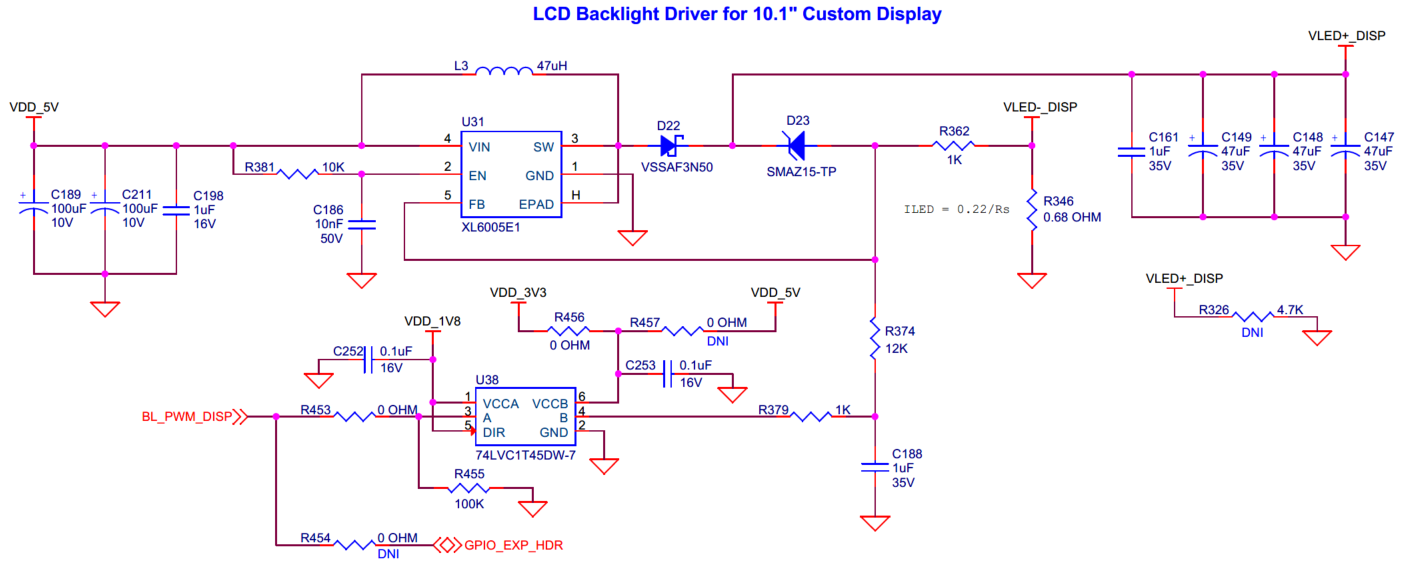

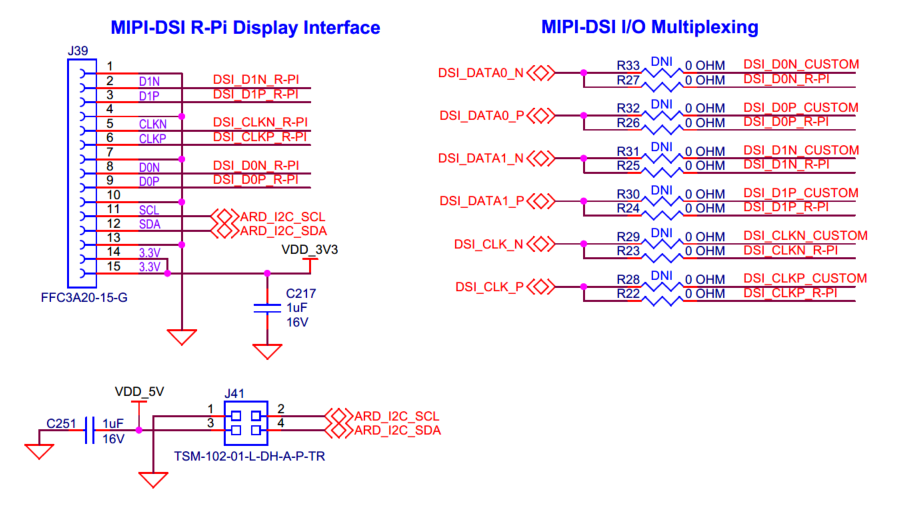

Signal name | PSOC™ Edge E84 I/O | Logic level |